AccessionIndex: TCD-SCSS-V.20160425.002 Accession Date: 25-Apr-2016 Accession By: Ken Gordon Object name: IBM Systems Reference Library - IBM System/360 Model 44 -Functional Characteristics Vintage: c.196x Synopsis: IBM.

# **Description:**

The System/360 Model 44 was a mainframe computer system manufactured by IBM, one of which was installed in 1969 in the Department of Computer Science in TCD, see the Hardware category of this catalog. The functional characteristics are thoroughly described in this document.

For the front and rear covers, title pages, table of contents, selected content, etc, see Figure 1 onwards below.

The homepage for this catalog is at: <u>https://www.scss.tcd.ie/SCSSTreasuresCatalog/</u> Click '*Accession Index*' (1st column listed) for related folder, or '*About*' for further guidance. Some of the items below may be more properly part of other categories of this catalog, but are listed here for convenience.

| Accession Index         | Object with Identification                                     |

|-------------------------|----------------------------------------------------------------|

| TCD-SCSS-V.20160425.002 | IBM Systems Reference Library - IBM System/360 Model 44        |

|                         | - Functional Characteristics, IBM, c.196x.                     |

| TCD-SCSS-V.20121208.258 | IBM Systems Reference Library - IBM System/360 Model 44        |

|                         | - Functional Characteristics, IBM, c.196x.                     |

| TCD-SCSS-T.20121208.018 | IBM 360/44 console and subsystems, Control panel, CPU          |

|                         | logic, core memory from IBM 360/44 installed in Trinity        |

|                         | College Dublin to provide a service to all sectors of College, |

|                         | including the Dept.Computer Science, from 1969, c.1969.        |

|                         |                                                                |

# **References:**

1. Wikipedia, IBM System/360 Model 44, see: <u>https://en.wikipedia.org/wiki/IBM\_System/360\_Model\_44</u> Last browsed to on 18-Jun-2016.

Figure 1: IBM 360/44 Functional Characteristics, folder opened on front page

1 1

File No. S360-01 Form A22-6875-6

# BM Syste

Systems Reference Library

# IBM System/360 Model 44

# **Functional Characteristics**

This manual describes the system structure, features, instruction timings and formulas, channels, device addressing, and operator controls unique to System/360 Model 44.

It is assumed the reader has a knowledge of the System/360 as defined in the IBM System/360 Principles of Operation, Form A22-6821 and the IBM System/360 System Summary, Form A22-6810.

tem/360 System Summary, Form A22-6521 and the IBM System/360 System Summary, Form A22-6510. For installations using the direct word, direct data channel, or priority interrupt features, a companion publication is Data Acquisition Special Features for the IBM System/360 Model 44, Form A22-6900. Other related literature is described in IBM System/360 Bibliography, Form A22-6822.

*Figure 2: IBM 360/44 Functional Characteristics, Page 1 (front cover)*

## SEVENTH EDITION

This is a major revision of, and obsoletes, A22-6875-5 and Technical News-letter N22-0275. The sections "Commercial Feature" and "Relationship of Model 44 to Other Models of IBM System/360" have been added. Other changes to the text are indicated by a vertical line to the left of the change; new and revised illustrations are denoted by the symbol • to the left of the caption.

Significant changes or additions to the specifications contained in this publica-tion are continually being made. When using this publication in connection with the operation of IBM equipment, check the latest SRL Newsletter for revisions or contact the local IBM branch office.

Requests for copies of IBM publications should be made to your IBM repre-sentative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B98, P.O. Box 390, Poughkeepsie, N.Y. 12602. A form is provided at the back of this publication for readers' comments. If the form has been removed, comments may be sent to the above address.

Figure 3: IBM 360/44 Functional Characteristics, Page 2

## Contents

|   | System Description                                 | 5  |

|---|----------------------------------------------------|----|

|   | Processing Unit                                    | -  |

|   | Timer                                              | 0  |

|   | Protection reature                                 | 0  |

| 1 | Commercial reature                                 | 10 |

|   | Standard Supporting Equipment                      | 13 |

|   | Console Printer-Keyboard                           | 10 |

|   | Single-Disk Storage Drive                          | 10 |

|   | Instructions                                       |    |

|   | Variable Long-Precision Floating Point             | 10 |

|   | Indexing Time                                      | 16 |

| 1 | Relationship of Model 44 to Other Models of IBM    |    |

|   | System/360                                         | 19 |

|   | Model-Dependent Functions                          | 10 |

|   | Machine Check Interruption                         | 10 |

|   | Normal Channel Operation                           | 10 |

|   | Instruction Execution                              | 10 |

|   | Timer Functions                                    | 20 |

|   | Channel Equipment Errors                           | 20 |

| 1 | System Controls                                    | 20 |

|   |                                                    |    |

|   | Instruction Timing Formulas                        | 21 |

|   | Group 1: Standard and Protection Timings with      | 21 |

|   | High-Speed General Registers                       | 21 |

|   | Group 2: Floating-Point Timings with High-Speed    | 21 |

|   | General Registers                                  | 23 |

|   | Group 3: Standard and Protection Timings without   | 20 |

|   | High-Speed General Registers                       | 26 |

|   | Group 4: Floating-Point Timings without High-Speed | 20 |

|   | General Registers                                  | 29 |

|   | Symbols Used in Timing Formulas                    | 31 |

|   | Basis of Average Timings                           |    |

| 1 | Commercial Feature Instruction Timings             |    |

|   |                                                    |    |

|   | Channels                                           | 35 |

|   | Channel Architecture                               | 38 |

|   | Channel Interference                               | 40 |

|   | Cross-Channel Interference                         |    |

|   | Cross-Channel Interference                         | UT |

System Control Panel System Control Functions

| System Reset                                         | 45 |

|------------------------------------------------------|----|

| Store and Display                                    |    |

| Initial Program Loading                              |    |

| Operator Control Section                             |    |

| Cartridge-Unlocked Lights (Disk)                     |    |

|                                                      |    |

| Emergency Pull Switch                                |    |

| Interrupt Key                                        |    |

| Load Key                                             |    |

| Load Light                                           |    |

| Load-Unit Switches                                   |    |

| Manual Light                                         |    |

| Power-Off Key                                        | 49 |

| Power-On Key                                         |    |

| Ready Lights (Disk)                                  | 49 |

| Start Keys (Disk)                                    | 49 |

| Stop Keys (Disk)                                     | 49 |

| System Light                                         | 49 |

| Test Light                                           |    |

| Wait Light                                           |    |

| Operator Intervention Controls                       |    |

| Address Switches                                     |    |

| Check Reset Key                                      |    |

| Data Switches                                        |    |

| Data Switches<br>Data Lights                         |    |

|                                                      |    |

| Display Key<br>Floating-Point Precision Switch       |    |

|                                                      |    |

| Instruction-Counter Lights                           |    |

| Lamp Test Switch                                     |    |

| MS Address Compare Switch                            |    |

|                                                      | 52 |

|                                                      | 52 |

|                                                      | 52 |

|                                                      | 53 |

| Stop Key (CPU)                                       |    |

| Storage Select Switch                                |    |

| Store Key                                            | 54 |

|                                                      | 54 |

| Commercial Feature Operating Controls and Procedures | 54 |

| Preparing the Model 44 for Emulation                 | 54 |

| Returning the Model 44 to Normal                     | 55 |

|                                                      |    |

| Index                                                | 56 |

| mucx                                                 | 00 |

Figure 4: IBM 360/44 Functional Characteristics, Page 3 (Table of Contents)

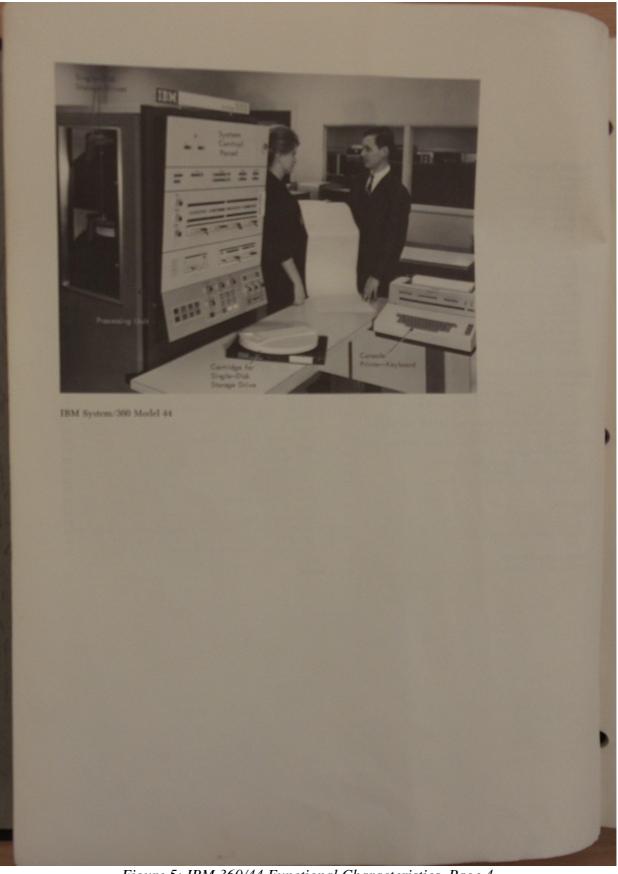

Figure 5: IBM 360/44 Functional Characteristics, Page 4

## **System Description**

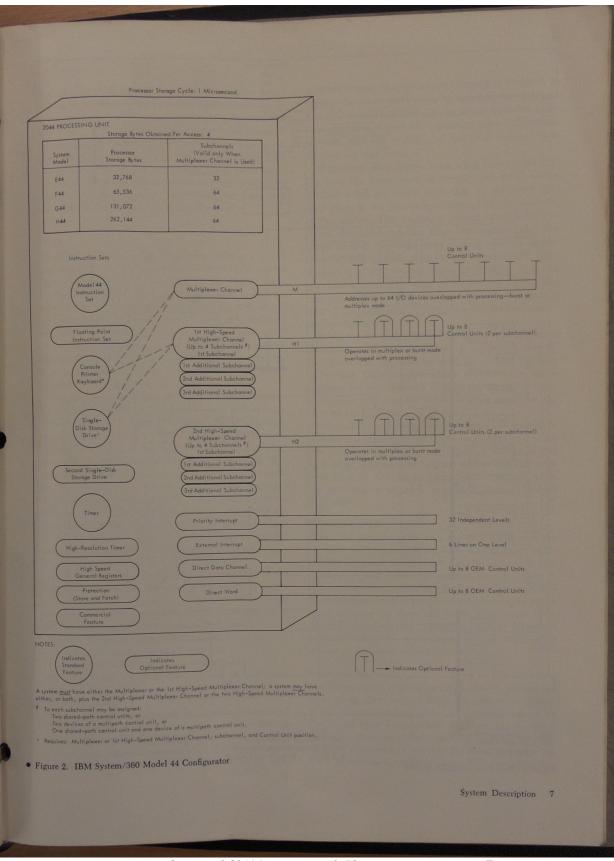

Model 44, a new member of the IBM System/360, is tailored to handle all relatively small to medium-sized scientific applications and advanced data acquisition and process control applications. Although the Model 44 is thus specialized, its inclusion within the context of System/360 philosophy provides for a very large addressing capability, a wide range of high-speed storage capacities, and 1/0 multiplexing on channels of low and high data-transfer rates.

The basic Model 44 is unilaterally compatible with System/360 Models 30 through 91. That is, a program written for the Model 44 can be executed on any of these other models if the compatibility constraints of System/360 are observed. However, programs that depend on special features available for only the Model 44 cannot be run on any other System/360 model. These features are: the selection of less than eight bytes for long-precision floating-point arithmetic (to be discussed) and three features (direct word, direct data channel, and priority interrupt) described in *Data Acquisition Special Features for the IBM System/360 Model 44*, Form A22-6900.

Model 44 was derived from standard System/360 architecture by including only those capabilities and instructions that are required for a binary and scientific model. The Model 44 therefore excludes 19 instructions that are normally included in the standard instruction set; those excluded are decimal arithmetic and other variable-field-length instructions.

One or more multiplexer channels, providing a choice of two data transfer rates, can be included in the Model 44 system. (Model 44 cannot be equipped with selector channels; however, a multiplexer channel in which one of its subchannels is operating in burst mode performs very similarly to a selector channel.)

Model 44 uses conventional high-speed sequential logic control instead of read-only storage.

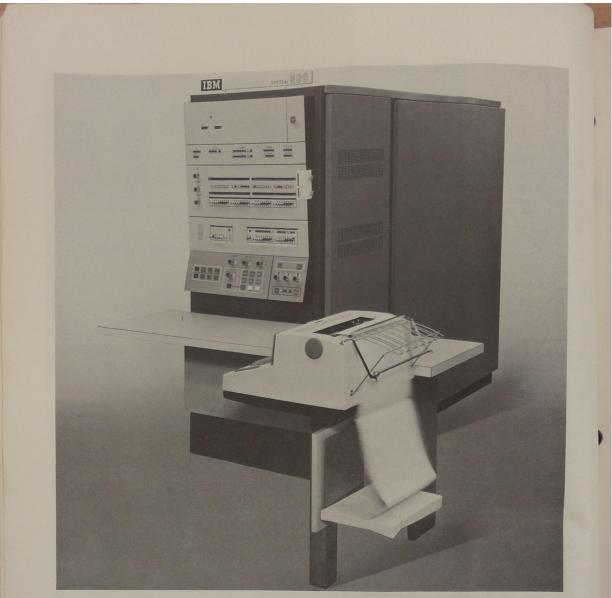

Although the Model 44 processing unit is about the same in physical size (Figure 1) as that of its nearest neighbor, the Model 50, its performance on problems for which it is optimized is 30 to 60 per cent faster than that of a Model 50. Performance figures depend much on the specific applications and optional equipment selected, namely: storage size, number and speed of channels, and quantity and speed of 1/0 devices supporting the CPU. The Model 44 processing unit contains, as standard equipment, a single-disk storage drive (capacity 1,171, 200 bytes) used for programming systems residence; the necessary disk storage adapter; and an adapter for the console printer-keyboard that is located on the processor table. A second single-disk storage drive, of equal capacity to the first, may be added within the processing unit as a special feature. (See Figure 2.)

All the  $\tau/o$  devices that can be attached to the Model 44 are listed, with channel and control-unit data, in Figure 9.

## **Processing Unit**

As in all other models of the System/360, the smallest addressable data unit is the byte, consisting of eight bits. A ninth bit, called the parity bit (not available to the program), is associated, for checking purposes, with each byte. Because of the optimization of Model 44 toward scientific work, however, the common units of data are the 32-bit binary word and the 16-bit binary halfword, composed of four and two bytes, respectively. Parity is checked upon each data fetch from processor storage and each transfer of data to or from channels.

Floating-point arithmetic uses the 32-bit word for short operands and a 64-bit double word for long operands. Model 44 introduces a new feature, variable long-precision floating-point arithmetic, in which different selections can be made for the length of the fraction when long operands are used. (See "Variable Long-Precision Floating Point.")

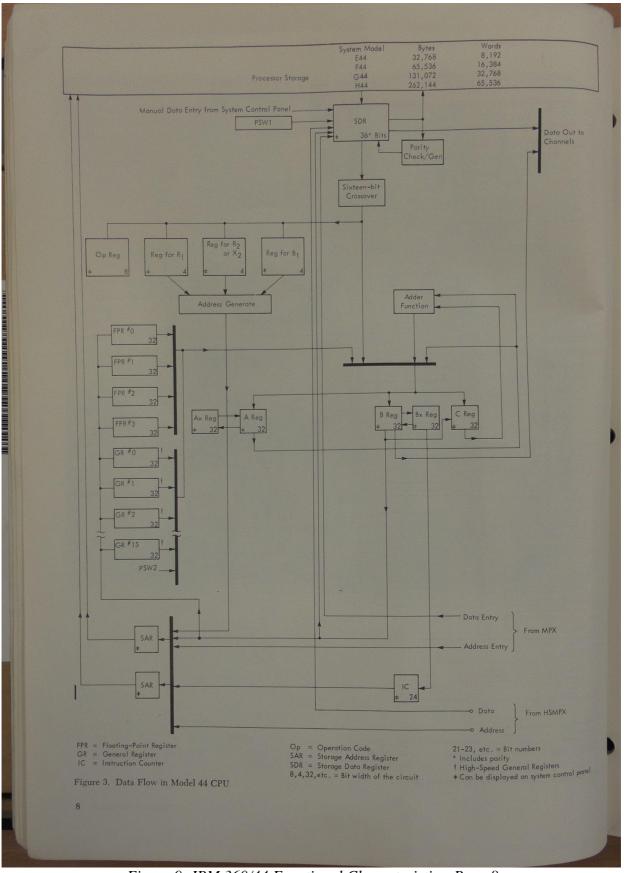

Processor storage speed for the Model 44 is 1 microsecond. Four bytes (one word or two halfwords) are stored or fetched in each access. Processor storage, always housed within the CPU, is available in the four capacities shown at the top of Figure 3.

Data paths throughout the CPU are one word wide. Because variable-length fields are not used in Model 44, bytes are handled in groups of two or four; however, they can be manipulated singly by the INSERT CHARACTER, STORE CHARACTER, TEST UNDER MASK, or the five immediate instructions:

COMPARE LOGICAL (CLI) EXCLUSIVE OR (XI) MOVE (MVI) OR (OI)

System Description 5

Figure 6: IBM 360/44 Functional Characteristics, Page 5

Figure 1. Processing Unit and Console Printer-Keyboard

The 16 general registers of the basic Model 44 are in a normally-unaddressable extension of the 1-microsecond processor storage. (This extension is often called "bump" storage or "core extension.") If the optional high-speed general registers feature (sometimes called "accelerator" feature) is installed, the 16 general registers are provided instead in solid logic technology (SLT) circuitry having 0.25 microsecond read/write time. This quartering of the access periods substantially reduces address generation time as well as the basic execution time of all fixed-point instructions in particular. (See Figures 3 and 7.)

6

Arithmetic and logical operations are performed between the A and B registers; the results are usually formed in the B register. The Bx register, coupled to the B register with left and right shifting ability, is used in multiply and divide operations and as an auxiliary address register.

If the floating-point feature is installed, the Ax register extends the A register to the 64-bit width needed for long-operand floating-point arithmetic. For long operands, the high-order halves of the floating-point registers are contained in sLT circuitry and the loworder halves are contained in the extension of processor

Figure 7: IBM 360/44 Functional Characteristics, Page 6

Figure 8: IBM 360/44 Functional Characteristics, Page 7

Figure 9: IBM 360/44 Functional Characteristics, Page 8

storage. For short operands, only the high-order (SLT) halves of the floating-point registers are used.

An optional feature provides six lines for external interrupts. The source of the external interrupts is identified by bits 26-31 of the interruption code in bit positions 16-31 of the old program status word (old rsw). These interrupts are independent of channel operations or of the direct-control feature required to provide external-interrupt capabilities for most System/360 models. Figure 14 shows the rsw.

### Timer

Model 44 has either a line-frequency timer as a standard capability or a high-resolution timer as a special feature. Either type can be used as an interval timer to measure elapsed time, or programmed to tell the time of day for program completions, etc. The standard timer is counted down every 1/60th or 1/50th of a second, and is fully described in *IBM System/360 Principles of Operation*, Form A22-6821. The specialfeature timer is mentioned therein also; for this, the least significant bit of the 32-bit timer word is decremented and the resolution is 13 microseconds.

The low-order eight bits of the high-resolution timer lie in an SLT-circuit counter rather than in core storage. The contents of the storage address register are monitored for any reference to byte 83, whether addressed directly, or as part of the halfword at 82, or as part of the fullword at 80. When any such reference to 83 is detected, a substitution occurs that causes the contents of the eight-bit counter to participate in the operation in place of the storage byte 83. This eight-bit counter includes the decrementing and parity-generating circuits and acts for all purposes as the low-order byte of the timer word. Byte 83 in the storage array becomes unaddressable either by CPU instructions or by channels, and its bits cannot be displayed.

A 76.8-KC oscillator causes the low-order bit of the counter to be decremented at approximately 13-microsecond intervals. Decrementing the counter does not interfere with CPU processing. The decrementing is prevented by any of the following conditions:

1. The initial program is being loaded

2. The CPU is in the stopped state

3. The rate switch is set to INSN STEP

4. The disable interval timer switch is turned on. This switch is for the use of customer engineering (CE) personnel

Every 1/300th of a second the counter becomes all l's, and bit 23 is updated whenever access to storage permits. Specifically, when the counter becomes all l's, a timer step trigger turns on (while the decrementing continues); if the timer step trigger is on at endoperation time, instruction sequencing is stopped to permit the timer word to be updated by the subtraction of 1 from bit position 23, at which time the timer step trigger is turned off. Updating takes 1.75 microseconds, and the fetching of the next instruction is delayed for that time.

If the timer step trigger is on when the CPU is fetching from the timer word in storage, bits 24-31 of the fetched word are made zero; that is, the fetch gets only zeros in the fourth byte instead of the contents of the counter. This ensures a correct relationship between the value fetched from the counter and the value fetched from the main storage portion of the timer at this instant; the counter is prevented from appearing as all 1's when timer bit position 23 is not yet decremented. The value of the fetched timer word may appear to be off by no more than the execution time of the instruction (after allowing for cycle-stealing by channels).

If, during the course of an instruction that addresses the timer word, an interruption is requested, this interruption may be delayed until the end of the next instruction. Only machine-check and program interruptions are not delayed. If only the standard timer is installed, however, the delay does not occur for any class of interruption.

When decrementing causes the entire timer word to pass from a positive value (including zero) to a negative value, a standard timer interrupt occurs in the form of an external interruption request. The full cycle time, from all 1's in bit positions 0-23 to the time when the interruption signal is generated, is the standard 15.5 hours.

## **Programming Note**

When the timer is used as a real-time clock and the CPU is to be instructed to read the current timer value and set the clock to some other value, successive fullword LOAD and STORE instructions must be used to simulate the MVC move which is absent from the Model 44 instruction set. It is possible for a timer updating to occur between the LOAD and STORE instructions; thus, the real-time clock may "creep" forward by 13 microseconds, and in the worst case this creep takes place whenever the clock value is changed.

### **Protection Feature**

The protection feature makes it possible to protect the contents of main storage from destruction or misuse. When the protection is added, as a special feature, to the Model 44, it includes both the store and the fetch protection features defined in *IBM System/360 Principles of Operation*, Form A22-6821. Neither store nor fetch protection is available alone. The protection key

System Description 9

Figure 10: IBM 360/44 Functional Characteristics, Page 9

in storage can be changed by the SET STORAGE KEY instruction and inspected by the INSERT STORAGE KEY instruction. Note that these two instructions are added to the Model 44 instruction set only when the protection feature is installed. The instruction timings are included in Figure 7.

In the INSERT STORAGE KEY instruction, bit 28 of the register designated by the first operand is the fetch protection bit and is set to one for both store and fetch protection or to zero for store protection only.

It is possible for the Model 44 to access in one cycle a storage word that straddles a 2,048-byte protection boundary. This can happen only in instruction fetching, at which time a fetch protection violation may cause the instruction to be suppressed, However, Model 44 has time to fetch and compare both storage keys during the one main storage access with no increase in the instruction time.

# • Commercial Feature

The System/360 Model 44 is custom-designed for small to medium-size scientific applications and advanced data acquisition and process control applications. The basic instruction set of the Model 44 consequently does not include all the System/360 instructions. To provide Model 44 compatibility with the System/360, the commercial feature adds five of the System/360 standard instructions to the Model 44

Figure 11: IBM 360/44 Functional Characteristics Page 10

capability and enables the Model 44 to execute by emulation 22 System/360 instructions that are not normally a part of the Model 44 basic instruction set.

The commercial feature provides the circuitry and emulator program required to execute 19 instructions of the System/360's standard set and eight instructions of System/360's decimal set. This feature also provides the capability to operate the high-speed multiplexer channels in selector mode, assuming the direct data channel feature is not installed.

The operating controls are described under "Commercial Feature Operating Controls and Procedures." Representative commercial feature instruction timings are shown in Figure 10.

### Restrictions

Restrictions on the commercial feature are:

1. The feature is available only for Models F44, G, and H.

2. Model F44 is limited to 32 subchannels.

3. Programs that are run under emulation cannot be time-dependent.

4. The Model 44 configuration must meet the requirements of the operating system in use.

5. If emulation of selector channel operation is required, the Model 44 configuration must include a high-speed multiplexer channel and cannot include the direct data channel feature.

6. Only valid System/360 op codes are emulated. RPQ or special op codes are not included.

7. Throughput is at a degraded rate and varies with the instruction mix.

8. The emulator disable switch does not disable the five standard System/360 instructions (EX, LM, STM, BXH, and BXLE) that are implemented by circuitry.

9. The single-disk storage drive operates with a multiplexer channel. If the drive is used in emulation, it must be connected to a low-speed multiplexer channel; if it is connected to a high-speed multiplexer channel, the selector mode switch must not be on.

## Theory of Operation

To emulate an instruction, Model 44 instructions are executed to produce the result that would have been produced by executing the original System/360 instruction. A machine language subroutine for each of the 22 instructions to be emulated exists in an extension of main storage. Whenever one of the 22 specified operation codes (shown in the following list) is decoded during an instruction fetch cycle, the appropriate subroutine is substituted to produce the desired result. In effect, all System/360 instructions of the commercial instruction set become valid when the commercial feature is installed.

| RMAT | CODE | MNEMONIC | NAME                         |

|------|------|----------|------------------------------|

| BX   | 44   | °EX      | Execute                      |

|      | 4E   | CVD      | Convert to decimal           |

|      | 4F   | CVB      | Convert to binary            |

| RS   | 86   | °BXH     | Branch on index high         |

|      | 87   | •BXLE    | Branch on index low or equal |

|      | 90   | *STM     | Store multiple               |

|      | 98   | °LM      | Load multiple                |

| SS   | D1   | MVN      | Move numerics                |

|      | D2   | MVC      | Move characters              |

|      | D3   | MVZ      | Move zones                   |

|      | D4   | NC       | AND characters               |

|      | D5   | CLC      | Compare logical characters   |

|      | D6   | OC       | OR characters                |

|      | D7   | XC       | Exclusive OR characters      |

|      | DC   | TR       | Translate                    |

|      | DD   | TRT      | Translate and test           |

|      | DE   | ED       | Edit                         |

|      | DF   | EDMK     | Edit and Mark                |

|      | F1   | MVO      | Move with offset             |

|      | F2   | PACK     | Pack                         |

|      | F3   | UNPK     | Unpack                       |

|      | F8   | ZAP      | Zero and add                 |

|      | F9   | CP       | Compare decimal              |

|      | FA   | AP       | Add decimal                  |

|      | FB   | SP       | Subtract decimal             |

|      | FC   | MP       | Multiply decimal             |

|      | FD   | DP       | Divide decimal               |

|      |      |          |                              |

NOTE: Op codes not listed cause a 01 program interruption in main storage.

\*Instructions implemented in circuitry.

#### Implementation

The implementation of instruction emulation requires additional core storage as residence for the emulator program. The additional storage, called storage extension, although it is an extension of main storage, is not addressable by the user programs.

Three operator switches (see "Operator Control Section") located on the console, provide control over initial program loading of the emulator program, conversion of the high-speed multiplexer channels to selector channels, and enabling of the emulate mode.

Circuitry, in conjunction with the operator controls, does the following:

1. Forces burst mode on all high-speed multiplexer channels, causing them to emulate selector channels, when the selector mode switch is on.

2. Causes all 1/0 channels to reference only storage extension addresses during an emulator initial program load (IPL).

3. Allows a system reset to set the Model 44 in the emulate mode when the emulator disable switch is set to normal.

4. Recognizes invalid operation codes during instruction fetch cycles in emulate mode.

5. Causes a program interruption that takes its new program status word (psw) from the corresponding storage extension location, when an invalid op code is detected.

6. Causes the stop key to be inactive during in-

System Description 11

## Figure 12: IBM 360/44 Functional Characteristics, Page 11

struction emulation, that is, the CPU stops only after emulation is complete.

7. Causes instruction fetching from storage extension instead of main storage during emulation.

8. Examines bit 8 of load PSW and supervisor call (svc) instructions. The special use of bit 8 in these instructions in emulate mode is explained later in this section.

With the emulator disable switch set to normal, and the emulator program loaded into storage extension, the CPU is ready to execute all of the commercial instructions used by the System/360. During normal program execution, each instruction fetched is decoded. When the decoded op code is invalid for the Model 44 (is not implemented in circuitry), a 01 program interrupt is signaled, emulate mode is set on, and a program interrupt is taken in storage extension. The program old PSW is stored in storage extension address 28(hex) and the program new PSW is taken from 68(hex). The new PSW places the CPU in the supervisor state disabled to all interrupts. The 16 general registers (GR) are stored, freeing them for use by the emulator program. The instruction address in the old PSW is used to examine the instruction causing entrance to the emulator. If it is System/360 invalid, or an execute exception, the old PSW in extension storage is moved to the program old PSW area in main storage location 28(hex). The program new PSW from main storage location 68(hex) is then loaded and emulation mode is turned off. This procedure simulates a code 01 program interruption to the problem program.

If the instruction causing entrance to the emulator is System/360 valid, the appropriate subroutine of the emulator is executed to simulate the decoded instruction.

Satisfactory completion of the emulation subroutine is followed by a load psw instruction with bit 8 of the instruction set to 1. This instruction resets the emulate mode and loads the modified old PSW from the storage extension location 20(hex) to become the current psw in resumption of the main program. Note that the load psw instruction, with bit 8 set to 1, serves the additional function of resetting the emulate mode. Similarly, bit 8 of the supervisor call (svc) instruction serves a special function. Because the emulator always operates in the supervisor state, the svc instruction is redundant; therefore, svc interrupts are inhibited in the emulate mode. The svc instruction is utilized instead to allow or disallow main storage accesses in the emulate mode. Bit 8 set to 1 in a decoded svc enables main storage accesses for operands (not for instructions); bit 8 set to 0 resets the function to allow only storage extension accesses.

In emulate mode, svc interrupts are inhibited;  $m_{a.}$  chine check, external, and 1/0 interrupts are held pending until emulation is complete; and program interrupts are handled according to the type.

To prevent overwriting the old rsw in storage  $e_x$ . tension that records the exit point of the problem program, any program interruptions taken while in emulate mode result in the new rsw being taken from location 78(hex) and the old rsw being stored in location 38(hex).

As noted in *IBM System/360 Principles of Opera*tion, Form A22-6821, when the timer is to be used as a real-time clock, the move instruction (MVC) may be used to read the current timer value and to set a new timer value without danger of timer updating occurring between the two operations. Because the Model 44 has no MVC instruction, successive load and store instructions must be used, and nothing can prevent a "creep" in the real-time clock. The "creep" could amount to 13 microseconds each time the timer value is changed.

Although the MVC instruction is emulated with the commercial feature, load and store instructions should still be used, because updating of the timer can occur between the machine instructions that move individual bytes.

Instructions related to System/360 RPQ's or special features, such as the direct control feature, are not emulated. No attempt is made to inhibit Model 44 special feature instructions, such as write direct word or read direct word; these instructions are executed when the feature is present, although they are categorized as System/360 invalid.

#### **Storage Extension Allocations**

Figure 5 shows the storage extension locations used during normal operation of the CPU, depending on the model number and the corresponding size of main storage.

## Storage Address Assignments in Storage Extension

|   |      | and the second |               |

|---|------|------------------------------------------------------------------------------------------------------------------|---------------|

|   |      | ADDRESS                                                                                                          | ASSIGNMENT    |

| ( | DEC) | ( HEX )                                                                                                          |               |

|   | 0    | 0                                                                                                                | IPL PSW       |

|   | 8    | 8                                                                                                                | IPL CCW 1     |

|   | 16   | 10                                                                                                               | IPL CCW 2     |

|   | 24   | 18                                                                                                               | External OPSW |

|   | 32   | 20                                                                                                               | SVC OPSW      |

|   | 40   | 28                                                                                                               | Program OPSW  |

|   | 48   | 30                                                                                                               | Machine OPSW  |

|   | 56   | 38                                                                                                               | I/O OPSW      |

|   | 64   | 40                                                                                                               | CSW           |

|   | 72   | 48                                                                                                               | CAW           |

|   | 76   | 4C                                                                                                               | Unassigned    |

|   | 80   | 50                                                                                                               | Timer         |

|   | 84   | 54                                                                                                               | Unassigned    |

|   | 88   | 58                                                                                                               | External NPSW |

|   | 96   | 60                                                                                                               | SVC NPSW      |

|   |      |                                                                                                                  |               |

Figure 13: IBM 360/44 Functional Characteristics, Page 12

| Storage Exte   | nsion Location    | and the second second |                   |                  |  |

|----------------|-------------------|-----------------------|-------------------|------------------|--|

| Hexadecimal    | Decimal           | Model F               | Model G           | Model H          |  |

| 0 - 11F        | 0 - 287           | Reserved              | Reserved          | Reserved         |  |

| 120 - 7FF      | 288 - 2047        | 1,760 Bytes           | 1,760 Bytes       | 1,760 Bytes      |  |

| 8,000 - 83FF   | 32,768 - 33,791   | 1,024 Bytes           | 1,700 Byies       | .,,              |  |

| 8,400 - 87FF   | 33,792 - 34,815   | 64 Multiplex UCWs     | 2,048 Bytes       | 2,048 Bytes      |  |

| 10,000 - 107FF | 65,536 - 67,583   | and pick octivs       | 2,048 Bytes       | 2,048 Bytes      |  |

| 18,000 - 183FF | 98,304 - 99,427   | Chan Degle State      | 1,024 Bytes       | 2,040 bytes      |  |

| 18,400 - 187FF | 99,428 - 101,351  |                       | 64 Multiplex UCWs | 2,048 Bytes      |  |

| 20,000 - 207FF | 131,072 - 133,119 |                       | of moniplex octis | 2,048 Bytes      |  |

| 28,000 - 287FF | 163,840 - 165,887 | Not Available         |                   | 2,048 Bytes      |  |

| 30,000 - 307FF | 196,608 - 198,655 |                       | Not Available     | 2,048 Bytes      |  |

| 38,000 - 383FF | 229,376 - 230,399 |                       |                   | 1,024 Bytes      |  |

| 38,400 - 387FF | 230,400 - 231,423 |                       |                   | 64 Multiplex MCW |  |

• Figure 5. Storage Extension Allocations

| ADDRES           | S            | ASSIGNMENT         |

|------------------|--------------|--------------------|

| ( DEC )          | (HEX)        |                    |

| 104              | 68           | Program NPSW       |

| 112              | 70           | Machine NPSW       |

| 120              | 78           | I/O NPSW           |

| 128              | 80           | GR0                |

| 132              | 84           | GR1                |

| 136              | 88           | GR2                |

| 140              | 8C           | GR3                |

| 144              | 90           | CR4                |

| 148              | 94           | GR5                |

| 152              | 98           | GR6                |

| 156              | 9 <b>C</b>   | GR7                |

| 160              | A0           | GR8                |

| 164              | A4           | GR9                |

| 168              | A8           | GR10               |

| 172              | AC           | GR11               |

| 176              | BO           | GR12               |

| 180              | B4           | GR13               |

| 184              | B8           | GR14               |

| 188              | BC           | GR15               |

| 192-255          | CO-FF        | 64 Bytes           |

| 256              | 100          | FR0                |

| 260              | 104          |                    |

| 264              | 108          | FR2                |

| 268              | 10C          | 504                |

| 272              | 110          | FR4                |

| 276              | 114          | 5320               |

| 280              | 118          | FR6                |

| 284              | 11C          | 1.760 Bytes        |

| 288 to 2047      | 120 to 7FF   | 1,700 Dytes        |

| 2048 to 32,767   | 800 to 7FFF  | 1,024 Bytes        |

| 32,768 to 33,791 | 8000 to 83FF | MPX UCW            |

| 33,792           | 8400         | MIN CON            |

| 33,804           | 840C         | MPX UCW            |

| 33,808           | 8410         | MILLA COLU         |

| 33,812           | 841C         | MPX UCW            |

| 33,824 to 34,800 | 8420 to 87F0 | TAX                |

| 34,812           | 87FC         |                    |

| 34,816 to 65,535 | 8800 to FFFF | Invalid on Model F |

| 65,536           | 10000        | Invalid on Model G |

| 131,072          | 20000        |                    |

|                  |              |                    |

## Standard Supporting Equipment

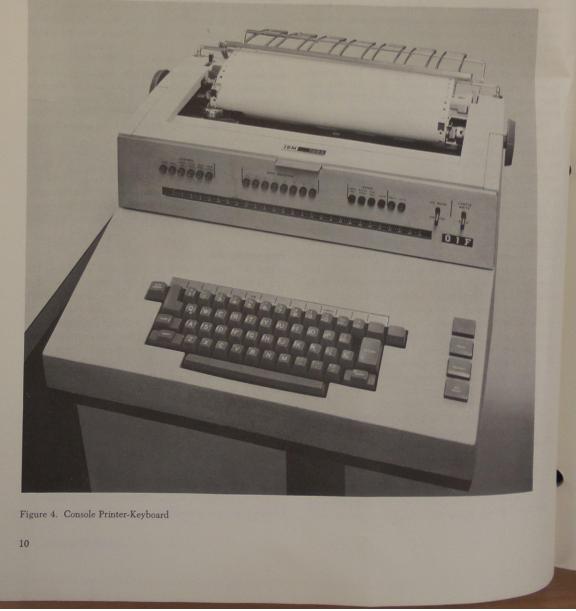

## **Console Printer-Keyboard**

The console printer-keyboard (Figure 4) permits communication between the operator and the system. Facilities are provided for interrupting the processing unit and for signalling the end of a data transmission.

The printer-keyboard has a stationary carriage and a replaceable, interchangeable printing sphere. Its typewriter-style keyboard and the printing function can be used independently: the keyboard for system input and the printer for computer output. The font of each printing sphere is specified by the customer.

The functions and operations of the console printerkeyboard are the same as those described for the IBM 1052 Printer-Keyboard Model 7 in IBM System/360 System Summary, Form A22-6810. Operating procedures and details are the same as those in IBM 1052 Printer-Keyboard Model 7 with IBM 2150 Console, Form A22-6877.

The console printer-keyboard is attached to one of the system channels via an adapter which is physically located within the CPU as a standard feature. The installation of the console printer-keyboard is also standard and takes up either one control-unit position and one subchannel of a multiplexer channel or one control-unit position and half a subchannel on a highspeed multiplexer channel.

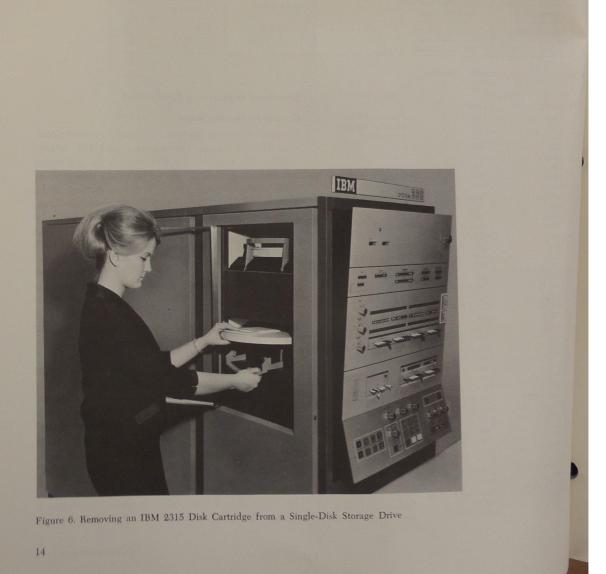

## Single-Disk Storage Drive

The single-disk storage drive provides direct access auxiliary storage for a minimum of 1,171,200 bytes on

System Description 13

Figure 14: IBM 360/44 Functional Characteristics, Page 13

a single disk permanently enclosed in an IBM 2315 Disk Cartridge and housed within the CPU, with side access for replacement of cartridges (Figure 6.) Each cartridge must be purchased separately, but the drive is a standard feature of Model 44.

The data rate of the disk storage is 90,000 bytes per second, necessitating operation in burst mode. Average time to seek a track is 70 milliseconds; the subsequent rotational delay to a particular record ranges from 0 to 40 milliseconds and averages 20 milliseconds.

Information is written on or read from the disk by a pair of magnetic read/write heads, one head for each

surface. The disk is organized in 200 cylinders and three spare cylinders; a cylinder consists of a pair of tracks, one track per disk surface. Each cylinder contains 16 sectors (eight per track and surface). Each sector has a fixed length of 366 bytes. The three spare cylinders ensure that the stated capacities are maintained for the life of the cartridge. The read/write heads move, under a single seek. command, directly to the track addressed. Error detection is accomplished on reading data from the disk.

No programming compatibility exists between the single-disk storage drive and disk storage drives controlled through the IBM 2841 Storage Control.

Figure 15: IBM 360/44 Functional Characteristics, Page 14

The drive is attached to one of the system channels only via an adapter, which is also installed in the CPU as a standard feature. A second drive may be installed in the CPU, as a special feature, to double the storage capacity. The two drives use the same shared-path adapter and operate on one shared subchannel, requiring one control-unit position on either a multiplexer or a high-speed multiplexer channel. Seek overlap is permissible when both drives are installed.

## Commands

Control Seek — 00001011: One byte is transferred to the adapter. The byte contains the required cylinder address (0 through 202). The channel is free after the transfer of this byte, and the drive is free at the end of the seek.

Read Data — HSSS1010: Reading begins with the head for track H, sector SSS, and continues to the end of the track. If SSS=0, the entire track of 2,928 bytes is read. If the ccw count goes to zero at the end of sector 7 (end of track) or before the end of any other sector, the drive is free at the end of the sector being read. If the ccw count goes to zero at the last byte of a sector 0-6, however, the device end is delayed until the end of the following sector.

Write Data - HSSS1001: Writing begins at track H, sector SSS, and continues to the end of the track. If the ccw count goes to zero before the end of the track, the remainder of the sector being written is filled with zeros by the adapter and the drive is then free.

Other Commands: The adapter also recognizes read IPL (00000010), control no-op (00000011), and sense commands (00000100).

### **Programming Notes**

The formal record length of the single-disk storage drive is 2,928 bytes (one full track); for all correct but shorter records, "incorrect length" is a normal indication. The ccw for a read or write command must therefore contain the SLI flag (suppress-length-indication, bit 34) unless the operation is to end with the 366th byte of the eighth sector.

Command chaining to the next sector may take place at a sector boundary without rotational delay unless a read operation ends with the 366th byte of sectors 0-6.

### Keys and Lights

All keys and lights for the proper operation of each drive are on the lower left portion of the system control panel and are described under "Operator Control Section."

## Instructions

The Model 44 executes the following instructions:

|                            |        | MNEN   | IONICS |       |

|----------------------------|--------|--------|--------|-------|

|                            | RR     | RX     | RS     | SI    |

| INSTRUCTION                | FORMAT | FORMAT | FORMAT | FORMA |

| Add                        | AR     | А      |        |       |

| Add Halfword               |        | AH     |        |       |

| Add Logical                | ALR    | AL     |        |       |

| AND                        | NR     | N      |        | NI    |

| Branch and Link            | BALR   | BAL    |        |       |

| Branch on Condition        | BCR    | BC     |        |       |

| Branch on Count            | BCTR   | BCT    |        |       |

| Compare                    | CR     | С      |        |       |

| Compare Halfword           |        | CH     |        |       |

| Compare Logical            | CLR    | CL     |        | CLI   |

| Divide                     | DR     | D      |        |       |

| Exclusive OR               | XR     | X      |        | XI    |

| Halt I/O                   |        |        |        | HIO   |

| Insert Character           |        | IC     |        |       |

| Load                       | LR     | L      |        |       |

| Load Address               |        | LA     |        |       |

| Load and Test              | LTR    |        |        |       |

| Load Complement            | LCR    |        |        |       |

| Load Halfword              |        | LH     |        |       |

| Load Negative              | LNR    |        |        |       |

| Load Positive              | LPR    |        |        |       |

| Load PSW                   |        |        |        | LPSW  |

| Move                       |        |        |        | MVI   |

| Multiply                   | MR     | М      |        |       |

| Multiply Halfword          |        | MH     |        |       |

| OR                         | OR     | 0      |        | OI    |

| Set Program Mask           | SPM    |        |        |       |

| Set System Mask            |        |        |        | SSM   |

| Shift Left Double          |        |        | SLDA   |       |

| Shift Left Double Logical  |        |        | SLDL   |       |

| Shift Left Single          |        |        | SLA    |       |

| Shift Left Single Logical  |        |        | SLL    |       |

| Shift Right Double         |        |        | SRDA   |       |

| Shift Right Double Logical |        |        | SRDL   |       |

| Shift Right Single         |        |        | SRA    |       |

| Shift Right Single Logical |        |        | SRL    |       |

| Start I/O                  |        |        |        | SIO   |

| Store                      |        | ST     |        |       |

| Store Character            |        | STC    |        |       |

| Store Halfword             |        | STH    |        |       |

| Subtract                   | SR     | S      |        |       |

| Subtract Halfword          |        | SH     |        |       |

| Subtract Logical           | SLR    | SL     |        |       |

| Supervisor Call            | SVC    |        |        |       |

| Test and Set               |        |        |        | TS    |

| Test Channel               |        |        |        | TCH   |

| Test I/O                   |        |        |        | TIO   |

| Test Under Mask            |        |        |        | TM    |

An optional feature provides the full complement of floating-point instructions for both long and short operands and the RR and RX formats:

|                  | MNEMONICS |           |      |       |

|------------------|-----------|-----------|------|-------|

|                  | RR F      | RR FORMAT |      | ORMAT |

| INSTRUCTION      | LONG      | SHORT     | LONG | SHORT |

| Add Normalized   | ADR       | AER       | AD   | AE    |

| Add Unnormalized | AWR       | AUR       | AW   | AU    |

| Compare          | CDR       | CER       | CD   | CE    |

| Divide           | DDR       | DER       | DD   | DE    |

| Halve            | HDR       | HER       |      |       |

| Load             | LDR       | LER       | LD   | LE    |

| Load and Test    | LTDR      | LTER      |      |       |

| Load Complement  | LCDR      | LCER      |      |       |

| Load Negative    | LNDR      | LNER      |      |       |

System Description 15

Figure 16: IBM 360/44 Functional Characteristics, Page 15

|                       | MNEMONICS |        |        |        |

|-----------------------|-----------|--------|--------|--------|

|                       | RR        | RX     | RS     | SI     |

| INSTRUCTION           | FORMAT    | FORMAT | FORMAT | FORMAT |

| Load Positive         | LPDR      | LPER   |        |        |

| Multiply              | MDR       | MER    | MD     | ME     |

| Store                 |           |        | STD    | STE    |

| Subtract Normalized   | SDR       | SER    | SD     | SE     |

| Subtract Unnormalized | SWR       | SUR    | SW     | SU     |

As already described under "Protection Feature," two more instructions are added when that special feature is installed:

| INSTRUCTION        | FORMAT | MNEMONICS |

|--------------------|--------|-----------|

| Set Storage Key    | RR     | SSK       |

| Insert Storage Key | RR     | ISK       |

A full description of each instruction (except for execution time) is in the *IBM System/360 Principles* of Operation, Form A22-6821. Full timing formulas, and bases for determining the average times given in Figures 8 and 9, are described in this manual under "Instruction Timing Formulas."

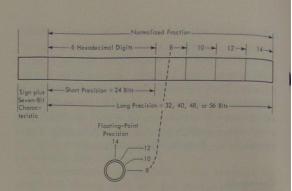

## **Variable Long-Precision Floating Point**

Some floating-point problems need more than short precision but do not require the 56 bits of long precision. With the variable long-precision floating-point feature, the user can adjust long-precision instructions for execution with 32, 40, 48, or the full 56 bits of precision. The adjustment for variable long-precision floating point is made at program execution time by setting a rotary switch on the system control panel to one of four positions (Figure 7). Only the floatingpoint long-precision multiply and divide operations are affected by the setting of the switch.

| SWITCH SETTING      | LONG PRECISION   |

|---------------------|------------------|

| NO. OF HEXADECIMAL  | (FRACTION LENGTH |

| DIGITS IN FRACTION) | IN BITS )        |

| 14                  | 56               |

| 12                  | 48               |

| 10                  | 40               |

| 8                   | 32               |

For maximum speed, the switch is set to 8; for maximum precision, it is set to 14. Setting the switch to 14 maintains complete compatibility with other System/360 models using long-precision floating point. At settings 8, 10, or 12, the operands of the long multiply instructions are pre-normalized and then truncated, as shown in Figure 7. A full 56-bit product is developed from these operands. The product is identi-

Figure 7. Variation of Fraction Length in Long Precision

cal to that which would be obtained at 14-digit precision, using the operands after truncation. At settings 8, 10, or 12, the normalized quotient fraction of the long divide instruction is truncated (see Figure 7). At settings 10 or 12, the full operand fractions participate in the divide, and consequently, those digits of the quotient which are not truncated are identical to the corresponding digits of the quotient (which would be obtained by using 14-digit precision). At 8-digit precision however, the divisor is truncated to 8 digits (after pre-normalization) as well as the quotient.

## **Indexing Time**

All Model 44 instruction timings (Figures 8 and 9) include the 1-microsecond I time and, for instructions that reference storage, the time to perform single indexing by one general register as referenced in the instruction (i.e.,  $B \neq 0$ ).

For instructions in which double indexing is possible (i.e., all RX format instructions) the time required for the second indexing is 1 microsecond on the basic Model 44, or 0.75 microsecond when the high-speed general registers feature is installed. The times shown for the eight shift instructions assume no indexing (i.e., B=0). For special timing calculations, the following adjustments may be made:

|                                                 | BASIC<br>MODEL 44 | WITH HIGH-SPEED<br>GENERAL REGISTERS |

|-------------------------------------------------|-------------------|--------------------------------------|

| INSTRUCTION FETCH<br>(included in all timings): | 1.00              | 1.00                                 |

| FIRST INDEXING<br>(excluded for shift instruct  | ions): 1.00       | 0.25                                 |

| SECOND INDEXING<br>(excluded from all timings   | ): 1.00           | 0.75                                 |

Figure 17: IBM 360/44 Functional Characteristics, Page 16

| Instruction                                    | Format           | Mnemonic                 | В                  | asic Model 44                          |             | ith High-Speed<br>fisters Feature      |

|------------------------------------------------|------------------|--------------------------|--------------------|----------------------------------------|-------------|----------------------------------------|

| dd                                             | RR               | AR                       |                    |                                        | General Reg | 1.75                                   |

| dd                                             | RX               | A                        |                    | 3.75<br>4.75                           |             | 2.25                                   |

| dd Halfword<br>dd Logical                      | RX<br>RR         | AH<br>ALR                |                    | 4.75                                   |             | 2.25                                   |

| dd Logical                                     | RX               | AL                       |                    | 3.75                                   |             | 1.75                                   |

| ND                                             | RR               | NR                       |                    | 4.75 3.75                              |             | 2.25                                   |

| ND                                             | RX               | N                        |                    | 4.75                                   |             | 2.25                                   |

| ND<br>ranch and Link                           | SI<br>RR         | NI<br>BALR               |                    | 3.75                                   |             | 3.00                                   |

| kranch and Link                                | RX               | BALK                     |                    | 3.25                                   |             | 2.25                                   |

| ranch on Condition                             | RR               | BCR                      |                    | 3.25<br>BR 2.50                        |             | 2.50                                   |

| Condition                                      |                  |                          | No                 | BR 1.00                                |             | 1.00                                   |

| branch on Condition                            | RX               | BC                       |                    | BR 2.75                                |             | 2.00                                   |

| Branch on Count                                | RR               | BCTR                     | No                 | BR 2.00                                |             | 1.25<br>2.50                           |

| Branch on Count                                | RX               | BCT                      |                    | 3.75<br>3.75                           |             | 2.75                                   |

| Compare                                        | RR               | CR                       |                    | 3.00                                   |             | 1.75                                   |

| Compare<br>Compare Halfword                    | RX<br>RX         | C<br>CH                  |                    | 4.00                                   |             | 2.25                                   |

| Compare Logical                                | RR               | CLR                      |                    | 4.00                                   |             | 2.25<br>1.75                           |

| Compare Logical                                | RX               | CL                       |                    | 3.00 4.00                              |             | 2.25                                   |

| Compare Logical                                | SI               | CLI                      |                    | 3.25                                   |             | 2.50                                   |

| Divide<br>Divide                               | RR<br>RX         | DR<br>D                  |                    | 31.75                                  |             | 28.75                                  |

| Exclusive OR                                   | RR               | XR                       | The second         | 32.75<br>3.75                          |             | 29.00<br>1.75                          |

| Exclusive OR                                   | RX               | X                        |                    | 4.75                                   |             | 2.25                                   |

| Exclusive OR                                   | SI<br>SI         | XI                       |                    | 3.75                                   |             | 3.00                                   |

| Halt I/O<br>Insert Character                   | SI<br>RX         | HIO                      |                    | 3.00 - 35.00                           |             | 2.25 - 35.00<br>2.50 EA, 2.25 OA       |

| Insert Storage Key                             | RR               | ISK                      |                    | 4.00<br>3.50                           |             | 2.00 EA, 2.25 OA                       |

| Lood                                           | RR               | LR                       |                    | 3.00                                   |             | 1.00                                   |

| Load                                           | RX               | L                        |                    | 4.00                                   |             | 2.25                                   |

| Load Address<br>Load and Test                  | RX<br>RR         | LA<br>LTR                |                    | 3.00<br>3.00                           |             | 1.25                                   |

| Lood Complement                                | RR               | LCR                      |                    | 3.00                                   |             | 1.75                                   |

| Load Halfword                                  | RX               | LH                       |                    | 4.00                                   |             | 2.25                                   |

| Load Negative<br>Load Positive                 | RR<br>RR         | L NR<br>L PR             | Constant in        | 3.00<br>3.00                           |             | 1.75<br>1.75                           |

| Load PSW                                       | SI               | LPK                      |                    | 4.50                                   |             | 3.75                                   |

| Move                                           | SI               | MVI                      |                    | 3.75                                   |             | 3.00                                   |

| Multiply                                       | RR               | MR                       |                    | 18.39                                  |             | 16.14                                  |

| Multiply                                       | RX<br>RX         | M<br>MH                  |                    | 19.39<br>12.72                         |             | 16.89<br>10.72                         |

| Multiply Halfword<br>OR                        | RR               | OR                       |                    | 3.75                                   |             | 1.75                                   |

| OR                                             | RX               | 0                        |                    | 4.75                                   |             | 2.25                                   |

| OP                                             | SI<br>RR<br>RR   | OI<br>SPM<br>SSK         |                    | 3.75<br>2.00<br>3.00                   |             | 3.00<br>1.50                           |

| Set Program Mask<br>Set Storage Key            | RR               | SSK                      |                    | 3.00                                   |             | 2.00<br>2.75 EA,3.00 OA                |

| Set System Mask                                | SI               | SSM                      | -                  | 3.50 EA, 4.00 OA                       | 5 ≤ 1       | S>1                                    |

|                                                |                  | Section 1                | 5≤3                | \$ > 3                                 |             |                                        |

| Shift Left Double                              | RS               | SLDA                     | 5.50               | 5.50 + 0.25 (S-3)<br>5.50 + 0.25 (S-3) | 3.00 3.00   | 3.00 + 0.25 (S-1)<br>3.00 + 0.25 (S-1) |

| Shift Left Double Logical                      | RS<br>RS         | SLDL<br>SLA              | 5.50               | 3.50 + 0.25 (S-3)                      | 2.25        | 2.25 + 0.25 (S-1)                      |

| Shift Left Single<br>Shift Left Single Logical | RS               | SLL                      | 3.50               | 3.50 + 0.25 (S-3)                      | 2.25        | 2.25 + 0.25 (S-1)                      |

| Shift Right Double                             | RS               | SRDA                     | 5.50               | 5.50 + 0.25 (S-3)<br>5.50 + 0.25 (S-3) | 3.00 3.00   | 3.00 + 0.25 (S-1)<br>3.00 + 0.25 (S-1) |

| Shift Right Double Logical                     | RS               | SRDL                     | 5.50 3.50          | 3.50 + 0.25 (S-3)                      | 2.25        | 2.25 + 0.25 (S-1)                      |

| Shift Right Single                             | RS<br>RS         | SRA<br>SRL               | 3.50               | 3.50 + 0.25 (S-3)                      | 2.25        | 2.25 + 0.25 (S-1)                      |

| Shift Right Single Logical                     | NO NO            |                          | a contract of the  | I<br>ingle indexing                    | For s       | ingle indexing                         |

|                                                |                  |                          | of sh              | ift instructions,                      | of sh       | ift instructions,                      |

|                                                |                  |                          | And and a state of | Add 1.00                               | A           | dd 0.25                                |

| 0                                              | SI               | SIO                      |                    | 3.00 - 40.00                           |             | 2.25 - 40.00                           |

| Start 1/O<br>Store                             | RX               | ST                       | and the second     | 4.25<br>4.75 EA,4.25 OA                |             | 2.50<br>3.00 EA,2.50 OA                |

| Store Character                                | RX               | STC                      | a series and a     | 4.75 EA,4.25 UA<br>4.25                |             | 2.50                                   |

| Store Halfword                                 | RX               | STH<br>SR                |                    | 3.75                                   | - Andrews   | 1.75                                   |

| Subtract                                       | RR               | S                        |                    | 4.75                                   |             | 2.25<br>2.25                           |

| Subtract<br>Subtract Halfword                  | RX               | SH                       |                    | 4.75<br>3.75                           |             | 2.25                                   |

| Subtract Logical                               | RR               | SLR<br>SL                |                    | 4.75                                   |             | 2.25                                   |

| Subtract Logical                               | RX<br>RR         | SVC                      |                    | 1.00                                   |             | 1.00                                   |

| Supervisor Call                                | SI               | TS                       |                    | 3.50<br>4.00 - 20.00                   |             | 2.75<br>3.25 - 20.00                   |

| Test and Set<br>Test Channel                   | SI               | TCH                      |                    | 3.00 - 38.00                           |             | 2.25 - 38.00                           |

| Test I/O                                       | SI               | TIO                      |                    | 3.00 EA, 3.25 OA                       |             | 2.25 EA,2.50 OA                        |

| Test Under Mask                                | SI               |                          |                    |                                        |             |                                        |

|                                                |                  | For double indexir       | ig of              |                                        |             | 0.75                                   |

| NOTES: EA = Even Address<br>OA = Odd Address   |                  | RX format instructi      | ions, add          | 1.00                                   |             | 0.75                                   |

| S = Number of bits                             | shifted          | antura                   |                    |                                        | Time "      |                                        |

| *Instruction added w                           | th protection t  | at shift instructions in | nclude single      | indexing; see "Indexing                | Time.       |                                        |

| ** All times except the                        | ose for the eigh |                          |                    |                                        |             |                                        |

| Figure 8. Execution                            | and the second   | or had In                | tructions          | and Protection-I                       | Feature In  | structions                             |

| Figure 8. Execution                            | Time for         | Standard Ins             |                    |                                        |             |                                        |

|                                                |                  |                          |                    |                                        |             |                                        |

|                                                |                  |                          |                    |                                        |             |                                        |

|                                                |                  |                          |                    |                                        |             |                                        |

|                                                |                  |                          |                    |                                        |             |                                        |

|                                                |                  |                          |                    |                                        |             |                                        |

Figure 18: IBM 360/44 Functional Characteristics, Page 17

ription 17

|                                      | Format               |            | Average Tir                   | me in Microseconds *                                  |

|--------------------------------------|----------------------|------------|-------------------------------|-------------------------------------------------------|

| Instruction                          |                      | Mnemonic   | Basic Model 44                | Model 44 with High-Speed<br>General Registers Feature |

| Add Normalized (Long)                | RR                   | ADR        | 6.28                          | 6.28                                                  |

| Add Normalized (Long)                | RX                   | AD         | 8.28                          | 7.53                                                  |

| Add Normalized (Short)               | RR                   | AER        | 3.81                          | 3.81                                                  |

| Add Normalized (Short)               | RX                   | AE         | 5.31                          | 4.56                                                  |

| Add Unnormalized (Long)              | RR                   | AWR        | 6.25                          | 6.25                                                  |

| Add Unnormalized (Long)              | RX                   | AW         | 8.25                          | 7.50                                                  |

| Add Unnormalized (Short)             | RR                   | AUR        | 3.79                          | 3.79                                                  |

| Add Unnormalized (Short)             | RX                   | AU         | 5.29                          | 4.54                                                  |

| control (control)                    |                      |            | J+27                          | 4,54                                                  |

| Compare (Long)                       | RR                   | CDR        | 5.84                          | 5.84                                                  |

| Compare (Long)                       | RX                   | CD         | 7.84                          | 7.09                                                  |

| Compare (Short)                      | RR                   | CER        | 3.50                          | 3.50                                                  |

| Compare (Short)                      | RX                   | CE         | 5.00                          | 4.25                                                  |

|                                      |                      |            | 5.00                          | 4.23                                                  |

| Divide (Long)                        |                      |            |                               |                                                       |

| Precision 14                         | RR                   | DDR        | 124.00                        | 124.00                                                |

| Precision 12                         | RR                   | DDR        | 108.50                        | 108.50                                                |

| Precision 10                         | RR                   | DDR        | 93.00                         | 93.00                                                 |

| Precision 8                          | RR                   | DDR        | 32.75                         | 32.75                                                 |

| Divide (Long)                        |                      |            | 02.70                         | 52.75                                                 |

| Precision 14                         | RX                   | DD         | 126.00                        | 125.25                                                |

| Precision 12                         | RX                   | DD         | 110.50                        | 109.75                                                |

| Precision 10                         | RX                   | DD         | 95.00                         | 94.25                                                 |

| Precision 8                          | RX                   | DD         | 34.75                         | 34.00                                                 |

| Divide (Short)                       | RR                   | DER        | 23.25                         | 23.25                                                 |

| Divide (Short)                       | RX                   | DE         | 24.75                         | 24.00                                                 |

|                                      |                      |            |                               |                                                       |

| Halve (Long)                         | RR                   | HDR        | 3.75                          | 3.75                                                  |

| Halve (Short)                        | RR                   | HER        | 2.00                          | 2.00                                                  |

|                                      |                      |            |                               |                                                       |

| Load (Long)                          | RR                   | LDR        | 3.00                          | 3.00                                                  |

| Load (Long)                          | RX                   | LD         | 5.00                          | 4.25                                                  |

| Load (Short)<br>Load (Short)         | RR                   | LER        | 1.00                          | 1.00                                                  |

| Load (Short)<br>Load and Test (Long) | RX<br>RR             | LE<br>LTDR | 3.00 3.00                     | 2.25                                                  |

| Load and Test (Short)                | RR                   | LTER       | 1.00                          | 3.00<br>1.00                                          |

| Load Complement (Long)               | RR                   | LCDR       | 3.00                          | 3.00                                                  |

| Load Complement (Short)              | RR                   | LCER       | 1.00                          | 1.00                                                  |

| Load Negative (Long)                 | RR                   | LNDR       | 3.00                          | 3.00                                                  |