# Written and Edited by E. Floyd Kvamme and L. H. Bieler

# TABLE OF CONTENTS

| Introduction                                                 | 1  |

|--------------------------------------------------------------|----|

| Technical Discussion - Digital Circuits                      | 2  |

| Current Sourcing                                             | 3  |

| Current Sinking                                              | 5  |

| Current Mode                                                 | 11 |

| Current Sourcing Circuits                                    | 14 |

| Resistor-Transistor Micrologic® Integrated Circuits          | 15 |

| Low Power Resistor-Transistor Micrologic Integrated Circuits | 23 |

| Counting Micrologic Integrated Circuits                      | 27 |

| Current Sinking Circuits                                     | 30 |

| Transistor-Transistor Micrologic Integrated Circuits         | 31 |

| Diode-Transistor Micrologic Integrated Circuits              | 35 |

| Low Power Diode-Transistor Micrologic Integrated Circuits    | 41 |

| Additional Current Sinking Circuits                          | 43 |

| Current Mode Circuits                                        | 48 |

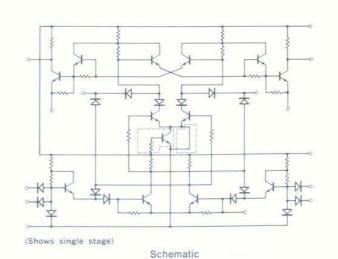

| Complementary Transistor Micrologic Integrated Circuits      | 49 |

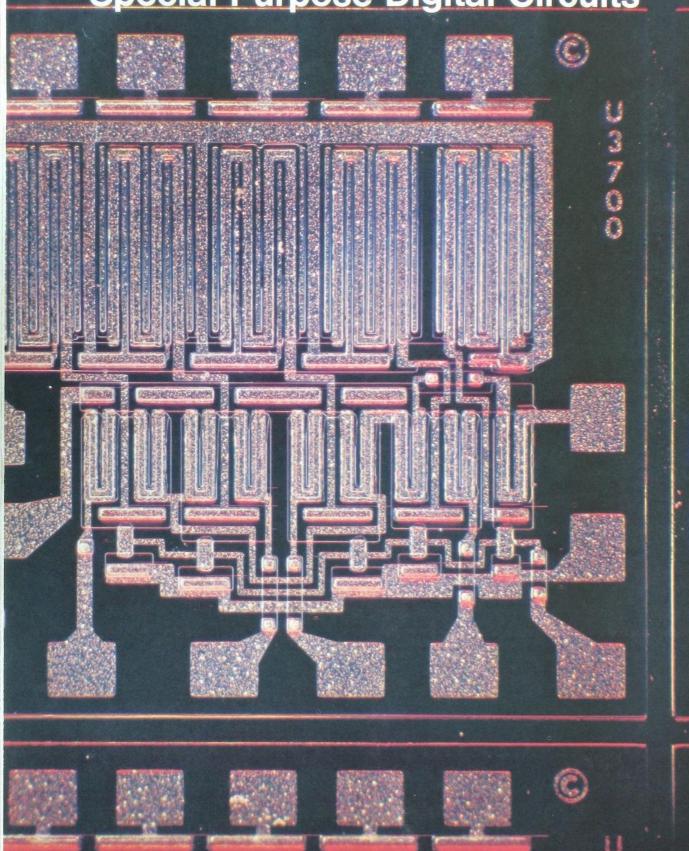

| Special Purpose Digital Circuits                             | 54 |

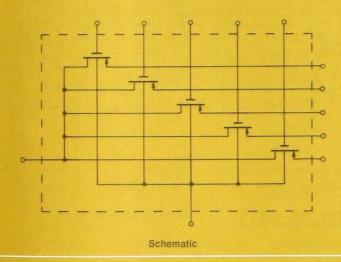

| MOS FET Circuits                                             | 55 |

| Memory Circuits                                              | 56 |

| Linear Circuits                                              | 58 |

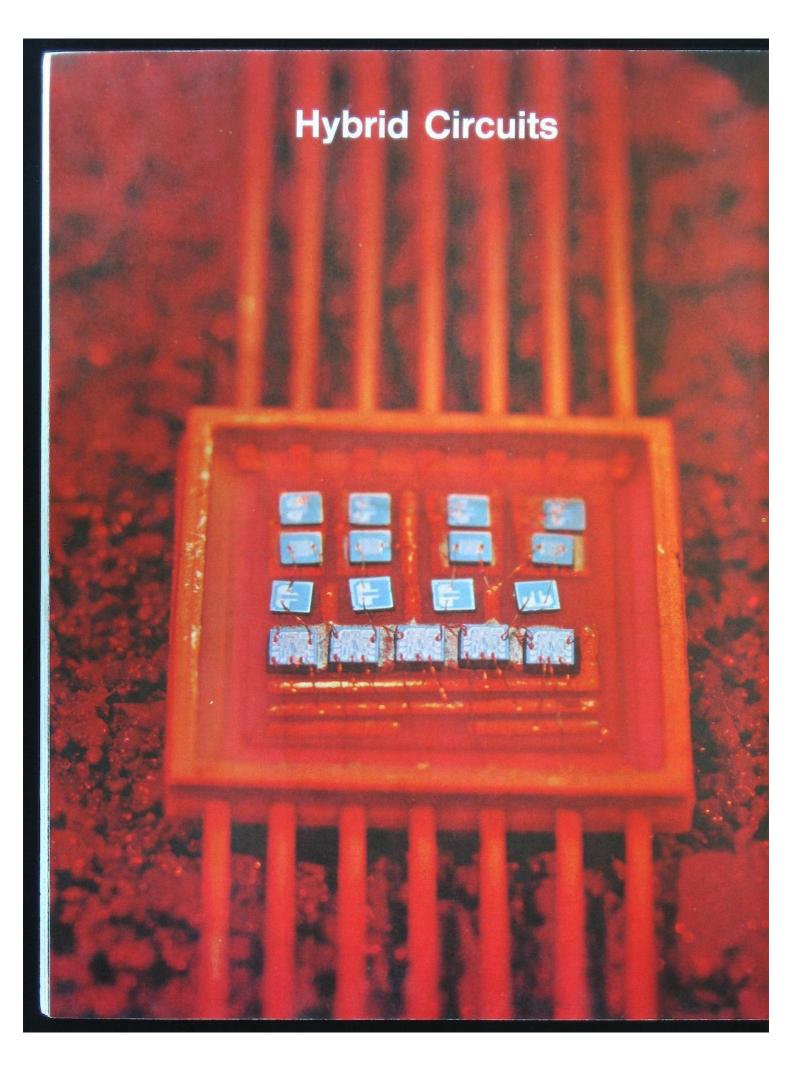

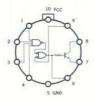

| Hybrid Circuits                                              | 62 |

| Custom Integrated Circuits                                   | 72 |

| Testing                                                      | 76 |

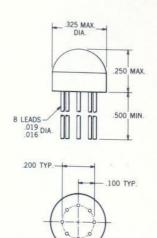

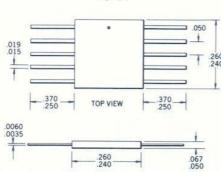

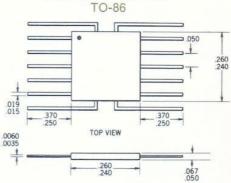

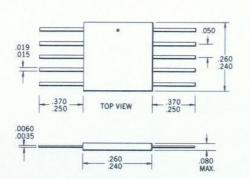

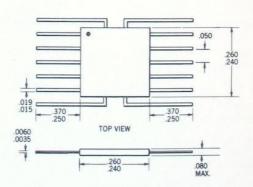

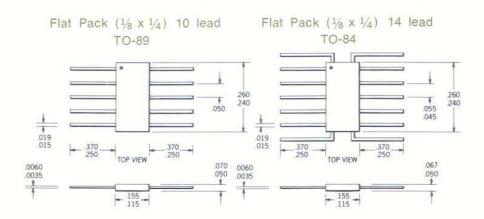

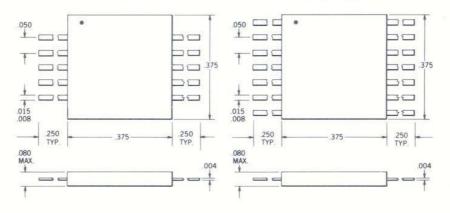

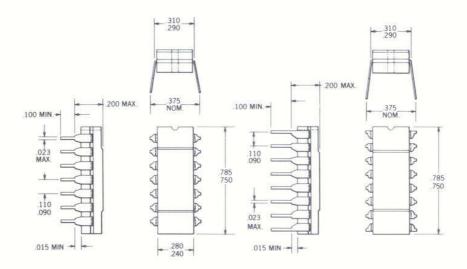

| Packaging                                                    | 78 |

| Product Code Explanation                                     | 83 |

| Index                                                        | 84 |

| Patent Information                                           | 85 |

| List of Photographs                                          | 85 |

Total capability is an important concept at Fairchild Semiconductor. As the largest and most experienced manufacturer of semiconductor devices in the world. Fairchild knows and understands the needs of the industry for which it is the leading supplier, and prides itself in its ability to design products which meet those needs. Over the years, this capability has led to the development of the most comprehensive line of digital and linear microcircuits the world has ever seen, produced in volume under a number of Fairchild patented processes Fairchild Semiconductor was founded in 1958 by a group of eight scientists who saw the myriad possibilities inherent in silicon mesa technology. Since that time, facilities have been expanded again and again to meet the demand for Fairchild's superior products. (Fairchild ships over one million units every month.) Plant locations now include California, New Mexico, and Maine, with affiliated plants in Hong Kong, Australia, Italy, Great Britain, France, Germany, and Sweden. Still further expansion is under consideration

The technology behind this rapid growth and overwhelming acceptance is Fairchild's patented Planar\* process, which incorporates the latest state-of-the-art developments to ensure the utmost in performance, stability, and reliability - Years of production experience stand behind these products - production experience which has enabled Fairchild to maintain price leadership across the board since it filled the first commercial order for a silicon mesa transistor in 1958 - Technology and experience combine to make this complete line of integrated circuits the most advanced and most reliable in the industry today - available at the lowest possible cost. For years, the name "Fairchild" has been synonymous with quality, leadership, and reliability. We plan to keep it that way.

The digital integrated circuits are presented according to three technological groupings with similar genetic characteristics: 1) Current Sourcing, 2) Current Sinking, and 3) Current Mode.

As used here, Current Source and Current Sink require some brief explanation. A common analogy is the kitchen sink, where the tap is the "source" and, of course, the place where the water goes is the "sink".

For RTL, current must flow from an output and be forced into the input of a similar RTL to activate the output of the second circuit. The output of the RTL, then, resembles the water tap of our analogy inasmuch as it is a "source".

DTL, however, requires a flow of current *out* of its input(s). Hence, the output stage of a circuit preceding a DTL gate resembles a "sink", in that it must provide a place for the outflowing current to go.

Current Mode circuits (CTL, CML) may either sink or source current, and take several forms. Their name is derived from their ability to change logic levels by switching between two active current levels or modes. They commonly employ emitter-follower, or emitter-coupled circuitry.

# **Current Sourcing**

# **General Characteristics**

Logic Current flows into inputs

Drive current flows out of outputs

Gate performs positive NOR function

Simplest logic form - good for complex circuits

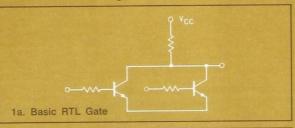

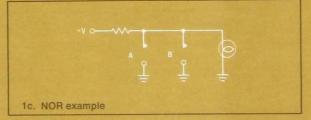

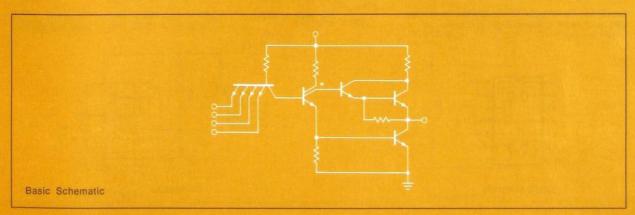

Figure 1a shows a typical RTL gate. Logically, this circuit performs the NOR gating function. Figure 1b has become a classic example of an "OR" circuit, demonstrating that when switch A and/or switch B is closed, the lamp lights - i.e., we have an output. An OR gating function, then, is performed when one, all, or any combination of "positive" events, defined here as the closing of switches, results in another positive event (in this case, the lighting of the lamp). Had we connected the circuit as in Figure 1c, while retaining our same definitions, we would have obtained a NOR result; that is, if we were to close either switch A or switch B, we would not have an output (the lamp would not light). Functionally, circuits 1a and 1c are identical in that they are both NOR circuits. Defining a "high" voltage condition (H) as a positive event, and a "low" voltage condition (L) as a negative event, we see that the RTL gate is a NOR gate: a high on the input of any or all of the bases saturates one or more transistors and forces the output to its low level.

The NOR gate may also be considered as an OR gate followed by an inverter.

Figure 1. OR/NOR Gating Examples

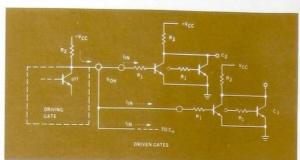

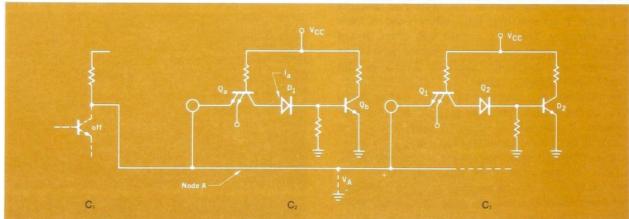

Figure 2 shows the output of an RTL gate driving the inputs of several other RTL circuits. Note that no particular RTL family need be specified. Fanout is the ratio of  $I_A$  to  $I_{IN}$ :  $I_A$  is determined by  $V_{CC}$  and  $R_2$ .  $I_{IN}$  is determined, primarily, by the  $h_{FE}$  of the transistor being driven and  $R_1$ .

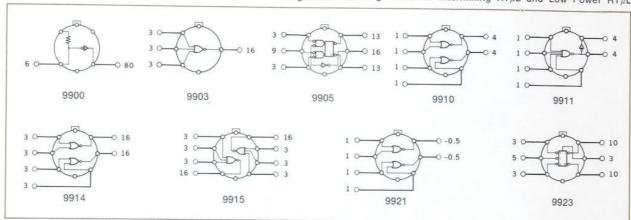

The RTL families, then, may be intermixed by changing the loading rules, as illustrated in Figure 3.  $I_{\rm IN}$  of the Low Power RT $_{\mu}L$  has been given a normalized value of 1.  $I_{\rm IN}$  of the RT $_{\mu}L$  is three times the  $I_{\rm IN}$  of the Low Power RT $_{\mu}L$ . In Figure 3, for example, we see that one RT $_{\mu}L9903$  element would drive sixteen Low Power RT $_{\mu}L9910$  or five RT $_{\mu}L9914$  inputs. Circuit C $_{\rm I}$  of Figure 2 is the current source for circuits C $_{\rm 2}$ , C $_{\rm 3}$  and C $_{\rm n}$ .

Figure 2. Typical RTL Gate Connection Showing Current Sourcing

Figure 3. Loading Rules for Intermixing  $RT_{\mu}L$  and Low Power  $RT_{\mu}L$

Another important difference in the RTL families is speed. As the various RTL families use transistors which are essentially identical, speed variations are primarily a result of different resistor values. For RT $_{\mu}$ L,  $R_{1}{=}450\Omega$  and  $R_{2}{=}640\Omega$  (see Figure 2). For Low Power RT $_{\mu}$ L, values of  $R_{1}$  and  $R_{2}$  are 1.5K $\Omega$  and 3.6K $\Omega$  respectively.

A transfer of electrical charge from one point to another is required to switch a transistor. The dimensional relationship between time, charge current, resistance, and capacitance may be expressed as  $t=\frac{Q}{1}=\frac{CV}{1}=RC$ ; time increases as R and C increase. Assuming constant capacitance, and identical transistors, time is primarily a function of resistance, which is greater for Low Power RT $\mu$ L than for RT $\mu$ L. While RT $\mu$ L and Low Power RT $\mu$ L capacitances are about the same, a change in the resistor values causes the switching speed of Low Power RT $\mu$ L to be higher than that of RT $\mu$ L. The following comparisons are for an RT $\mu$ L9914 and a Low Power RT $\mu$ L9910:

| Characteristic        | RTμL         | Low Power RT <sub>u</sub> L | Ratio of Low Power RT <sub>μ</sub> L to RT <sub>μ</sub> L |

|-----------------------|--------------|-----------------------------|-----------------------------------------------------------|

| onaractorione         | 111 μ2       | LOW TOWER TITHE             | Trans of Low Tower Trac to Trac                           |

| R,                    | $450\Omega$  | <b>1.5K</b> Ω               | 3.3:1                                                     |

| R <sub>2</sub>        | <b>640</b> Ω | <b>3.6K</b> Ω               | 5.6:1                                                     |

| t <sub>pd</sub> (typ) | 15 ns        | 30 ns                       | 2.0:1                                                     |

# **Current Sinking**

# **General Characteristics**

Logic current flows out of inputs

Outputs "sink" drive current

Gate performs positive NAND function

Highest voltage noise immunity

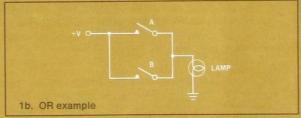

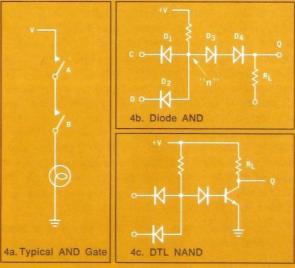

DTL is NAND logic. An AND circuit is one such as Figure 4a, in which only one set of conditions will activate the output. That is, closing switches A and B will turn on the lamp, but if either or both switches are open, the lamp will not light.

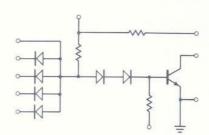

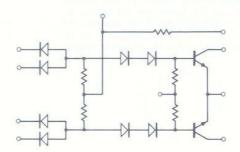

Figure 4b is a diode AND gate. For the output (Q) to be at a high level, inputs C and D must be at a high level (diodes  $D_1$  and  $D_2$  must be off). If either input C or D is connected to ground, the voltage at n will be insufficient to turn on  $D_3$  and  $D_4$ , and no current will flow through  $R_L$ ; point Q will remain at zero volts. The replacement of  $D_4$  and  $R_L$  in Figure 4b with a transistor produces a NAND circuit, as in Figure 4c, since the transistor inverts the output.  $R_L$  in Figure 4c is used to speed up the switching times; it is not necessary for logic performance.

Figure 4. AND Circuit examples

Figure 5. Typical DTL NAND Connection Showing Current Sinking.

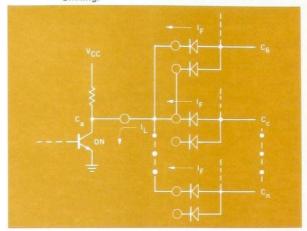

In Figure 5, current flows from circuits  $C_b$ ,  $C_c$ ,  $C_n$ , representing current sinking (i.e., the current must be drawn from the inputs.) DTL fan-out will be determined by the ratio  $I_{OL}/I_F$ .

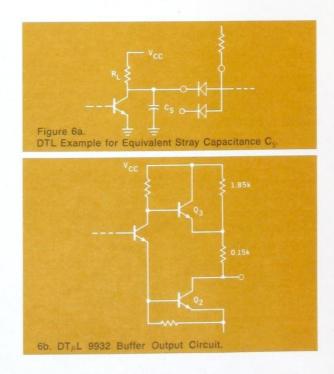

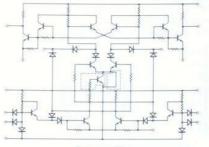

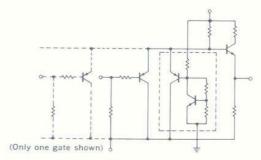

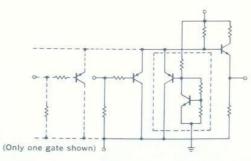

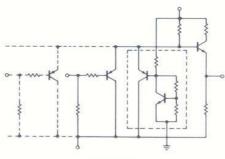

The discussion of speed characteristics for RTL also applies to DTL. There is, however, another method sometimes used to speed up circuits driving highly capacitive loads. As mentioned earlier, the DTL load resistor is added to speed up the output turn-off times. If there is a large stray capacitance to ground between the output of one gate and the input of another, this capacitance must be charged before the voltage can rise to threshold. Figure 6a shows a typical DTL connection where R<sub>L</sub> is the charging path to V<sub>CC</sub> for the stray capacitance Cs. Figure 6b is functionally the same, but an "active pull-up" has been added. Transistor Q3 is "on" when Q2 is "off", and "off" when  $Q_{\scriptscriptstyle 2}$  is "on". This arrangement provides a relatively low resistance charge path for charging the stray capacitance when Q2 is turned off, and a relatively high impedance to  $V_{\text{CC}}$ (1.85 K + .15 K) when  $Q_2$  is saturated.

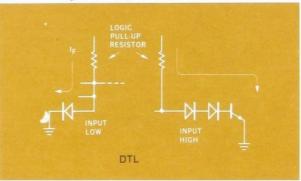

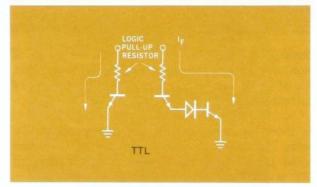

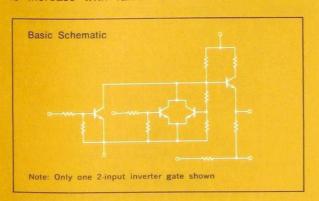

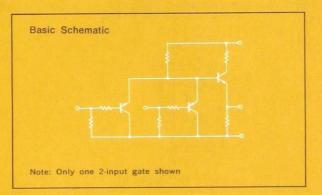

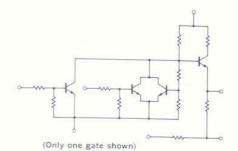

TTL has been classed with DTL, since it is also a current sinking logic. However, TTL is similar to DTL in several other aspects as well.

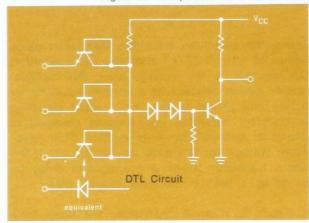

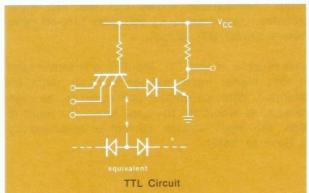

Figure 7. Comparison for DTL and TTL

Comparison of the simple DTL and TTL circuits in Figure 7 reveals that they differ only in their input circuitry. The DTL circuit has been drawn showing the transistor emitter inputs with their collector-base junctions shorted, which is the circuit configuration used for Fairchild DT<sub>µ</sub>L. (The emitter-base diode has lower capacitance and lower forward voltage drop than the basecollector diode, and is used in preference to it primarily because it has faster switching characteristics.) Operationally, the circuits are identical. A "low" on the input of the TTL gate shunts current away from the base circuit of the inverting transistor, and the output goes to a high level. With a "high" on the inputs, the current flows through the base-collector diode of the multipleemitter input transistor. If we dissect the DTL and the TTL circuits of Figure 7 and show the current paths, the similarity is readily apparent. (See Figure 8.)

The TTL circuit has one advantage and one disadvantage peculiar to the multiple-emitter transistor. The advantage is speed and the disadvantage is inverse beta leakage.

Figure 8. Input Comparison for DTL and TTL

During the switching transition that takes place within the circuit (TTL) after the input (emitter) has reached its low voltage level, the multiple-emitter device behaves as a normal transistor by pulling charge out of the "on" output circuitry; its collector saturates and remains clamped at saturation voltage above its emitter. This lower return voltage for the base driving circuit of the output transistor shortens propagation delay by providing a path for turn-off charge flow.

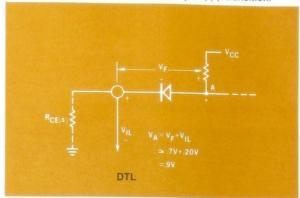

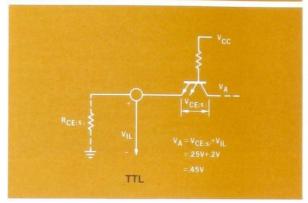

In Figure 9, node A represents the base drive circuit. Comparison shows that the TTL input provides approximately  $\frac{1}{2}$  volt more turn-off drive than a similar DTL circuit.

Inverse beta of the TTL input is a disadvantage in that higher input leakage currents must be tolerated. With the emitter connected to the high voltage, as would be the case when the input is high, the input leakage current is amplified by  $\beta_1$  (inverse beta).

Figure 9. Comparison of voltage drop for DTL and TTL during the Input (—) Output (+) transition.

Figure 10. TTL Example for Parallel Gate Operation.

Observe the example of Figure 10. If  $\beta_1$  of  $Q_a$  is high, the voltage at node A is reduced from rated  $V_{OH}$  of  $C_1$  because node A is pulling an amount of current equal to  $\beta_1 I_a$  from  $C_1$ .

As there has been a good deal of interest in TTL noise immunity, we should quickly review what noise immunity is, and make a comparison of TTL and DTL.

Noise immunity is a measure of safety margin; there are three margins one must consider: low level, high level, and a.c.

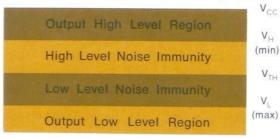

Low-level noise immunity is the difference between the threshold voltage of the circuit being driven and the most positive low-level voltage of the driving circuit. In Figure 11, this would be the difference between  $V_{\text{TH}}$  and  $V_{\text{L}}$  (max.)

Similarly, high-level noise immunity is the difference between  $V_{\text{H}}(\text{min})$  of the driving circuit and  $V_{\text{TH}}$  of the driven circuit. Noise immunity, then, is that amount of voltage spiking, positive or negative, that can be tolerated at  $V_{\text{L}}$  or  $V_{\text{H}}$  without exceeding the next threshold level and causing an error.

In reality, the threshold voltage is not a single value, but a region. There are two factors that must be considered: first, the threshold varies, within limits, of course, from unit to unit. Secondly, there is a minimum value required to hold an input circuit fully "on" for full fan-out, and a maximum value that can be applied without turning the circuit partially "off".

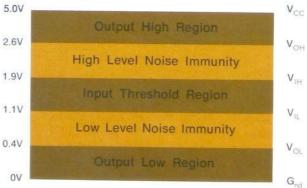

Figure 12 shows the voltage levels for DTL noise immunity calculation.

Using these values, we see that worst-case noise immunity at 25°C is:

High Level

$$N.I._{HL} = V_{OH} - V_{IH}$$

= 2.6V - 1.9V

= 0.7V

Low Level

$$N.I._{LL} = V_{IL} - V_{OL}$$

= 1.10V - 0.40V

= 0.7V

Typically,  $V_{\text{OH}}$  would be in excess of 4V,  $V_{\text{OL}}$  about 0.25V,  $V_{\text{IL}}$  about 1.3V, and  $V_{\text{IH}}$  less than 1.7V, for which a typical rating of 1 volt is the low level noise immunity usually given by manufacturers of DTL circuits.

Figure 11. Voltage Levels for Transistor Logic Circuits.

Figure 12. D.C. Voltage Levels for DTL Noise Immunity at  $25\,^{\circ}\mathrm{C}$

Spurious noise signals are present in every system. Some are externally generated and are electromagnetically coupled to the system through the atmosphere or the power line. Others are generated internally by relays or neighboring logic. Their frequency and magnitude cover a very wide spectrum. Some can be shielded out or designed around; others can be disregarded; and still others, one must learn to live with. The subject of a.c. noise immunity studies a system's immunity to these spurious noise sources.

A.C. noise immunity is usually most critical during the time that a circuit is switching through the threshold level. The following factors normally apply:

- The switching transition time interval.

- The stray capacitances that limit the circuit switching times may shunt noise to ground.

- Most noise signals exhibiting high voltage and narrow pulse width have insufficient power to drive many logic circuits.

For purpose of analysis, noise signals of relatively low frequency may be regarded as d.c. noise. If a circuit exhibits ringing just after a switching transition, which can be considered self-generated noise, the a.c. noise immunity is less than the d.c. noise immunity until the ringing settles out.

The TTL circuit of Figure 8 has the same d.c. noise immunity as the DTL circuit because the same number of diode drops exist between the input logic pull-up resistor and ground. One must compare the individual circuits to ascertain their relative merits in a.c. noise immunity. Generally, a circuit containing high output drive capability and using an active pull-up as shown in Figure 6b will generate more supply and ground line noise than a circuit without the pull-up, since high current pulses are delivered from active pull-up outputs. In high speed systems, care must be exercised in by-passing all supplies so as to minimize the effects of this noise.

# **Current Mode**

# **General Characteristics**

Logic current is small and flows in or out of inputs, depending on circuit (high impedance input).

Outputs source and/or sink current (low impedance output).

Gates perform AND/OR functions (AND/OR may be inverted by common base stage to NAND/NOR). Fastest logic form - non-saturating.

Both Current "Sinking" and "Sourcing" were rather straightforward; Current Mode circuits are more difficult to categorize. There are, however, some identifying characteristics.

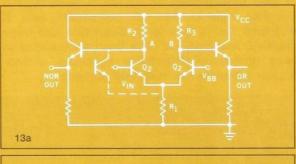

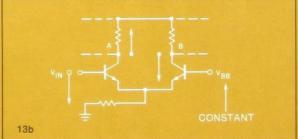

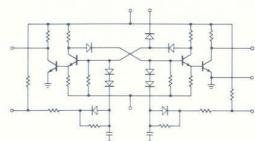

Figure 13a shows a Current Mode circuit. The peculiarity worth noting is emitter-coupled, non-saturating circuitry. The input portion of the circuit, Figure 13b, has been set apart for closer inspection; in this case, the input is differential. The arrows with a dot on the tail indicate the relative voltage variations of points A and B with respect to  $V_{\rm IN}$ . More inputs may be provided by adding more transistors parallel to  $Q_2$ . Since point A drives an emitter-follower, the output is in phase with point A. Likewise, the OR output is in phase with point B.

The emitter-follower output enhances propagation time because it does not saturate, and therefore there is no delay due to storage time.

Figure 13. Current Mode Circuit Example

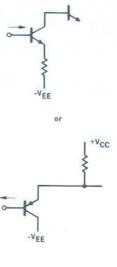

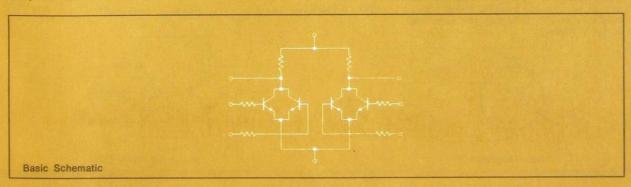

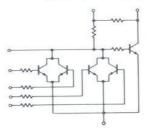

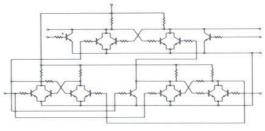

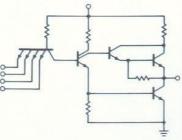

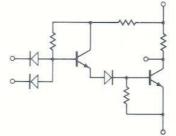

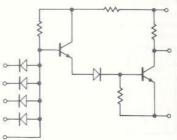

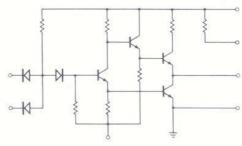

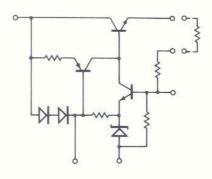

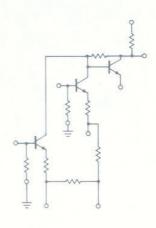

Fairchild  $CT_\mu L$  is a form of Current Mode logic, but it has been specially designed for application in simple circuit board or open transmission systems. The CTL basic gate in Figure 14 has those characteristics thus far attributed to Current Mode circuits. It is non-saturating logic and uses emitter-followers.

The inputs are PNP emitter-followers, biased so as to be "on" with no connection to their base. The inputs require low voltage, a current sink to drive the output to its low level, and a current source to make the output high.

The output of the CTL gate meets the requirements of the CTL inputs. When its inputs are high, the base of the NPN is high, the output is high, and the requirement of current sourcing is met. Conversely, with the inputs low, current sinking is provided.

One problem common to some forms of CML and CTL is "level shift". Since the voltage gain is less than, but nearly equal to one, the voltage extremes of the output are less than those of the input by a small amount. This means that after several decision levels, one must restore logic levels. This is done for CTL with the 9952 gates and the flip-flops, which use saturating inverter circuits.

No mention of flip-flops has been made. The current classification has been presented on the basis of gate requirements as an aid to grouping the Fairchild logic circuits into comparable sets. It is hoped that a functional distinction has been clarified, and that you have been encouraged to keep abreast of Fairchild's numerous technological advances in integrated circuits.

Figure 14. CTL AND Gate

V+

to other gates on same chip

CLAMP

Figure 14. CTL AND Gate

AND Gate

Figure 14. CTL AND Gate

# Input, Output Summary

INPUTS:

# CURRENT SOURCING

# CURRENT SINKING

# CURRENT MODE

# OUTPUTS: Normal Pull-Up or Pull-Down

# CURRENT SOURCING

# CURRENT SINKING

# CURRENT MODE

# **Current Sourcing Circuits**

# TOTAL CAPABILITY RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

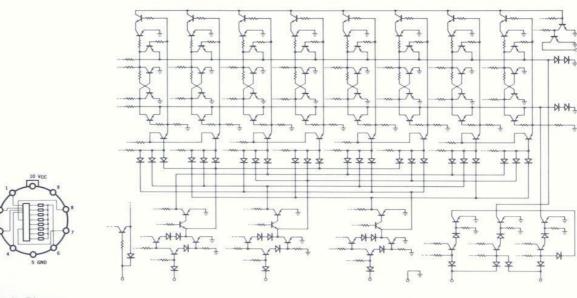

Fairchild Resistor-Transistor Micrologic® integrated circuits are a set of compatible integrated circuits manufactured by the patented Planar\* epitaxial process. All the necessary transistors and resistors are diffused into a single silicon wafer, with individual RT<sub>µ</sub>L gates interconnected by the patented metal-over-oxide process.

The RT<sub>µ</sub>L family in itself can comprise the logic section of a computer. It features very low propagation delays, making it ideal for use in highspeed systems. Typical propagation delay for the basic RT<sub>µ</sub>L circuit is 12 nanoseconds.

Fairchild RT<sub>µ</sub>L elements are specifically designed to permit highly reliable data processing at the lowest cost per logic function.

-65°C to +150°C

Power Dissipation

| RESISTO        | R-TRANSISTOR                                                                  | MICROLOGIC                     | C® INTEGRATED                     | CIRCUITS                                   |                             |

|----------------|-------------------------------------------------------------------------------|--------------------------------|-----------------------------------|--------------------------------------------|-----------------------------|

| PART<br>NUMBER | ELEMENT<br>TYPE                                                               | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C)          | DRIVE FACTOR                |

| 9900           | Buffer                                                                        | 300 mV                         | 16 nsec                           | 30 mW                                      | 25                          |

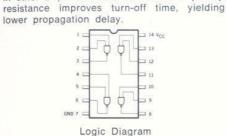

| DESCRIPTION    | N                                                                             |                                | SUPPLY VOLTAGE                    | TEMPERATURE RANGE                          | PACKAGE                     |

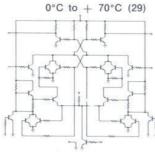

| use as a line  | nce inverting driver of driver, an astable or m                               | onostable                      | 3.0 volts ±10%                    | -55°C to +125°C (21)<br>0°C to +100°C (22) | Flat-Pack (3F)<br>TO-5 (5D) |

| for driving he | or pulse differentiator.<br>vily loaded circuits or<br>deterioration due to c | r minimiz-                     | 3.6 volts ±10%                    | +15°C to + 55°C (28)<br>0°C to + 70°C (29) | Epoxy (8B)                  |

| loading.       |                                                                               | *******                        | Ĉ                                 | <u></u>                                    |                             |

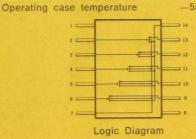

|                | 8 VCC                                                                         |                                | \$                                |                                            |                             |

|                | 2000                                                                          |                                | 0                                 | -w-K                                       |                             |

|                | ,00,                                                                          |                                | L                                 |                                            |                             |

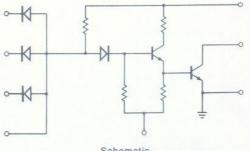

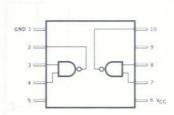

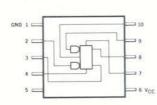

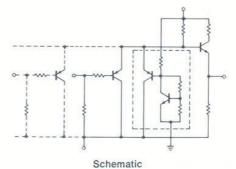

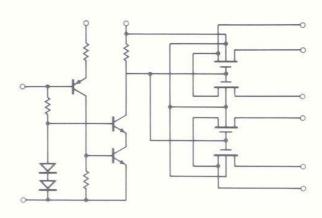

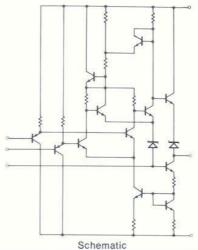

|                | Logic Diagram                                                                 |                                |                                   | Schematic                                  |                             |

| DADT           | FLENENT                                                                       |                                |                                   |                                            |                             |

| PART<br>NUMBER | TYPE                                                                          | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C)          | DRIVE FACTOR                |

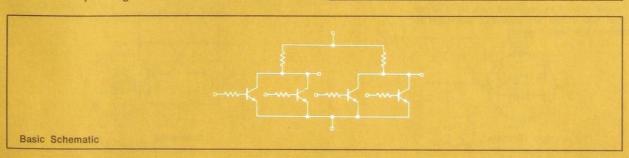

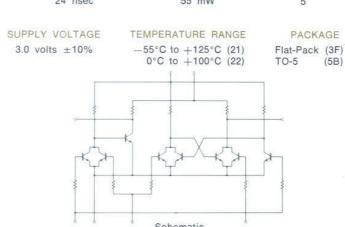

| 9901           | Counter Adapter                                                               | 300 mV                         | 24 nsec                           | 55 mW                                      | 5                           |

| DESCRIPTION    | J                                                                             |                                | SUPPLY VOLTAGE                    | TEMPERATURE RANGE                          | PACKAGE                     |

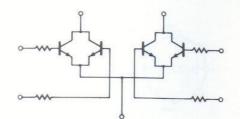

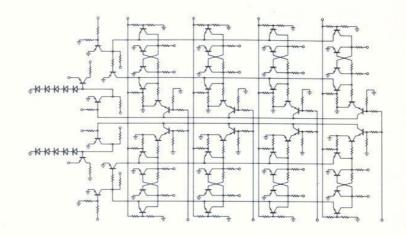

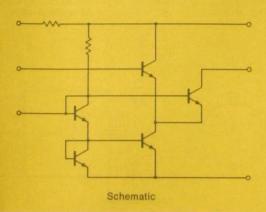

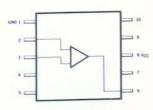

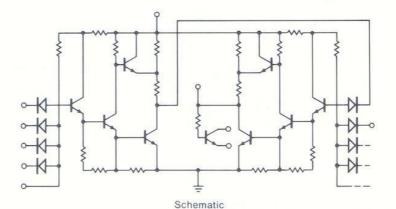

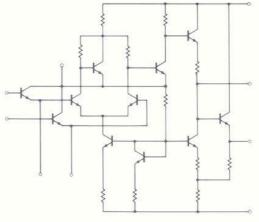

Non-inverting gating unit composed of five basic  $RT_{\mu}L$  circuits. Gives complementary outputs from a single-valued input. Power is supplied separately to the output nodes so that the outputs may be paralleled with other elements.

|                | Logic Diagram   |                                |                                   | Schematic                         |              |

|----------------|-----------------|--------------------------------|-----------------------------------|-----------------------------------|--------------|

| PART<br>NUMBER | ELEMENT<br>TYPE | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C) | DRIVE FACTOR |

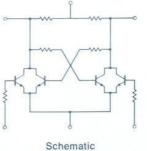

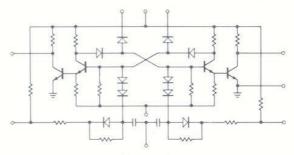

| 9902           | Flip-Flop       | 300 mV                         | 14 nsec                           | 22 mW                             | 4            |

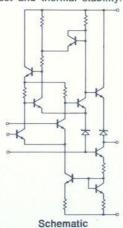

# DESCRIPTION

Consists of two basic RT<sub>µ</sub>L gate circuits internally cross-connected to form a bi-stable flip-flop storage unit. Since only a positive input can cause an internal change of state, the unit should be regarded as a NOR circuit. Input and output are provided externally for each of the gate circuits,

# SUPPLY VOLTAGE 3.0 volts $\pm 10\%$

TEMPERATURE RANGE  $-55^{\circ}$ C to  $+125^{\circ}$ C (21)  $0^{\circ}$ C to  $+100^{\circ}$ C (22)

PACKAGE

# RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

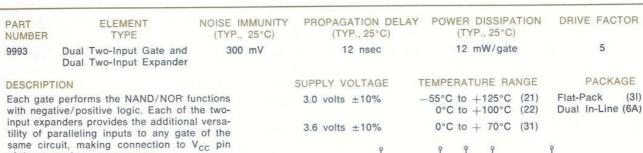

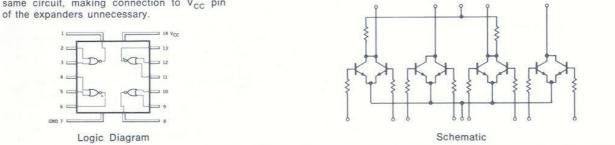

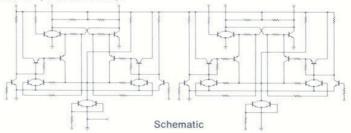

|   | PART<br>NUMBER                              | ELEMENT<br>TYPE                                                | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELA<br>(TYP., 25°C) | Y POWER DISSIPATION<br>(TYP., 25°C)                                                                                                                                                                                                                                                                                       | FAN-OUT                     |  |

|---|---------------------------------------------|----------------------------------------------------------------|--------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

|   | 9903                                        | Three-Input Gate                                               | 300 mV                         | 12 nsec                          | 12 mW                                                                                                                                                                                                                                                                                                                     | 5                           |  |

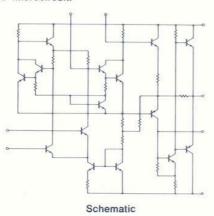

|   | DESCRIPTIO                                  | N                                                              |                                | SUPPLY VOLTAGE                   | TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                         | PACKAGE                     |  |

|   |                                             | gate for NAND/NOR f<br>generation of any logic                 |                                | 3.0 volts $\pm 10\%$             | -55°C to +125°C (21)<br>0°C to +100°C (22)                                                                                                                                                                                                                                                                                | Flat-Pack (3F)<br>TO-5 (5C) |  |

|   | Individual gat                              | exclusive use of gate of<br>te elements may be para            | alleled to                     | 3.6 volts ±10%                   | 0°C to + 70°C (29)                                                                                                                                                                                                                                                                                                        |                             |  |

|   | put node, or                                | number of inputs to a si<br>combined with other ele            |                                |                                  | ٩                                                                                                                                                                                                                                                                                                                         |                             |  |

|   | augment thei                                | r logic functions.                                             |                                |                                  | *                                                                                                                                                                                                                                                                                                                         |                             |  |

|   |                                             | 1000                                                           |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

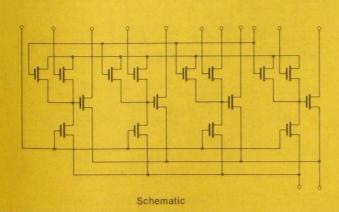

|   |                                             |                                                                |                                | ~~~                              | KomKomK                                                                                                                                                                                                                                                                                                                   |                             |  |

|   |                                             | 2                                                              |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | ,000,                                                          |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

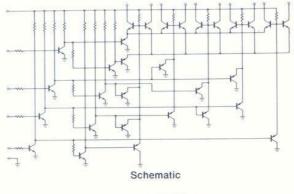

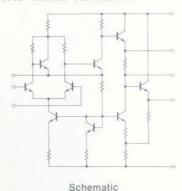

|   |                                             | Logic Diagram                                                  |                                |                                  | Schematic                                                                                                                                                                                                                                                                                                                 |                             |  |

| _ |                                             | Logic Diagram                                                  |                                |                                  | Concinatio                                                                                                                                                                                                                                                                                                                |                             |  |

|   | PART<br>NUMBER                              | ELEMENT<br>TYPE                                                | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELA<br>(TYP., 25°C) | Y POWER DISSIPATION<br>(TYP., 25°C)                                                                                                                                                                                                                                                                                       | FAN-OUT                     |  |

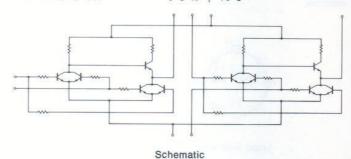

|   | 9904                                        | Half-Adder                                                     | 300 mV                         | 16 nsec                          | 34 mW                                                                                                                                                                                                                                                                                                                     | 5                           |  |

|   | DESCRIPTIO                                  | N                                                              |                                | SUPPLY VOLTAGE                   | TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                         | PACKAGE                     |  |

|   | Multi-purpose                               | combination of thre                                            | e basic                        | 3.0 volts ±10%                   | -55°C to +125°C (21)                                                                                                                                                                                                                                                                                                      | Flat-Pack (3F)              |  |

|   | RT <sub>µ</sub> L circuits<br>able for half | as two-level AND/OR gradder, exclusive OR,                     | gate suit-<br>or other         |                                  | 0°C to +100°C (22)                                                                                                                                                                                                                                                                                                        | TO-5 (5B)                   |  |

|   | similar logic                               |                                                                |                                | 3.6 volts ±10%                   | $0^{\circ}C \text{ to } + 70^{\circ}C \text{ (29)}$                                                                                                                                                                                                                                                                       |                             |  |

|   |                                             |                                                                |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | 8 VCC                                                          |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | 1000                                                           |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | 2000                                                           |                                | ٦                                |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             |                                                                |                                | r.                               |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | 4 GND                                                          |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | Logic Diagram                                                  |                                | ۰                                | Schematic                                                                                                                                                                                                                                                                                                                 |                             |  |

|   |                                             | 20310 212312111                                                |                                |                                  | Contoniatio                                                                                                                                                                                                                                                                                                               |                             |  |

|   | PART<br>NUMBER                              | ELEMENT<br>TYPE                                                | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELA<br>(TYP., 25°C) | Y POWER DISSIPATION<br>(TYP., 25°C)                                                                                                                                                                                                                                                                                       | FAN-OUT                     |  |

|   | 9905                                        | Half-Shift Register<br>(with Inverter)                         | 300 mV                         | 18 nsec                          | 53 mW                                                                                                                                                                                                                                                                                                                     | 4                           |  |

|   | DESCRIPTIO                                  | N                                                              |                                | SUPPLY VOLTAGE                   | TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                         | PACKAGE                     |  |

|   | five basic R1                               | storage element comp<br>Γ <sub>μ</sub> L gate circuits. Intern | al cross-                      | $3.0 \text{ volts } \pm 10\%$    | -55°C to +125°C (21)<br>0°C to +100°C (22)                                                                                                                                                                                                                                                                                | Flat-Pack (3F)<br>TO-5 (5B) |  |

|   | connection of                               | of the two output gate<br>mory. Should be regarde              | circuits                       | 3.6 volts ±10%                   | 0°C to + 70°C (29)                                                                                                                                                                                                                                                                                                        | 10-3 (38)                   |  |

|   |                                             | D input logic levels.                                          | , d do 10                      | Ţ                                | 1 1 1 1                                                                                                                                                                                                                                                                                                                   |                             |  |

|   |                                             | 8 Vcc                                                          |                                | •                                |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | 1000                                                           |                                | +                                | < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < < > < < > < < > < < > < < > < < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < < > < < > < < > < < > < < > < < > < < > < < > < < > < < > < < |                             |  |

|   |                                             |                                                                |                                |                                  |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             |                                                                |                                | E T                              |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | ,00,                                                           |                                | f                                |                                                                                                                                                                                                                                                                                                                           |                             |  |

|   |                                             | Logic Diagram                                                  |                                | L                                | Sahara ii                                                                                                                                                                                                                                                                                                                 |                             |  |

|   |                                             | Logic Diagram                                                  |                                |                                  | Schematic                                                                                                                                                                                                                                                                                                                 |                             |  |

| RESIST                                                                                                                                          | OR-TRANSISTOR                                        | MICROLOGIC                     | ® INTEGRATED                     | CIRCUITS                                   |                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|----------------------------------|--------------------------------------------|-----------------------------|

| PART<br>NUMBER                                                                                                                                  | ELEMENT<br>TYPE                                      | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELA<br>(TYP., 25°C) | Y POWER DISSIPATION<br>(TYP., 25°C)        | FAN-OUT                     |

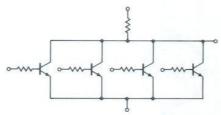

| 9906                                                                                                                                            | Half-Shift Register (without Inverter)               | 300 mV                         | 22 nsec                          | 36 mW                                      | 4                           |

| DESCRIPTION                                                                                                                                     |                                                      |                                | SUPPLY VOLTAGE                   | TEMPERATURE RANGE                          | PACKAGE                     |

| four basic F                                                                                                                                    | t storage element comp<br>RTμL gate circuits. Intern | al cross-                      | 3.0 volts ±10%                   | -55°C to +125°C (21)<br>0°C to +100°C (22) | Flat-Pack (3F)<br>TO-5 (5B) |

| provides me                                                                                                                                     | of the two output gate                               | cascaded                       | 3.6 volts ±10%                   |                                            |                             |

| internal logic levels, the unit changes state in<br>response to near-ground input signals (like<br>the 9905), and should be regarded as requir- |                                                      |                                |                                  |                                            |                             |

| ing NAND i                                                                                                                                      | nput logic levels.                                   | is requir-                     | •                                |                                            |                             |

|                                                                                                                                                 | 1000                                                 |                                |                                  | K.>-\-(\)                                  |                             |

|                                                                                                                                                 | 2 (- EDT) .                                          |                                | ŗĶ                               | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\     |                             |

|                                                                                                                                                 | ,600,                                                |                                |                                  |                                            |                             |

|                                                                                                                                                 | Logic Diagram                                        |                                |                                  | Schematic                                  |                             |

| PART<br>NUMBER                                                                                                                                  | ELEMENT<br>TYPE                                      | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELA                 | Y POWER DISSIPATION<br>(TYP., 25°C)        | FAN-OUT                     |

| PART<br>NUMBER | ELEMENT<br>TYPE | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C) | FAN-OUT |

|----------------|-----------------|--------------------------------|-----------------------------------|-----------------------------------|---------|

| 9907           | Four-Input Gate | 300 mV                         | 12 nsec                           | 12 mW                             | 5       |

| DESCRIPTION    |                 |                                | OUDDLY VOLTAGE                    | THE PARTY OF THE PARTY OF         |         |

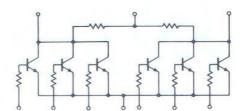

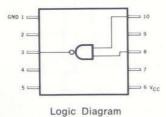

# DESCRIPTION

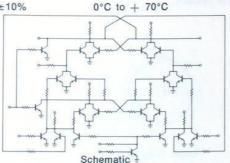

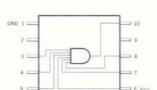

Four-input gate for NAND/NOR functions. Permits the generation of any logic-function. Individual four-input gate elements may be paralleled to increase the number of inputs to a single output node, or combined with other elements to augment their logic functions.

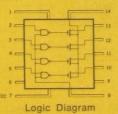

Logic Diagram

| SUPPLY VOLTAGE                | TEMPERATURE RANGE                          | PACKAGE                     |

|-------------------------------|--------------------------------------------|-----------------------------|

| 3.0 volts ±10%                | -55°C to +125°C (21)<br>0°C to +100°C (22) | Flat-Pack (3F)<br>TO-5 (5B) |

| $3.6 \text{ volts } \pm 10\%$ | 0°C to + 70°C (29)                         |                             |

Schematic

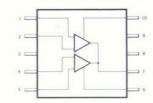

| PART<br>NUMBER                                                                                                                                                                 | ELEMENT<br>TYPE     | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C)          | FAN-OU                    | Т  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------|-----------------------------------|--------------------------------------------|---------------------------|----|

| 9914                                                                                                                                                                           | Dual Two-Input Gate | 300 mV                         | 12 nsec                           | 24 mW                                      | 5                         |    |

| DESCRIPTION                                                                                                                                                                    | ON                  |                                | SUPPLY VOLTAGE                    | TEMPERATURE RANGE                          | PACKAGE                   | E  |

| Dual two-input gate capable of generating any logic function. Element circuits may be cross-connected to form a flip-flop, or connected in tandem to form non-inverting gates. |                     |                                | 3.0 volts ±10%                    | -55°C to +125°C (21)<br>0°C to +100°C (22) | Flat-Pack (3F<br>TO-5 (5E |    |

|                                                                                                                                                                                |                     |                                | 3.6 volts ±10%                    | 0°C to + 70°C (29)<br>+15°C to + 55°C (28) | Epoxy (8A                 | A) |

|                                                                                                                                                                                | 8 VCC               |                                |                                   |                                            | <b>~~</b>                 |    |

|                                                                                                                                                                                | Logic Diagram       |                                |                                   | Schematic                                  |                           |    |

# RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

| PART   | ELEMENT               | NOISE IMMUNITY | PROPAGATION DELAY | POWER DISSIPATION | FAN-OUT |

|--------|-----------------------|----------------|-------------------|-------------------|---------|

| NUMBER | TYPE                  | (TYP., 25°C)   | (TYP., 25°C)      | (TYP., 25°C)      |         |

| 9915   | Dual Three-Input Gate | 300 mV         | 12 nsec           | 24 mW             | 5       |

# DESCRIPTION

Dual three-input gate capable of performing flip-flop and non-inverting gate functions.

# SUPPLY VOLTAGE

TEMPERATURE RANGE

PACKAGE

3.0 volts ±10%

-55°C to +125°C (21) 0°C to +100°C (22) Flat-Pack (3F)

3.6 volts ±10%

0°C to + 70°C (29)

TO-5 (5B)

Logic Diagram

Schematic

| P | A | R | Г |   |   |

|---|---|---|---|---|---|

| N | U | M | B | E | R |

ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

(TYP., 25°C)

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C)

FAN-OUT

9923

J-K Flip-Flop

300 mV

40 nsec

54 mW

3

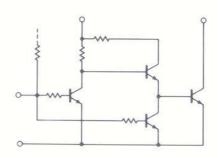

# DESCRIPTION

Complete general purpose storage element designed for use in industrial shift register and binary counting applications.

TEMPERATURE RANGE

PACKAGE

3.6 volts ±10%

+15°C to + 55°C (29) +15°C to + 55°C (28)

(5B) TO-5 Ероху (8A)

Operation from  $-55^{\circ}\text{C}$  to  $+125^{\circ}$  can be obtained by use of a sliding voltage supply system (i.e., 4.2 volts at -55°C, 3.6 volts at 25°C, 2.6 volts

at +125°C; ±10%)

Logic Diagram

Schematic

# PART NUMBER

9926

ELEMENT TYPE

J-K Flip-Flop

NOISE IMMUNITY (TYP., 25°C)

300 mV

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C)

40 nsec

(TYP., 25°C)

56 mW

**FAN-OUT**

5

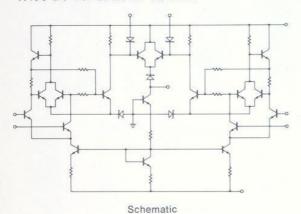

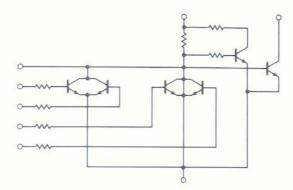

# DESCRIPTION

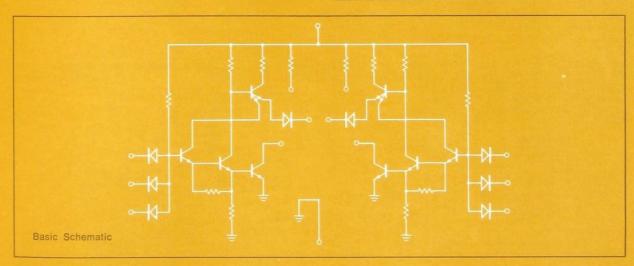

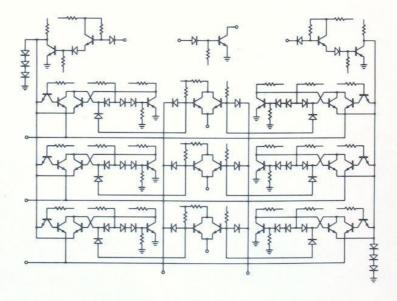

Complete, general purpose storage element suitable for use in shift registers, counters, or any type of control function. Asynchronous preset and preclear inputs are included for presetting counters, inserting parallel data in registers, and similar applications.

Logic Diagram

# SUPPLY VOLTAGE

3.0 volts  $\pm 10\%$

3.6 volts ±10%

# TEMPERATURE RANGE

-55°C to +125°C (21) 0°C to +100°C (22)

Schematic

PACKAGE

Flat-Pack (3F) TO-5 (5F)

### RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

PART NUMBER ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

PROPAGATION DELAY (TYP., 25°C)

POWER DISSIPATION (TYP., 25°C)

DRIVE FACTOR

9927

Quad Inverter

300 mV

12 nsec

48 mW

DESCRIPTION

Quad single-input inverter for multi-inversion

functions.

SUPPLY VOLTAGE

TEMPERATURE RANGE

PACKAGE

3.0 volts  $\pm 10\%$

-55°C to +125°C (21)

0°C to +100°C (22)

Flat-Pack (3F)

3.6 volts ±10%

0°C to + 70°C (29)

TO-5 (5F)

Logic Diagram

Schematic

PART

NUMBER

ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

PROPAGATION DELAY (TYP., 25°C)

POWER DISSIPATION (TYP., 25°C)

DRIVE FACTOR

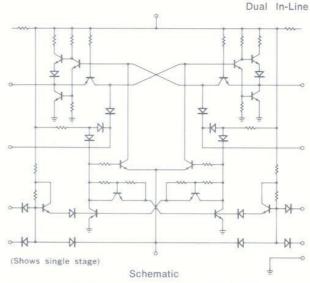

9970

Dual Half-Adder

300 mV

16 nsec

34 mW/half-adder

5

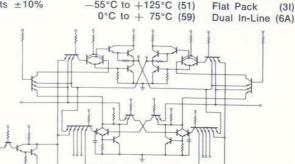

(31)

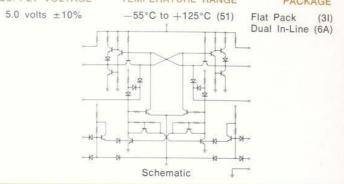

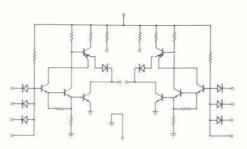

DESCRIPTION

Multi-purpose element suitable for half-adder, exclusive OR, and other similar logic con-

structions.

SUPPLY VOLTAGE

TEMPERATURE RANGE -55°C to +125°C (21)

PACKAGE

3.6 volts ±10%

0°C to +100°C (22) 0°C to + 70°C (29)

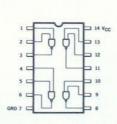

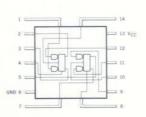

Flat-Pack Dual In-Line (6A)

Logic Diagram

3.0 volts ±10%

PART NUMBER

ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

PROPAGATION DELAY (TYP., 25°C)

POWER DISSIPATION (TYP., 25°C)

DRIVE FACTOR

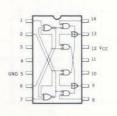

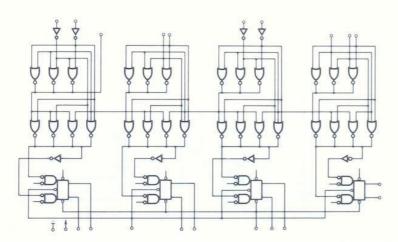

9991

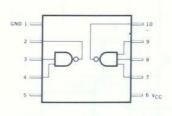

Quad Two-Input Gate

300 mV

12 nsec

12 mW/gate

DESCRIPTION

Each of the four two-input gates performs the NAND/NOR functions with positive/negative

logic.

SUPPLY VOLTAGE 3.0 volts ±10%

TEMPERATURE RANGE -55°C to +125°C (21) 0°C to +100°C (22)

PACKAGE Flat-Pack

Dual In-Line (6A)

3.6 volts ±10%

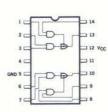

Logic Diagram

0°C to + 70°C (29)

Schematic

| RESIS                                                                                          | TOR-TRANSISTOR                                                                                                                                   | MICROLOGIC                     | © INTEGRATED                      | CIRCUITS                                   | ericis i tiilais                       |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------|--------------------------------------------|----------------------------------------|

| PART<br>NUMBER                                                                                 | ELEMENT<br>TYPE                                                                                                                                  | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION (TYP., 25°C)             | DRIVE FACTOR                           |

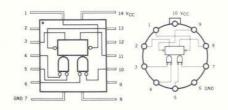

| 9992                                                                                           | Quad Two-Input Expander                                                                                                                          | 300 mV                         | 12 nsec                           | <del>-</del>                               | -0.5                                   |

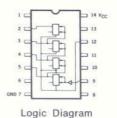

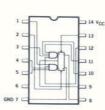

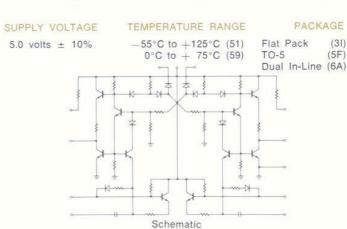

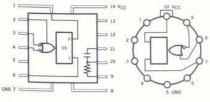

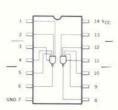

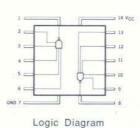

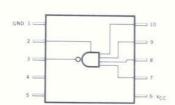

| DESCRIP                                                                                        | TION                                                                                                                                             |                                | SUPPLY VOLTAGE                    | TEMPERATURE RANGE                          | PACKAGE                                |

| Consists of four two-input gates without col-<br>lector node resistors. Output terminal may be |                                                                                                                                                  |                                | 3.0 volts ±10%                    | -55°C to +125°C (21)<br>0°C to +100°C (22) | Flat Pack (3I)<br>Dual In-Line (6A)    |

| connected<br>fan-in ca<br>with ano                                                             | connected in parallel with any gate to increase fan-in capability. When used in conjunction with another gate, V <sub>CC</sub> must also be con- |                                | 3.6 volts ±10%                    | 0°C to + 70°C (29)                         |                                        |

| nected to                                                                                      | pin 14 of the expander.                                                                                                                          |                                | Ì                                 | Î                                          | Ĺ                                      |

|                                                                                                | 3 13 13                                                                                                                                          |                                | K.74                              |                                            | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| 4-                                                                                             |                                                                                                                                                  |                                | <b>1 1 1 1</b>                    |                                            |                                        |

|                                                                                                | 5 0 0 0                                                                                                                                          |                                |                                   |                                            |                                        |

|                                                                                                | GND 7 8                                                                                                                                          |                                |                                   |                                            |                                        |

|                                                                                                | Logic Diagram                                                                                                                                    |                                |                                   | Schematic                                  |                                        |

SUPPLY VOLTAGE

3.6 volts ±10%

| PART<br>NUMBER | ELEMENT<br>TYPE    | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C) | DRIVE FACTOR |

|----------------|--------------------|--------------------------------|-----------------------------------|-----------------------------------|--------------|

| 9994           | Dual J-K Flip-Flop | 300 mV                         | 40 nsec                           | 54 mW/FF                          | 3            |

# DESCRIPTION

Complete general purpose storage element designed for use in industrial shift register and binary counting applications.

\*Operation may be expanded to  $-55^{\circ}$ C to  $+125^{\circ}$ C by using a sliding scale power supply (i.e., 4.2 volts at  $-55^{\circ}$ C, 3.5 volts at  $+25^{\circ}$ C, 2.6 volts at  $+125^{\circ}$ C;  $\pm 10^{\circ}$ ).

TEMPERATURE RANGE\*

0°C to + 70°C (29)

Flat-Pack

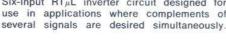

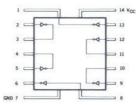

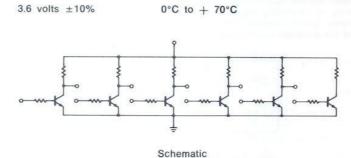

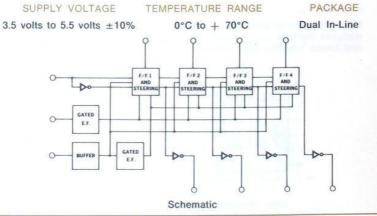

### RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS PART ELEMENT NOISE IMMUNITY PROPAGATION DELAY POWER DISSIPATION DRIVE FACTOR NUMBER TYPE (TYP., 25°C) (TYP., 25°C) (TYP., 25°C) Dual Buffer and Dual 9995 300 mV 12 nsec (gate) 30 mW/buffer Three-Input Gate Expander 16 nsec (buffer) DESCRIPTION SUPPLY VOLTAGE TEMPERATURE RANGE Each of the three-input gates performs the -55°C to +125°C 3.0 volts ±10% NAND/NOR function with positive/negative 0°C to +100°C logic. Each of the buffers is a low-impedance, inverting driver circuit which can supply sub-0°C to + 70°C 3.6 volts ±10% stantially more output current than a standard RT<sub>µ</sub>L gate. DOD. 0.0 Logic Diagram Schematic PART ELEMENT NOISE IMMUNITY PROPAGATION DELAY POWER DISSIPATION NUMBER TYPE (TYP., 25°C) (TYP., 25°C) (TYP., 25°C) 9996 300 mV Hex Inverter 12 nsec 12 mW/node DESCRIPTION TEMPERATURE RANGE SUPPLY VOLTAGE Six-input RT<sub>µ</sub>L inverter circuit designed for 3.0 volts ±10% -55°C to +125°C use in applications where complements of 0°C to +100°C

Logic Diagram

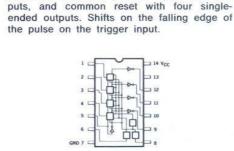

Features serial and parallel inputs and out-

5 (gate)

25 (buffer)

PACKAGE

Flat-Pack

**FAN-OUT**

5

PACKAGE

Flat Pack

Dual In-Line

Dual In-Line

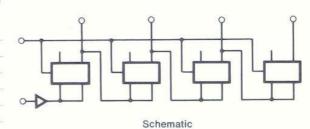

| PART<br>NUMBER | ELEMENT<br>TYPE         | NOISE IMMUNITY<br>(TYP., 25°C) | PROPAGATION DELAY<br>(TYP., 25°C) | POWER DISSIPATION<br>(TYP., 25°C) | FAN-OUT |

|----------------|-------------------------|--------------------------------|-----------------------------------|-----------------------------------|---------|

| 9997           | Four-Bit Shift Register | 300 mV                         | 45 nsec                           | 220 mW                            | 5       |

| DESCRIPT       | ION                     |                                | SUPPLY VOLTAGE                    | TEMPERATURE RANGE                 | PACKAGE |

Logic Diagram

# TOTAL CAPABILITY LOW POWER RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

Fairchild Low Power Resistor-Transistor Micrologic® integrated circuits (formerly Milliwatt Micrologic®) are a compatible set of integrated logic building blocks. As with the standard  $RT_{\mu}L$  family, all the necessary transistors and resistors are diffused into a single silicon wafer by the patented Planar\* process, with individual  $RT_{\mu}L$  gates inter-connected by the patented metalover-oxide technique.

Low Power  $RT_{\mu}L$  features very low propagation delays at low DC power dissipation. Typical propagation delay for the basic circuit is 40 nanoseconds; power dissipation is 2 mW.

These low power elements may be used through the full military temperature range of -55°C to +125°C. Absolute Maximum Ratings

Maximum voltage applied to pin 8

Maximum voltage

applied to pin 8

(pulsed < 1 second

Maximum voltage

applied to any input pin

Storage Temperature

--65°C to +150°C

8 volts

Power Dissipation

250 mW

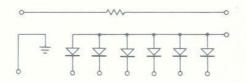

LOW POWER RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS ELEMENT PROPAGATION DELAY POWER DISSIPATION NUMBER (TYP., 25°C) (TYP., 25°C) (TYP., 25°C) 9908 Adder 300 mV 70 nsec 10 mW DESCRIPTION TEMPERATURE RANGE Performs Mod 2 addition, or exclusive OR  $3.0 \text{ volts } \pm 10\%$ -55°C to +125°C (21) Flat-Pack (3F) function, and is used to select one of two data streams under control of a single gate TO-5  $3.6 \text{ volts } \pm 10\%$ 0°C to + 70°C (29) signal. Logic Diagram Schematic PART ELEMENT NOISE IMMUNITY PROPAGATION DELAY POWER DISSIPATION NUMBER (TYP., 25°C) (TYP., 25°C) TYPE (TYP., 25°C) 9909 Buffer 300 mV 70 nsec DESCRIPTION SUPPLY VOLTAGE TEMPERATURE RANGE Two-input, low impedance inverting driver  $3.0 \text{ volts } \pm 10\%$ -55°C to +125°C (21) circuit. Can supply more output current than the basic RT<sub>µ</sub>L circuit. For use as a line 3.6 volts ±10% 0°C to + 70°C (29) driver, astable or monostable multivibrator, or pulse differentiator.

Logic Diagram

FLEMENT

Logic Diagram

# PACKAGE Flat-Pack (3F) TO-5 (5B) Schematic

Schematic

FAN-OUT

4

PACKAGE

FAN-OUT

30

(5B)

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C) (TYP., 25°C) PART NOISE IMMUNITY FAN-OUT NUMBER TYPE (TYP., 25°C) 9910 Dual Gate 300 mV 35 nsec 4 mW DESCRIPTION SUPPLY VOLTAGE PACKAGE TEMPERATURE RANGE Dual two-input gate for use as a pair of NOR -55°C to +125°C (21) 3.0 volts  $\pm 10\%$ Flat-Pack (3F) gates, as an R-S flip-flop, as a pair of inver-TO-5 (5B) ters, or as a double inverter. It may also be 3.6 volts ±10% 0°C to + 70°C (29) used with the 9921 Gate Expander to increase its fan-in capacity.

# LOW POWER RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

PART NUMBER 9911 DESCRIPTION PART NUMBER 9912

ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

(TYP., 25°C)

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C)

**FAN-OUT**

4

Gate

300 mV

65 nsec

4 mW

TEMPERATURE RANGE

PACKAGE

Four-input gate for OR, NOR, AND or NAND gate functions. Fan-in capacity can be increased by use with the 9921 Gate Expander. SUPPLY VOLTAGE 3.0 volts ±10%

-55°C to +125°C (21)

Flat-Pack (3F) (5B)

3.6 volts ±10%

TO-5 0°C to + 70°C (29)

Logic Diagram

Schematic

ELEMENT TYPE Half-Adder NOISE IMMUNITY (TYP., 25°C)

300 mV

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C)

70 nsec

(TYP., 25°C)

8 mW

FAN-OUT

4

DESCRIPTION

Two-level AND-OR gate with added output inverter for use as complete half-adder, exclusive OR gate, or any similar logic construction.

Logic Diagram

SUPPLY VOLTAGE 3.0 volts ±10%

3.6 volts ±10%

TEMPERATURE RANGE

-55°C to +125°C (21)

0°C to + 70°C (29)

PACKAGE

Flat-Pack (3F) TO-5 (5B)

ELEMENT TYPE

Type D Flip-Flop

NOISE IMMUNITY (TYP., 25°C)

300 mV

(TYP., 25°C)

~~~

70 nsec

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C)

Schematic

12 mW

FAN-OUT

3

DESCRIPTION

PART

9913

NUMBER

Complete, general purpose gated storage element suitable for shift registers, counters, and control circuitry.

Logic Diagram

SUPPLY VOLTAGE

3.0 volts ±10%

3.6 volts ±10%

TEMPERATURE RANGE

-55°C to +125°C (21)

0°C to + 70°C (29)

PACKAGE

Flat-Pack (3F) TO-5 (5B)

Schematic

# LOW POWER RESISTOR-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

NUMBER

ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

(TYP., 25°C)

PROPAGATION DELAY POWER DISSIPATION (TYP., 25°C)

FAN-OUT

9921

Gate Expander

300 mV

35 nsec

PACKAGE

TO-5

DESCRIPTION

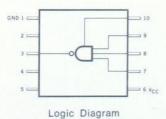

Dual two-input gate without resistors, used to increase fan-in capability of gate circuits.

SUPPLY VOLTAGE  $3.0 \text{ volts } \pm 10\%$

TEMPERATURE RANGE -55°C to +125°C (21)

Flat-Pack (3F)

(5B)

3.6 volts ±10%

0°C to + 70°C (29)

Logic Diagram

Schematic

PART NUMBER ELEMENT TYPE

NOISE IMMUNITY (TYP., 25°C)

PROPAGATION DELAY (TYP., 25°C)

POWER DISSIPATION

FAN-OUT

9938

Dual Buffer

300 mV

70 nsec

(TYP., 25°C) 20 mW

30/buffer

DESCRIPTION

Dual two-input low-impedance inverting driver circuit. Can supply more output current than the basic  $RT_{\mu}L$  circuit, for use as a line driver, astable or monostable multivibrator, or pulse differentiator.

Logic Diagram

SUPPLY VOLTAGE

3.0 volts ±10%

3.6 volts  $\pm 10\%$

TEMPERATURE RANGE

-55°C to +125°C

0°C to + 70°C

PACKAGE

Flat Pack TO-5

PART NUMBER

9940

ELEMENT

J-K Flip-Flop

NOISE IMMUNITY (TYP., 25°C)

300 mV

PROPAGATION DELAY (TYP., 25°C)

80 nsec

POWER DISSIPATION (TYP., 25°C)

12 mW

**FAN-OUT**

3

PACKAGE

DESCRIPTION

Complete, general purpose storage element suitable for use in shift registers, counters, or binary control functions.

Logic Diagram

SUPPLY VOLTAGE

$3.0 \text{ volts } \pm 10\%$

3.6 volts ±10%

TEMPERATURE RANGE

-55°C to +125°C

Flat Pack

TO-5

# TOTAL CAPABILITY COUNTING MICROLOGIC® INTEGRATED CIRCUITS

Fairchild Counting Micrologic® integrated circuits are a compatible family of integrated circuits designed for various types of counting and allied applications.

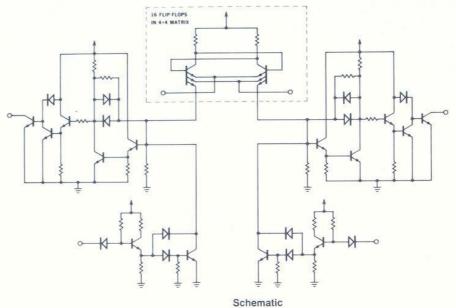

The  $C_\mu L$  family compresses all of the circuit components of a printed circuit card into the space formerly occupied by a single transistor. Functionally, however, it is equivalent to four flip-flops and at least one logic gate. Counting microcircuits offer the advantages of reliability, small size, and low power consumption at prices that are difficult to meet with discrete components and impossible with other integrated circuit approaches.

The 9958 and 9989 are both complete counters in themselves; the other members of the family provide storage and decoding capabilities.

# (25°C Free Air Temperature)

| Maximum voltage at pin 7 (0°C to +75°C) | +6.0 volts             |

|-----------------------------------------|------------------------|

| Count Input Pin<br>Voltage              | +4.0 volts, -2.0 volts |

| Reset Input Pin<br>Voltage              | +4.0 volts, -2.0 volts |

| Current into Each Output Terminal       | ±5.0 mA                |