INTEL CORPORATION, 3065 Bowers Avenue, Santa Clara, California 95051 • [408] 246-7501

# MICRO COMPUTER SET

USERS MANUAL

FEBRUARY 1973

REV 4

© lotal 1972

# MCS-4

### FOUR-BIT PARALLEL MICRO COMPUTER SET

#### **Features**

- Microprogrammable General Purpose Computer Set

- 4-Bit Parallel CPU With 45 Instructions

- Instruction Set Includes Conditional Branching, Jump to Subroutine and Indirect Fetching

- Binary and Decimal Arithmetic Modes

- Addition of Two 8-Digit Numbers in 850 Microseconds

- 2-Phase Dynamic Operation

- 10.8 Microsecond Instruction Cycle

- CPU Directly Compatible With MCS-4 ROMs and RAMs

- Easy Expansion One CPU can Directly Drive up to 32,768 Bits of ROM and up to 5120 Bits of RAM

- Unlimited Number of Output Lines

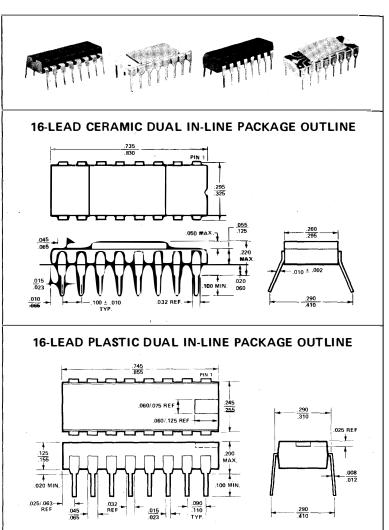

- Packaged in 16-Pin Dual In-Line Configuration

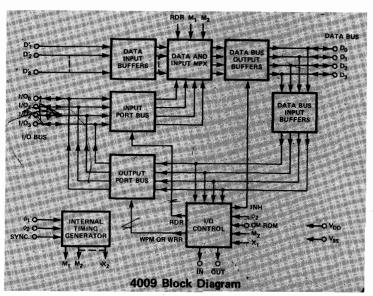

MCS-4 CAPABILITIES ARE EXPANDED BY THE ADDITION OF THE 4008/4009, THE STANDARD MEMORY AND I/O INTERFACE SET.

#### **Expanded Features**

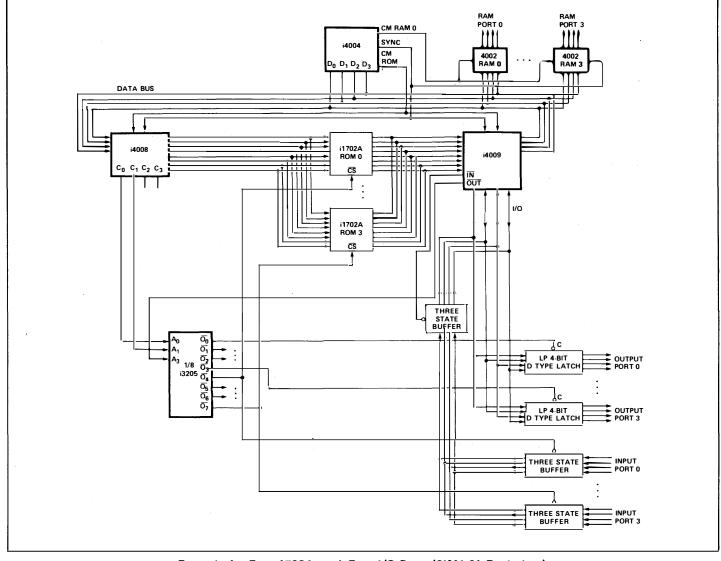

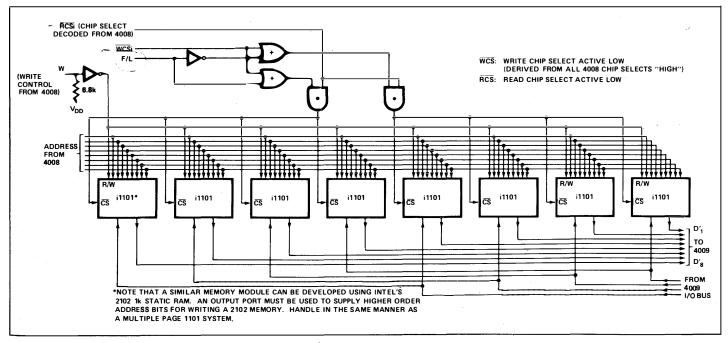

- Directly Compatible With 4004 CPU

- Interface 1702A PROMs Directly to 4004 CPU -- Completely Eliminates TTL Interface

- Permits Program Storage in Alterable Memory

- Execute MCS-4 Programs from any Mix of Standard Intel PROMs, ROMs and RAMs

- Expanded I/O Po. \* Capability

- Each Port May be Both Input and Output -- Up to 16 4-bit Input Ports and 16 4-bit Output Ports

- Number of I/O Ports is Independent of the Size of the Program Memory

- I/O Ports and Control Lines are TTL Compatible

- New Instruction WPM (Write Program Memory) is Used for Loading Alterable Program Storage (RAM)

#### **CONTENTS**

|              |                                                                                            | Pag  |

|--------------|--------------------------------------------------------------------------------------------|------|

| I.           | Introduction                                                                               |      |

|              | A. General Discussion  B. Applications for the MCS-4 Micro Computer Set                    | . 2  |

|              | C. Features of the MCS-4                                                                   |      |

| II.          | MCS-4 System Description                                                                   | . 4  |

|              | A. General Description                                                                     | . 4  |

|              | B. Basic System Operation C. MCS-4 Logic Definitions                                       |      |

|              | D. Basic System Timing                                                                     |      |

| III.         | 4 Bit Central Processor Unit (CPU) — 4004                                                  | . 7  |

|              | A. Description B. CPU Instruction Set Format, Index Register Organization and              |      |

|              | Operation of the Address Register and Command Lines                                        |      |

|              | 1. Instruction Set Format                                                                  |      |

|              | 3. Operation of the Address Register 4. Operation of the Command Lines and the SRC Command |      |

|              | 4. Operation of the Command Lines and the SRC Command                                      | . 13 |

| 157          | C. Basic Instruction Set                                                                   |      |

| IV.          | 4001-256 x 8 Mask Programmable ROM and 4 Bit I/O Port                                      |      |

| V.           | 4002-320 Bit RAM and 4 Bit Output Port                                                     |      |

| VI.          | 4003-10 Bit Serial In/Parallel-Out, Serial Out Shift Register                              |      |

| VII.         | Detailed Instruction Repertoire of the MCS-4                                               |      |

|              | A. Instruction Format                                                                      |      |

|              | B. Symbols and Abbreviations C. Format for Describing Each Instruction                     |      |

|              | D. One-word Machine Instructions                                                           |      |

|              | E. Two-word Machine Instructions                                                           |      |

|              | F. Input/Output and RAM Instructions                                                       |      |

| <i>/</i> 111 | An Introduction to Programming the MCS-4                                                   |      |

| VIII.        |                                                                                            |      |

| IX.          | Programming Examples                                                                       |      |

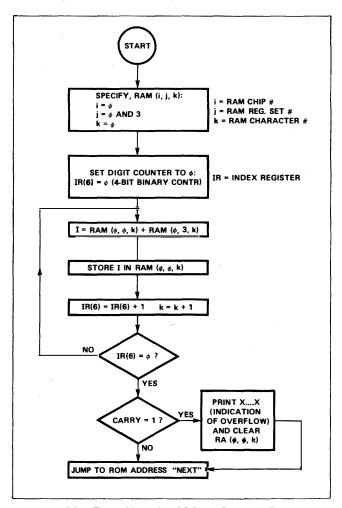

|              | A. MCS-4 Program Routine Format Notes  B. 16-Digit Decimal Addition Routine                |      |

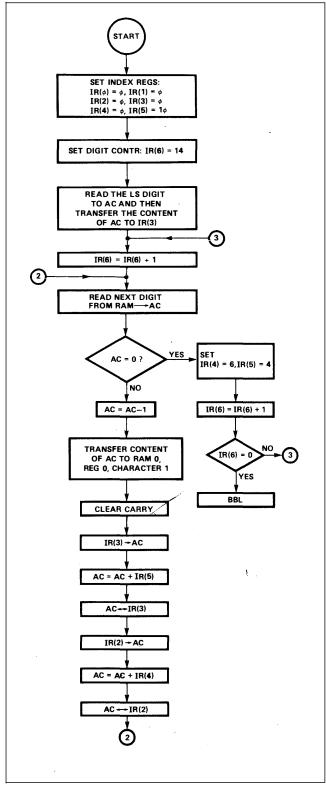

|              | C. BCD to Binary Conversion                                                                |      |

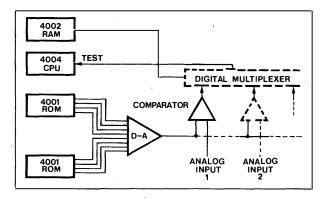

|              | D. A-D Converter Using DAC with MCS-4                                                      |      |

| X.           | E. MCS-4 Software and Firmware Library  Interface Design for the MCS-4 System              |      |

| ^.           | A. General Discussion                                                                      |      |

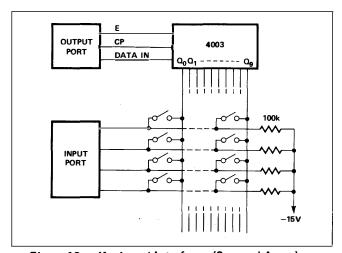

|              | B. Keyboards                                                                               |      |

|              | C. Display                                                                                 | . 53 |

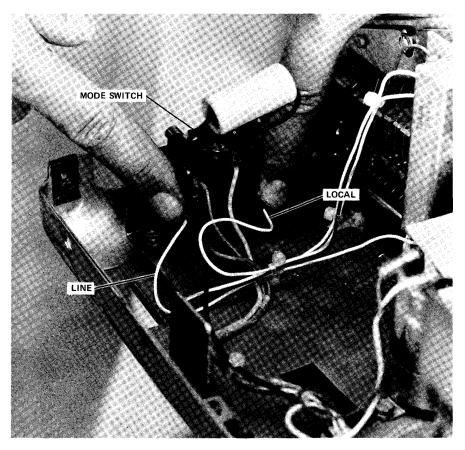

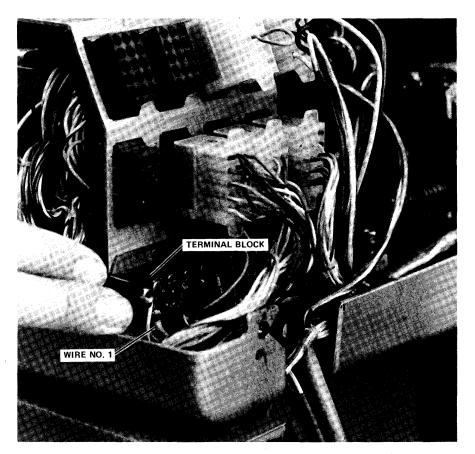

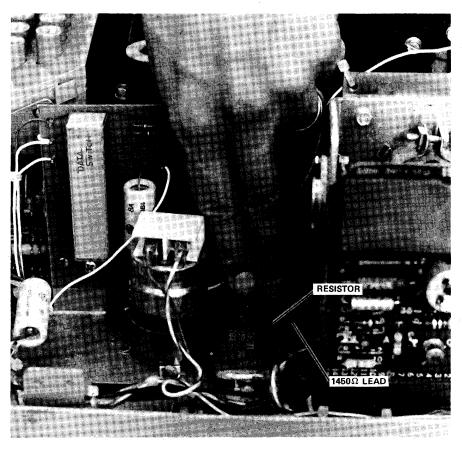

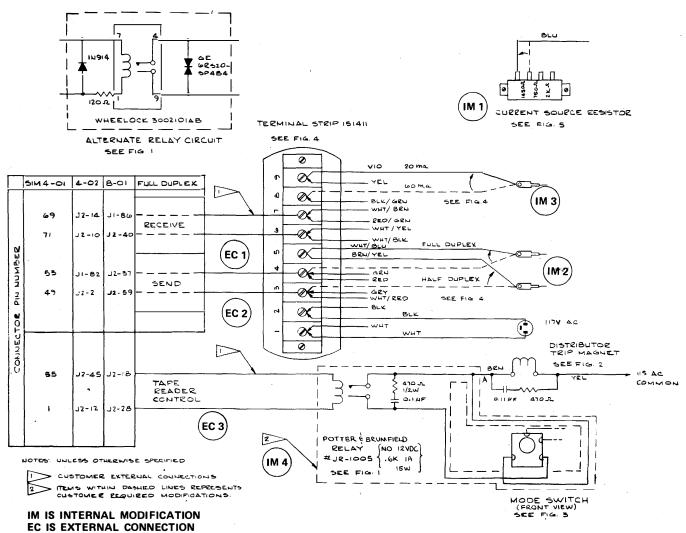

|              | D. Teletype Interface                                                                      |      |

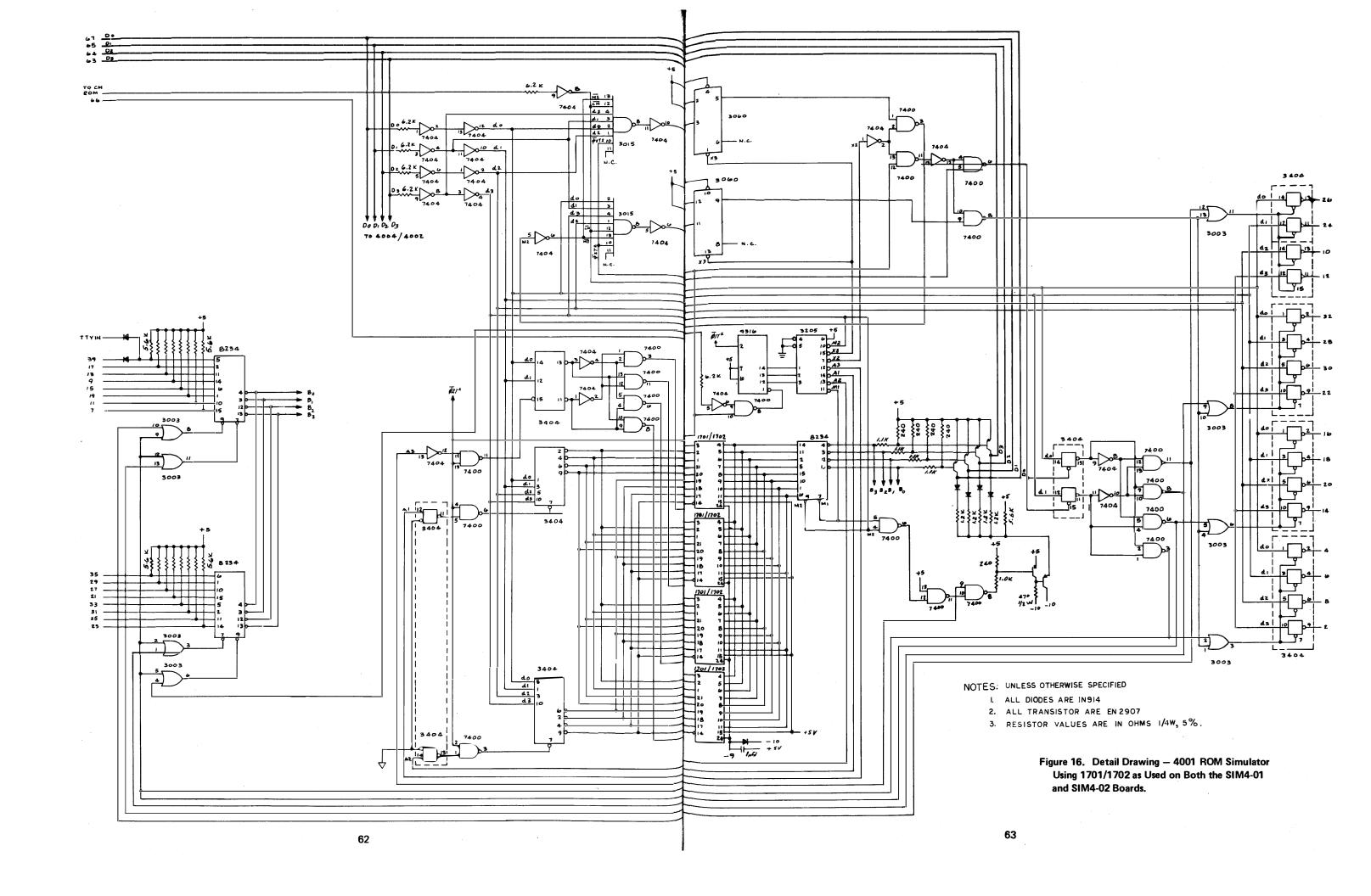

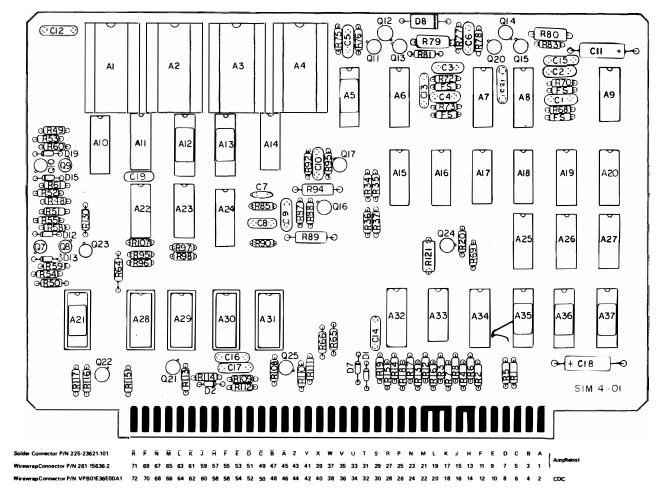

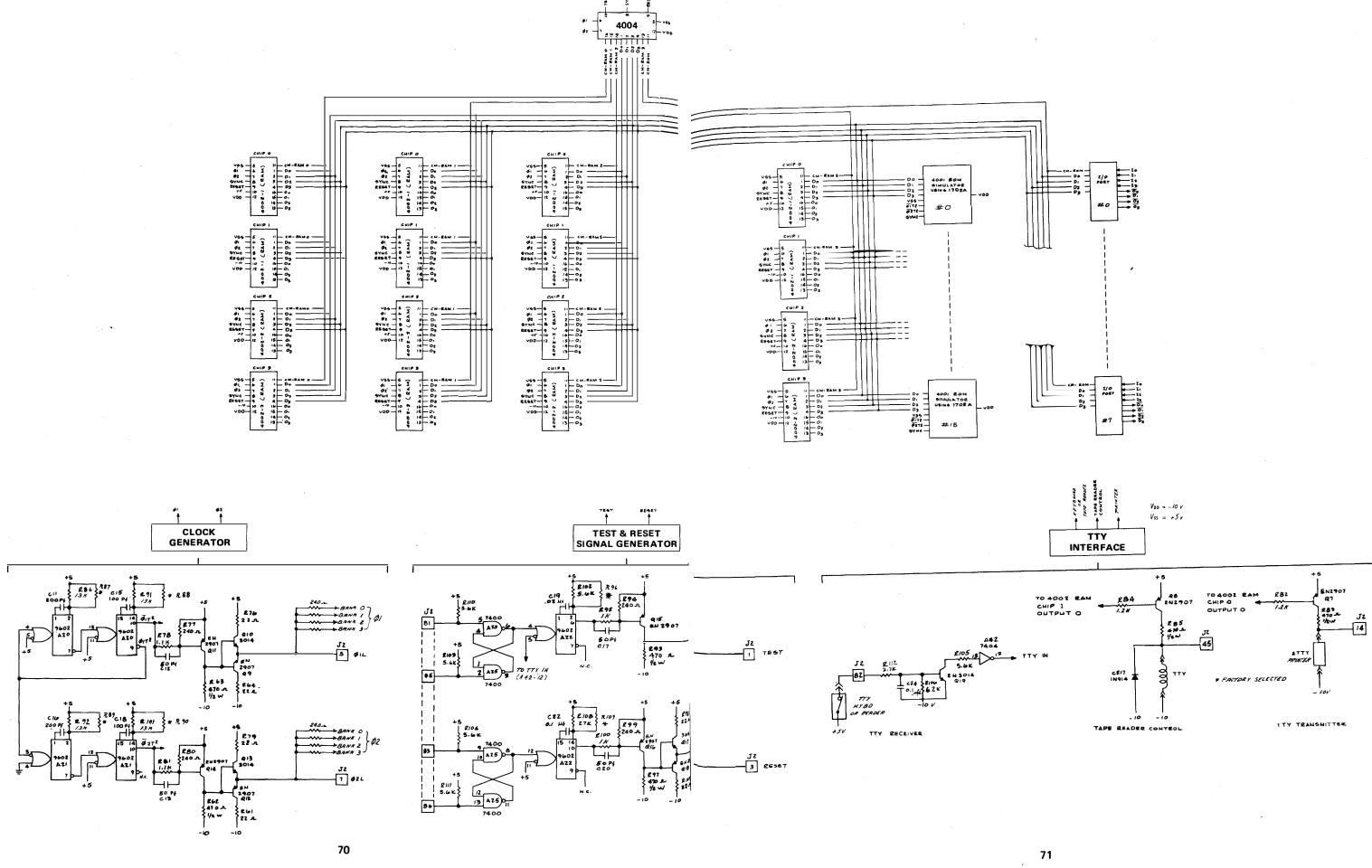

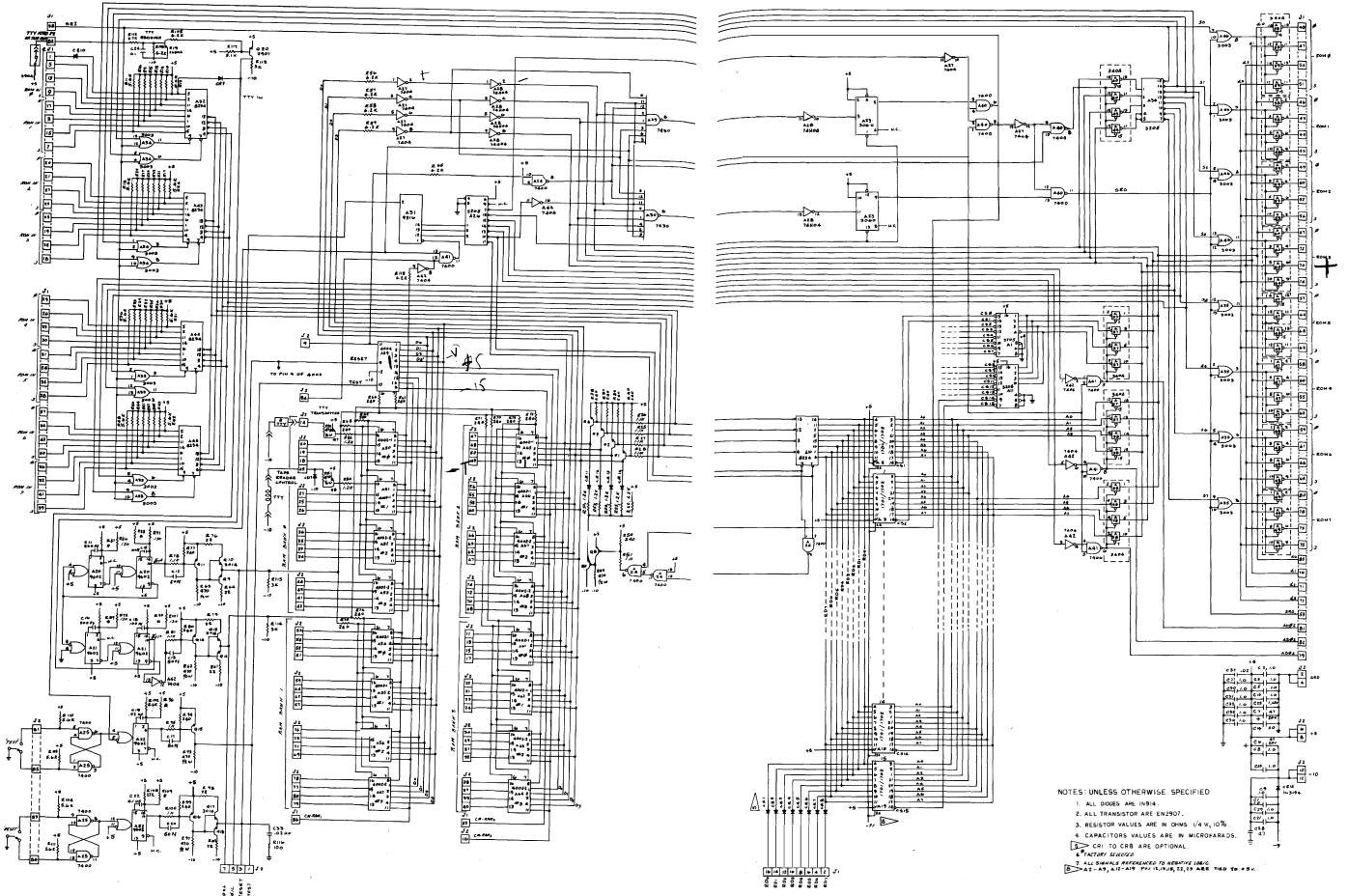

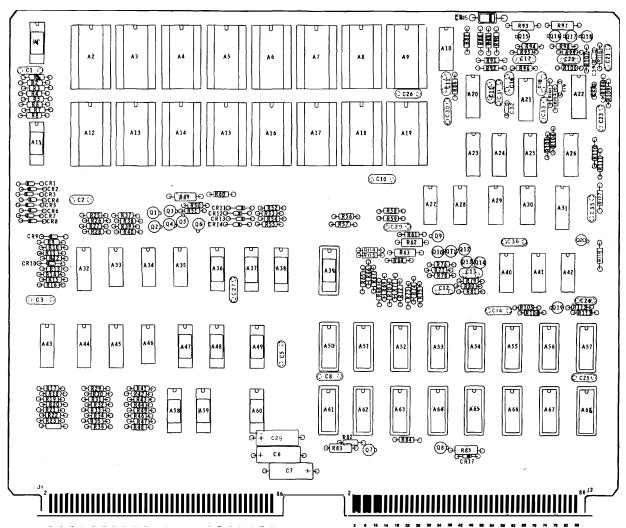

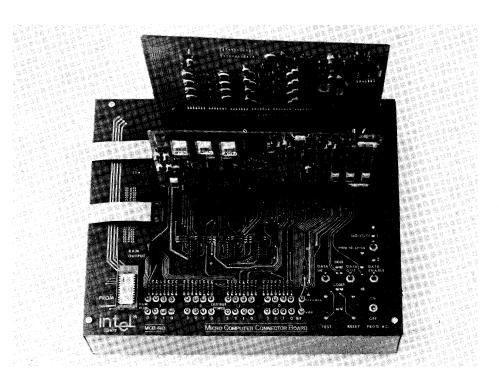

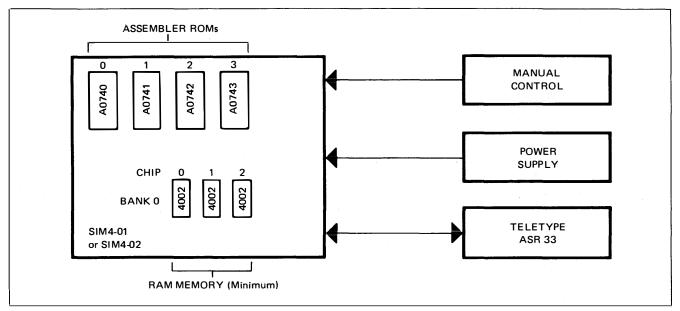

| XI.          | SIM4-01/SIM4-02 Prototyping System                                                         |      |

|              | A. General System Description                                                              |      |

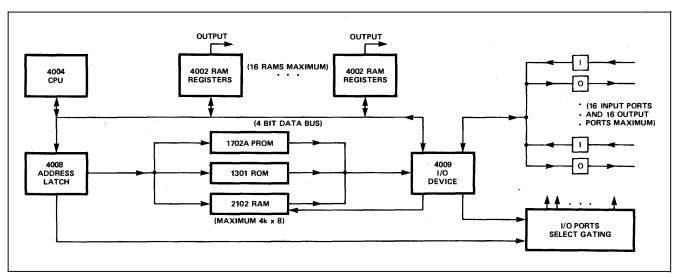

|              | B. SIM4-01/SIM4-02 Specifications C. MCS-4 Standard Memory and Interface Set (4008/4009)   |      |

|              | D. SIM4-01 Prototype System                                                                | . 64 |

|              | E. SIM4-02 Prototype System                                                                | . 70 |

| XII.         | Sample Sixteen Digit Decimal Addition Program (Intel ROM Program Number A0700)             |      |

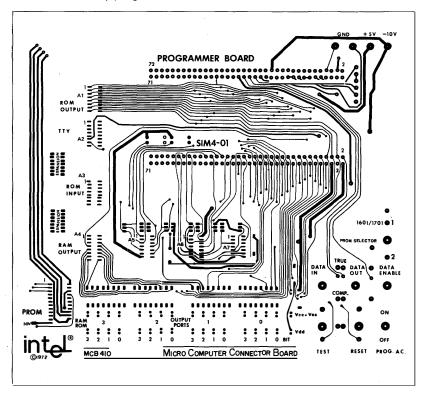

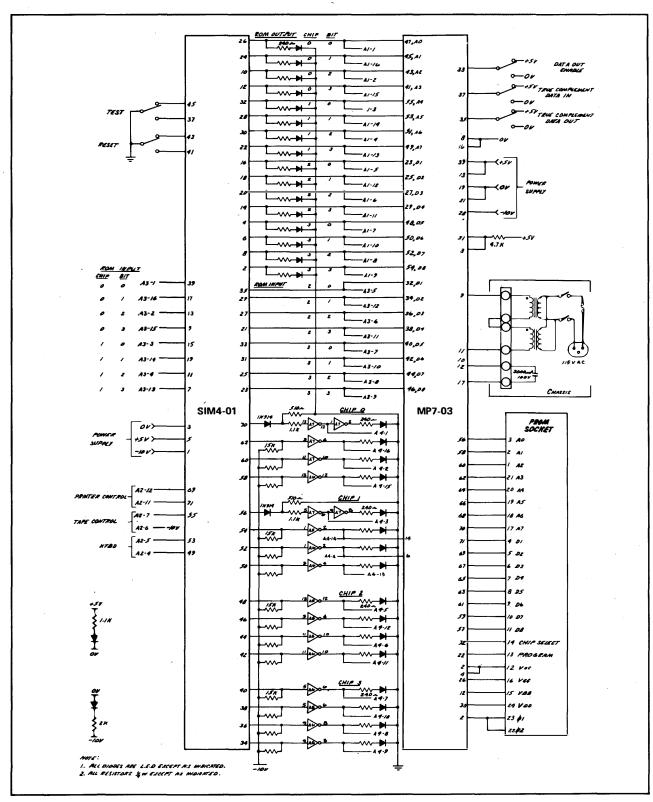

| XIII.        | MCS-4 PROM Programming System                                                              |      |

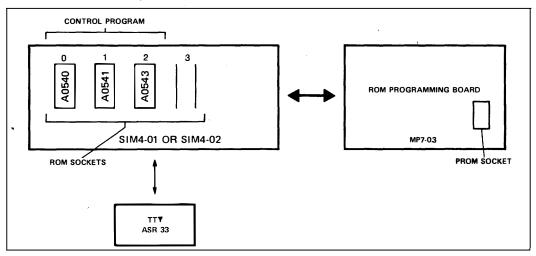

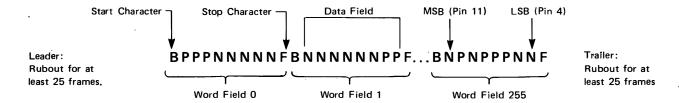

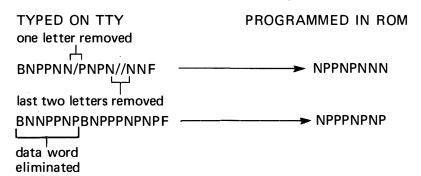

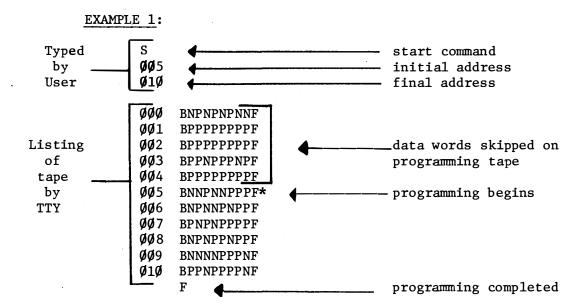

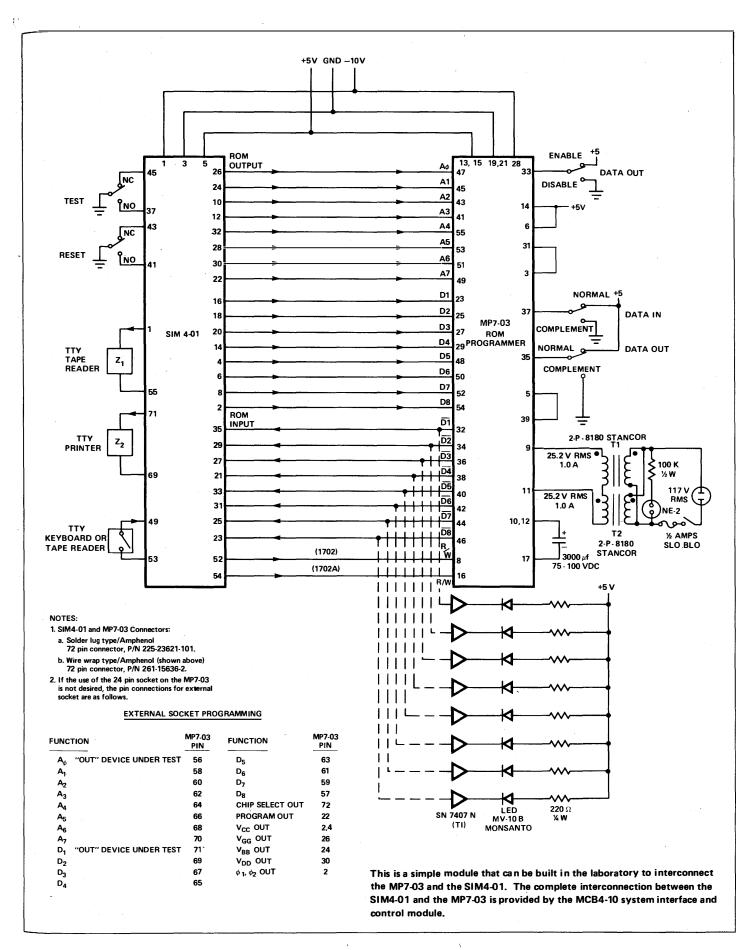

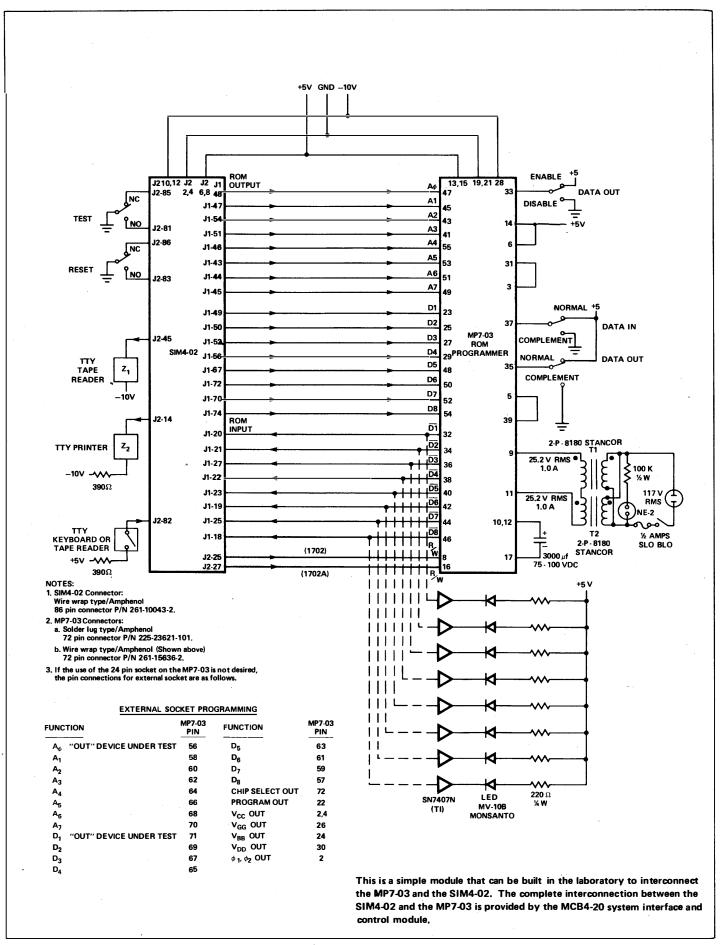

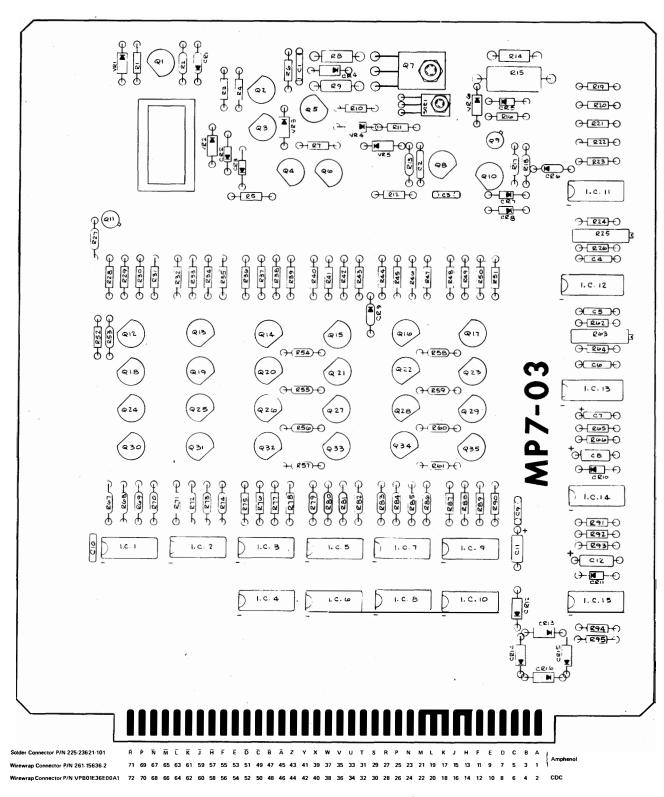

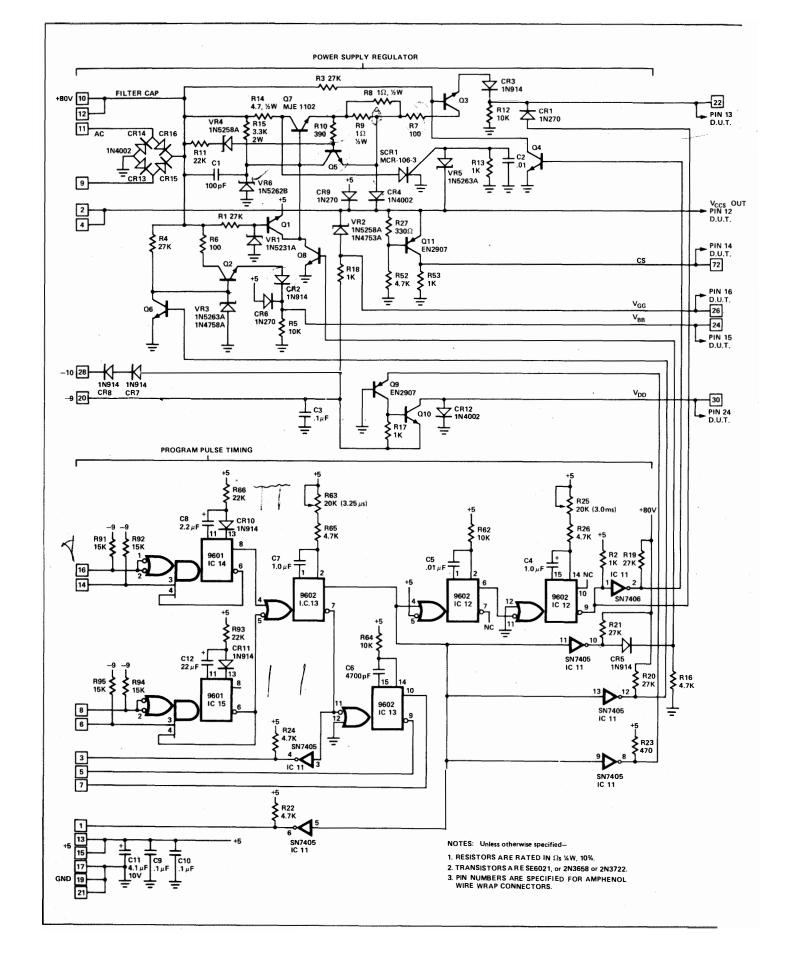

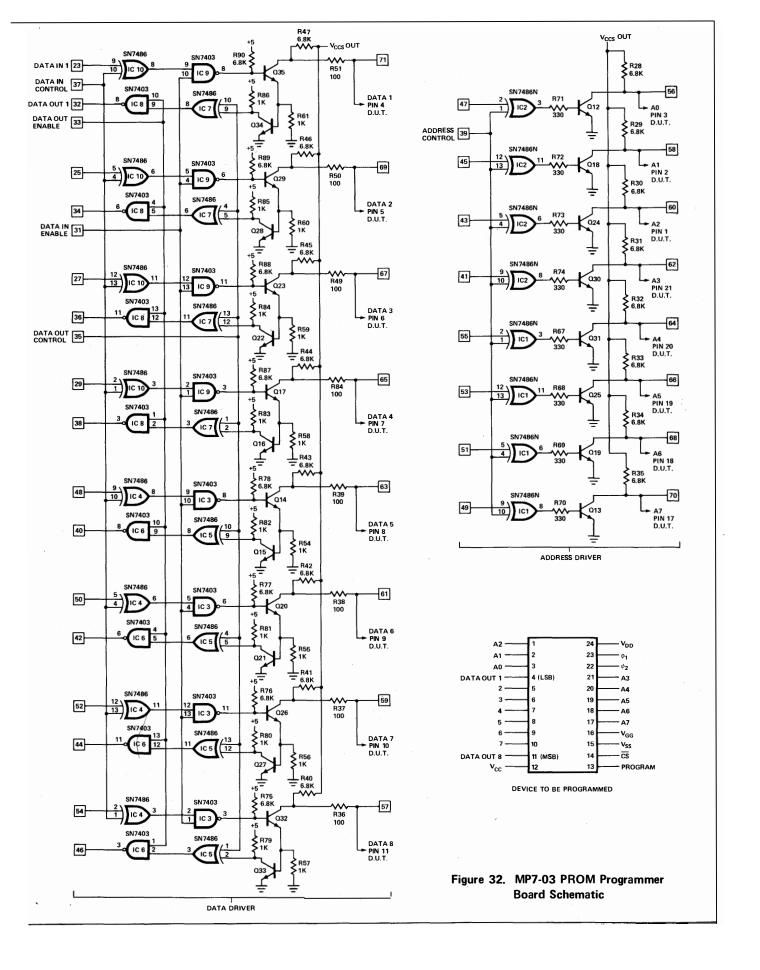

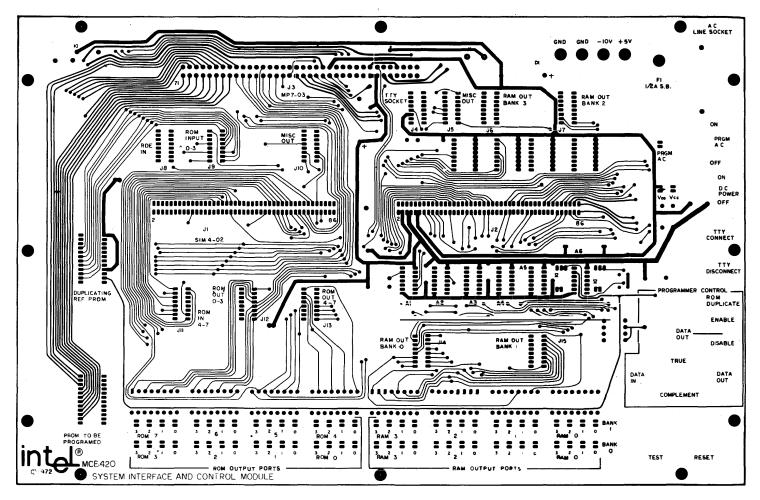

|              | A. General System Description and Operating Instructions B. MP7-03 Programming System      | . 89 |

| XIV.         | MCS-4 Evaluation Kit Using the 4001-0009                                                   | . 96 |

| XV.          | Appendices                                                                                 | 102  |

|              | A. Electrical Characteristics of the MCS-4                                                 |      |

|              | B. System Applications of the 4008/4009                                                    |      |

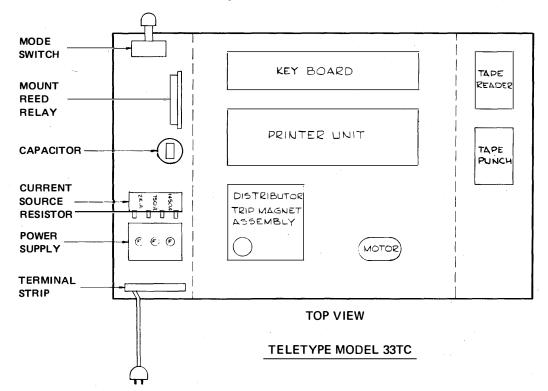

|              | D. Teletype Modifications for SIM4-01/SIM4-02                                              |      |

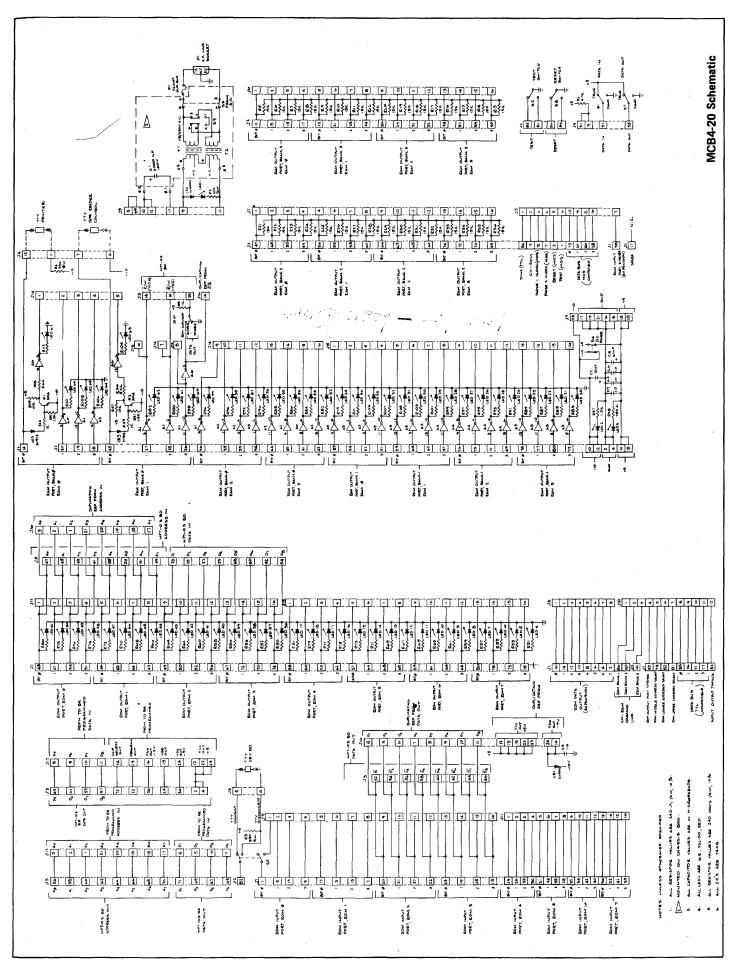

|              | E. System Interface and Control Modules - MCB4-10/MCB4-20                                  | 121  |

|              | F. SIM4 Hardware Assembler for SIM4-01 or SIM4-02 G. SIM4 Hardware Simulator               |      |

|              | H. MCS-4 Fortran Assembler/Simulator Software Package                                      |      |

|              | I. MCS-4 Programming Examples                                                              |      |

| XVI.         | Ordering Information                                                                       | 172  |

|              | A. Sales Offices                                                                           |      |

|              | B. Distributors                                                                            |      |

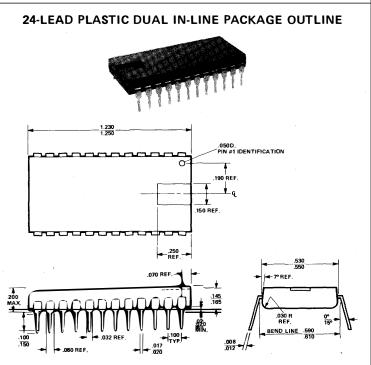

|              | C. Ordering Information/Packaging Information                                              | 1/4  |

NOTICE: The circuits contained herein are suggested applications only. Intel Corporation makes no warranties whatsoever with respect to the completeness, accuracy, patent or copyright status, or applicability of the circuits to a user's requirements. The user is cautioned to check these circuits for applicability to his specific situation prior to use. The user is further cautioned that in the event a patent or copyright claim is made against him as a result of the use of these circuits, Intel shall have no liability to user with respect to any such claim.

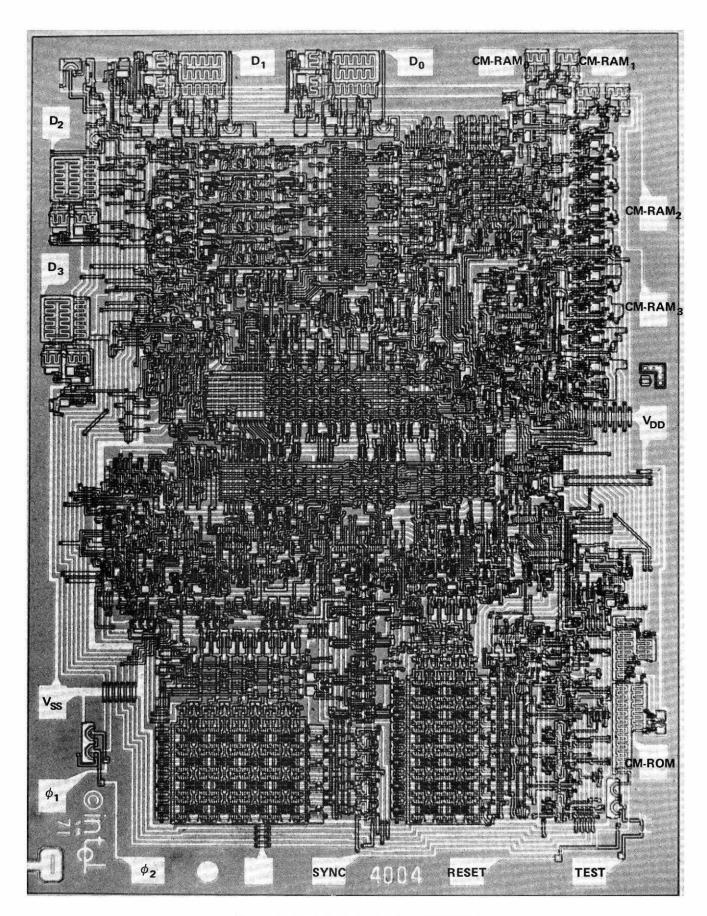

4004 Photomicrograph With Pin Designations

#### INTRODUCTION — THE ALTERNATIVE TO RANDOM LOGIC SYSTEMS

#### A. General Discussion

Since its inception, digital computer applications have evolved from calculation through data processing and into control. The development of the minicomputer has vastly increased the scope of computer usage. In particular, the use of minicomputers in dedicated applications has had a profound effect on systems design.

Many engineers have found having a minicomputer at the heart of a system offers significant advantages. Minicomputer systems are more flexible, can be easily personalized for a particular customer's requirements, and can be more easily changed or updated than fixed-logic design systems. For most designers, the programming of a minicomputer is a much easier and more straightforward procedure than designing a controller with random logic.

Unfortunately, the size and cost of even the smallest minicomputer has limited its use to relatively large and costly systems. This has resulted in many smaller systems being implemented with complicated random logic. INTEL NOW OFFERS ANOTHER ALTERNATIVE. . . THE MCS-4 MICRO COMPUTER SET.

This new concept in LSI technology makes the power of a general purpose computer available to almost every logic designer and represents a strong attack on the dependency of systems manufacturers on complicated random logic systems. This component computer from Intel can provide the same arithmetic, control and computing functions of a minicomputer in as few as two 16 pin DIP's and costs nearly 2 orders of magnitude less.

The set is not designed to compete with the minicomputer, but rather to extend the power of the concept into new ranges of applications. For example, many systems now built of SSI and MSI TTL can now be implemented with a totally self-contained system built around this set of devices.

Heart of each system is a single chip central processor unit (CPU) which performs all control and data processing functions. Auxiliary to the CPU are ROM's which store microprograms and data tables; RAM's which store data and instructions, and Shift Registers which can expand the I/O capacity of the system. The MCS-4 system communicates with circuits and devices outside the family through "ports" provided on each RAM and ROM.

A system using this set of devices will usually consist of one CPU, from one to 16 ROM's, up to 16 RAM's and an arbitrary number of SR's. A minimum system could be designed with just one CPU and one ROM. With these components, you can build distributed computers, dedicated computers, or personalized computers and utilize the almost infinite combinations of microprogramming. The designer buys standard devices, and with microprogramming of the ROM fulfills his own unique circuit requirements.

The three major advantages of Intel microcomputers:

Great system flexibility, with easy program changes, ability to expand or shrink the system, and small size and low power.

Expediency of design, because ROM programming is easier than random circuit design, system checkout is easier using electrically programmable and erasable ROM's, and ability to insert new microprograms helps prevent system obsolescence.

Manufacturing economies come from simple DIP package design, automatic insertion, lower labor costs, lower inventory of parts and boards.

When designing with random logic (logic gates, flip flops, etc.), the designer will usually start with a description of the desired function and attempt to wire counters, gates, etc. to achieve this function. Switches, displays, etc. are also connected to the logic. To correct errors or make changes in a design usually requires significant changes in wiring, often requiring that circuit boards be scrapped and replaced by new ones.

To do the same design with the MCS-4 Micro Computer Set, the designer again starts with the functional description. However, he implements these functions by encoding suitable sequences of instructions in ROM. The MCS-4 instruction set is quite complete and allows a wide variety of functions to be performed: decimal or binary arithmetic, counting, decisions, table-lookup, etc. Switches, displays, etc. are connected to the system via the input and output ports.

As a result of this organization, almost the entire logic, the entire "personality" of the machine is determined by the instructions in ROM. Very significant modifications of machine characteristics can be made by changing or adding ROM's without making any changes in wiring or circuit boards.

Thus the set offers tremendous flexibility of design and allows the user to have many of the desirable features of a custom MOS LSI design—small package count, a set of components which is uniquely his own (for each user's program routines are his proprietary property)—and yet have none of the disadvantages of long development cycle, high development costs, etc. The short design cycle and flexibility associated with ROM programming allows much more rapid response to market demands than is possible with custom LSI and thus provides insurance against obsolescence.

#### B. Applications for the MCS-4 Micro Computer Set

Heart of the MCS-4 micro computer set is the 4004 CPU. This device has a powerful and versatile instruction set which allows the system to perform a wide variety of arithmetic, control and decision functions. The microprograms stored in the ROM devices give the designer the power of designing custom computers with standard components. You can

use the MCS-4 almost anywhere. Here are a few examples:

Control Functions - Because of low initial cost and flexibility of programming, the MCS-4 can be used in place of random logic in systems such as those in process control, numeric controls, elevator controls, highway and rail traffic controls. By changing ROM microprograms the whole system can easily be modified and updated.

<u>Computer Peripherals</u> - The system can be conveniently used in peripheral equipment to control displays, keyboards, printers, readers, plotters and to give intelligence to terminals.

Computing Systems - The MCS-4 system is ideally suited for such devices as billing machines, cash registers, point of sale terminals and accounting machines. For example, the adding of two 8-digit numbers can be done in 850 microseconds. In addition, the MCS-4 can be efficiently used to decentralize central computer functions.

Other Applications - The elements of the MCS-4 have many applications within transportation, automotive, medical electronics and test systems, where inexpensive dedicated computers can improve system performance.

#### C. Features of the MCS-4

- 4-bit parallel CPU with 45 instructions

- Decimal and binary arithmetic modes

- 10.8 µs instruction cycle

- Addition of Two 8-digit numbers in 850 usec.

- Sixteen 4-bit general purpose registers

- Nesting of subroutines up to 3 levels

- Instruction Set includes conditional branching, jump to subroutine, and indirect fetching

- 2-phase dynamic operation

- Synchronous operation with memories

- Direct compatibility with 4001, 4002 and 4003

- No interface circuitry to memory and I/O required

- Directly drives up to: 4K by 8 ROM (16 4001's)

1280 by 4 RAM (16 4002's) 128 I/O lines (without 4003)

Unlimited I/O (with 4003's)

- Memory capacity expandable through bank switching

- 16-pin DIP package

- P-channel Silicon Gate MOS

- Minimum system: CPU and one ROM

#### II. MCS-4 SYSTEM DESCRIPTION

#### A. General Description

Each MCS-4 circuit constitues a basic standard building block which allows the design of many different types of systems which can be fabricated using the same parts. The only custom part is the ROM chip which will store a microprogram defined by the user and requires a metal mask option for each new program.

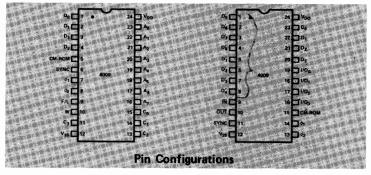

The MCS-4 micro computer set consists of the following 4 chips, each packaged in a 16 pin DIP package:

- (1) A Central Processor Unit Chip -CPU 4004

- (2) A Read Only Memory Chip ROM 4001

- (3) A Random Access Memory Chip RAM 4002

- (4) A Shift Register Chip SR 4003

The CPU contains the control unit and the arithmetic unit of a general purpose microprogrammable computer. The ROM stores microprograms and data tables, the RAM stores data and instructions, and the Shift Register is used in conjunction with I/O devices to effectively increase the number of I/O lines.

The MCS-4 set has been designed for optimum interfaceability; the CPU communicates with the RAM's and ROM's by means of a 4-line data bus ( $D_0$ ,  $D_1$ ,  $D_2$ ,  $D_3$ ). This single data bus is used for all information flow between the chips except for control signals which are sent to RAM and ROM over 5 additional lines. One CPU controls up to 16 ROM's (4K x 8 words), 16 RAM's (1280 x 4 words), and 128 I/O lines without requiring any interface circuit. With the addition of few gates up to 48 ROMS & RAMS combined and 192 I/O lines can be controlled by one CPU.

The I/O function, although different from the ROM and RAM functions, is physically located in the ROM and RAM chips. Each 4001 and 4002 has 4 I/O lines for communication with I/O devices.

- 4001-ROM The 4001 is a 2048 Bit metal mask programmable ROM providing custom microprogramming capability for the MCS-4 micro computer set. Each chip is organized as 256 x 8 bit words which can be used for storing programs or data tables. Each chip also has a 4 bit input-output (I/O) port which is used to route information to and from the data bus lines in and out of the system.

- 4002-RAM The 4002 performs two functions. As a RAM it stores 320 bits arranged as 4 registers of twenty 4-bit characters each. As a vehicle of communication with peripheral devices, it is provided with 4 output lines and associated control logic to perform output operations.

- The 4003 is a 10 bit Serial-in/parallel-out, serial-out shift register. Its function is to increase the number of output lines to interface with I/O devices such as keyboards, displays, printers, teletypewriters, switches, readers, A-D converters, etc.

4004-CPU - The 4004 is a central processor unit designed to work in conjunction with the other members of the MCS-4 micro computer set to form a completely self-contained system. The CPU communicates with the other members of the set through a four line data bus and with the peripheral devices through the RAM, ROM or SR I/O ports. The CPU chip contains 5 command control lines, four of which are used to control the RAM chips (each line can control up to 4 RAM chips for a total system capacity of 16 RAM's) and one which is used to control a bank of up to 16 ROM's.

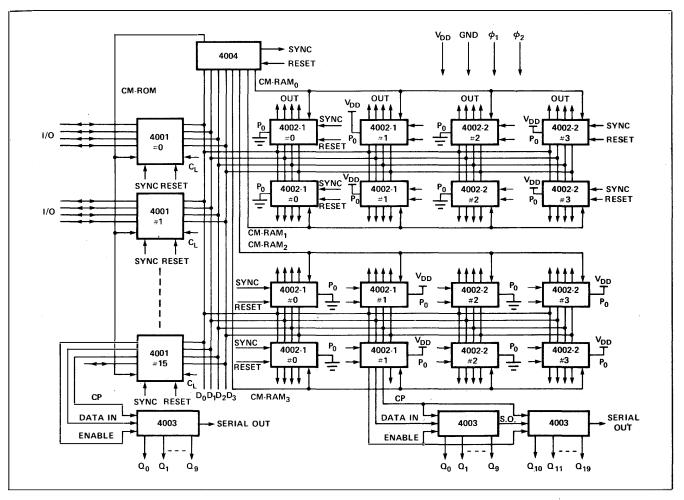

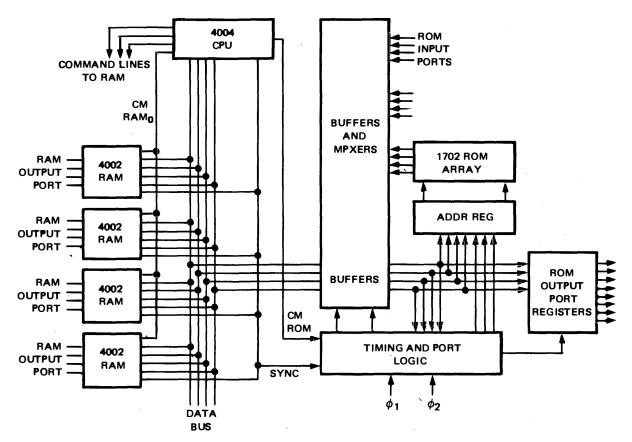

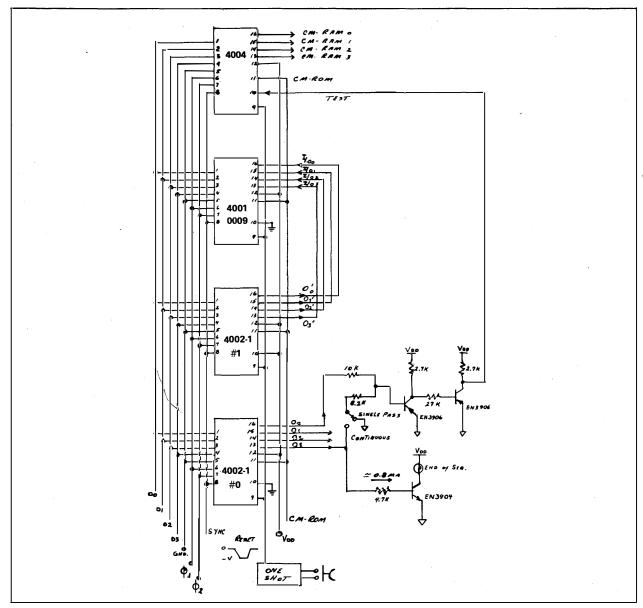

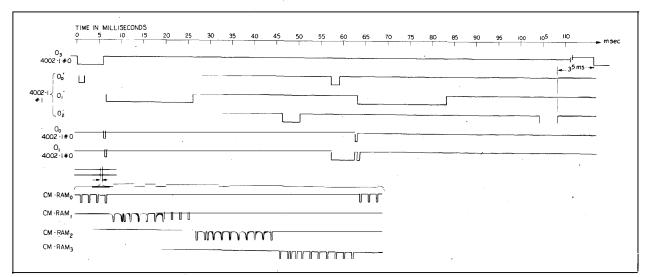

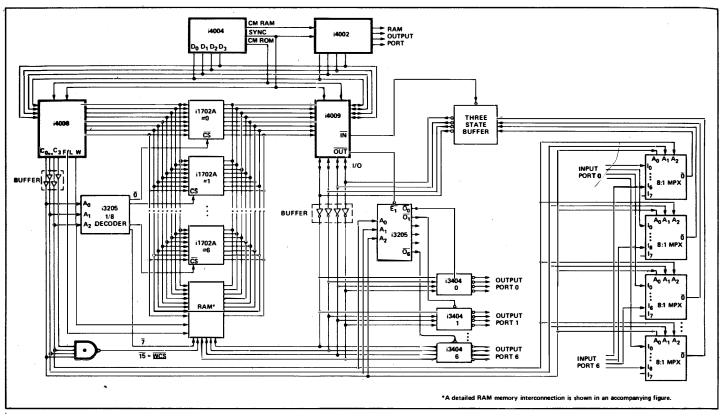

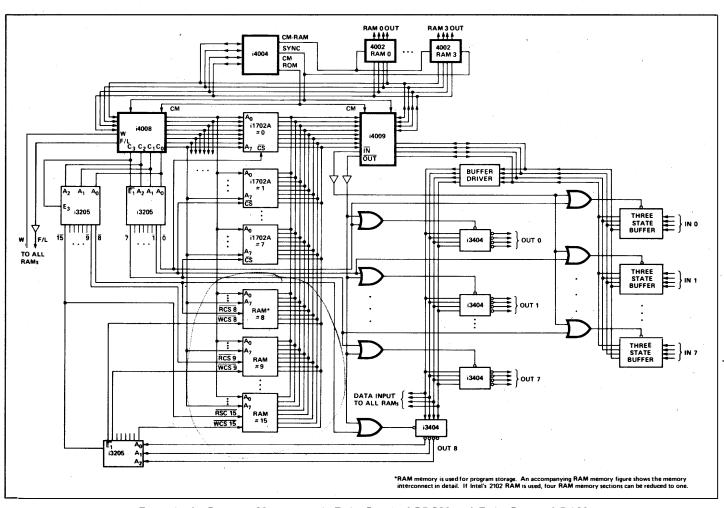

Figure 1. MCS-4 System Interconnection

#### B. Basic System Operation

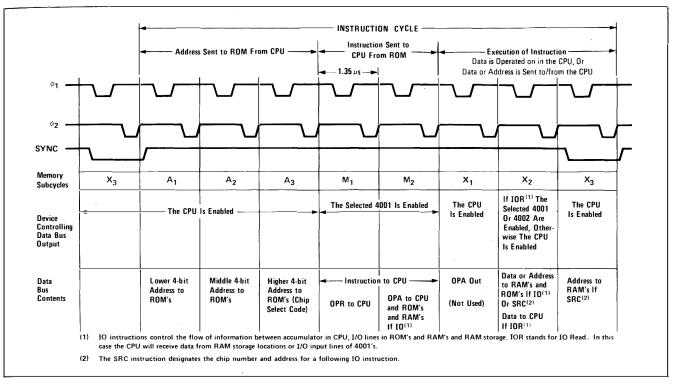

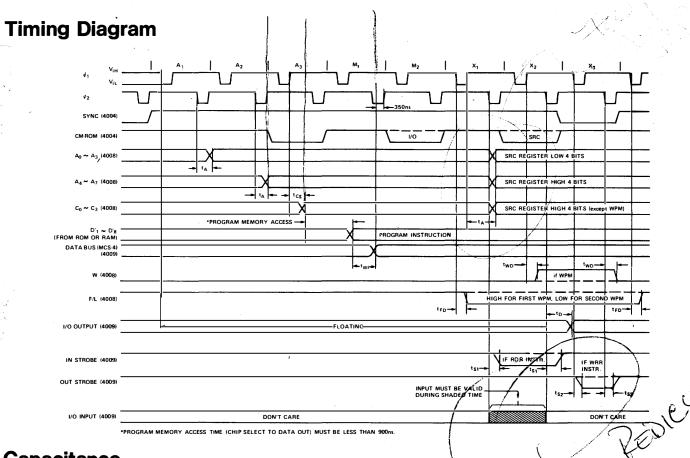

The MCS-4 uses a 10.8  $\mu$ sec instruction cycle. The CPU (4004) generates a synchronizing signal (SYNC), indicating the start of an instruction cycle, and sends it to the ROM's (4001) and RAM's (4002).

Basic instruction execution requires 8 or 16 cycles of a 750 kHz clock. In a typical sequence, the CPU sends 12 bits of address (in three 4 bit bytes on the data bus) to the ROM's in the first three cycles  $(A_1, A_2, A_3)$ . This address selects 1 out of 16 chips and 1 out of 256 8-bit words in that chip. The selected ROM chip sends back 8 bits of instruction (OPR, OPA) to the CPU in the next two cycles  $(M_1, M_2)$ . This instruction is sent over the 4 line data bus in two 4 bit bytes. The instruction is then interpreted and executed in the final three cycles  $(X_1, X_2, X_3)$ . (See Figure 2)

When an I/O instruction is received from the ROM, data is transferred to or from the CPU accumulator on the four ROM I/O lines during  $\rm X_2$  time.

A set of four RAM's is controlled by one of four command control lines from the CPU. The address of a RAM chip, register and character is stored in two index registers in the CPU and is transferred to the RAM during  $\mathbf{X}_2$ ,  $\mathbf{X}_3$  time when a RAM instruction is executed. When the RAM output instruction is received by the CPU, the content of the CPU accumulator is transferred to the four RAM output lines.

The CPU, RAM's and ROM's can be controlled by an external RESET line. While RESET is activated the contents of the registers and flip-flops are cleared. After RESET, the CPU will start from address 0 and CM-RAM is selected.

The interconnection of the MCS-4 system is shown in Figure 1. An expanded configureation is shown. The minimum system configuration consists of one CPU (4004) and one ROM (4001).

#### C. MCS-4 Logic Definitions

The MCS-4 devices operate with negative Logic. Logic "1" is defined as the low voltage (negative voltage) Level and Logic "0" is defined as the high voltage Level ( $V_{\rm SS}$ ). This definition will be used throughout the manual.

#### D. Basic System Timing

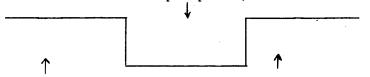

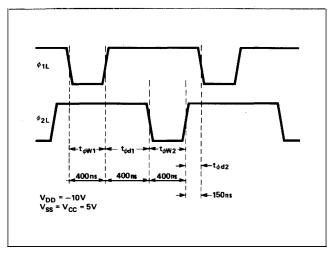

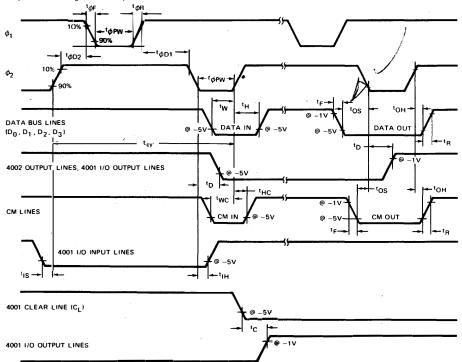

For the correct operation of the system two non-overlapping clock phases -  $\emptyset_1$ ,  $\emptyset_2$  - must be externally supplied to the 4001, 4002 and 4004.(1) The 4004 will generate a SYNC signal every 8 clock periods and will send it to the 4001's and 4002's. The SYNC signal marks the beginning of each instruction cycle. The 4001's and 4002's will then generate internal timing using SYNC and  $\emptyset_1$ ,  $\emptyset_2$ .

<sup>(1)</sup> The 4003 is a static shift register and does not use these two clocks for its operation.

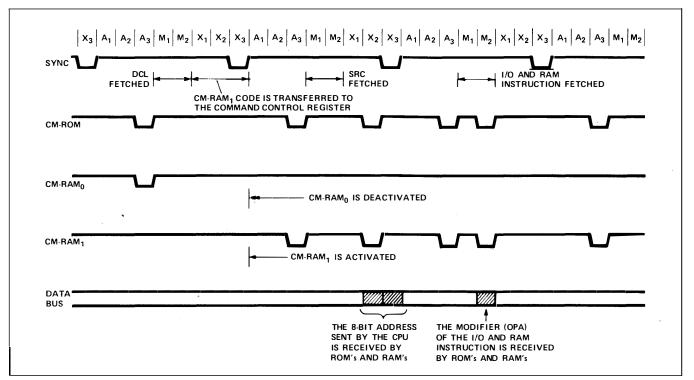

Figure 2. MCS-4 Basic Instruction Cycle

Figure 2 shows how a basic instruction cycle is subdivided and what the activity is on the data bus during each clock period. Each data bus output buffer has three possible states: "1", "0" and floating. At a given time, only 1 output buffer is allowed to drive a data line, therefore all the other buffers must be in a floating condition. However, more than 1 input buffer per data line can receive data at the same time.

#### III 4 BIT CENTRAL PROCESSOR UNIT (CPU) - 4004

#### A. Description

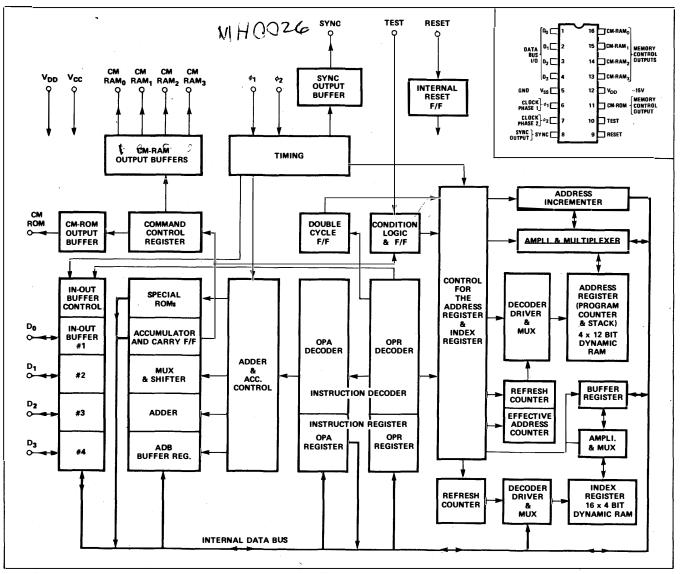

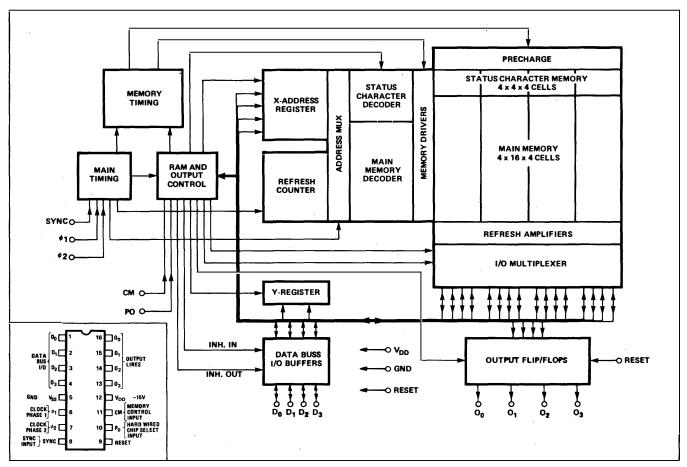

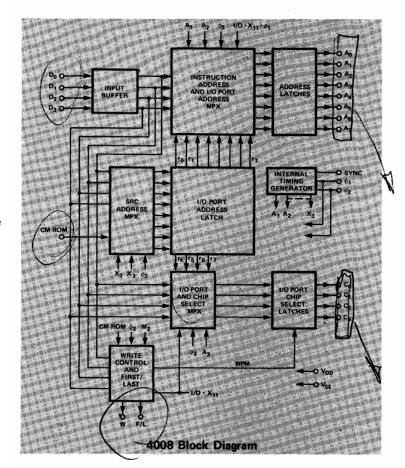

The 4004 block diagram shown in Figure 3 contains the following functional blocks:

- (1) Address register (program counter and stack organizaed as 4 words of 12 bits each) and address incrementer.

- (2) Index register (64 bits organized as 16 words of 4 bits each.

- (3) 4-bit adder.

- (4) Instruction register (8 bits wide), decoder and control.

- (5) Peripheral circuitry.

The functional blocks communicate internally through a 4-line bus and are shown in Figure 3. The function and composition of each block is as follows:

#### 1. Address Register (Program counter & Stack) & Address Incrementer

The address register is a dynamic RAM cell array of 4 x 12 bits. It contains one level used to store the instruction address (program counter) and 3 levels used as a stack for subroutine calls. The stack address is provided by the effective address counter and by the refresh counter, and it is multiplexed to the decoder.

The address when read is stored in an address buffer and is demultiplexed to the internal bus during A<sub>1</sub>, A<sub>2</sub>, and A<sub>3</sub> in three 4-bit slices (see Figure 2 for basic instruction cycle). The address is incremented by a 4-bit carry look-ahead circuit (address incrementer) after each 4-bit slice is sent out on the data bus. The incremented address is transferred back to the address buffer and finally written back into the address register.

Figure 3. 4004 CPU Block Diagram

#### 2. Index Register

The index register is a dynamic RAM cell array of 16 x 4 bits and has two modes of operation. In one mode of operation the index register provides 16 directly addressable storage locations for intermediate computation and control. In the second mode, the index register provides 8 pairs of addressable storage locations for addressing RAM and ROM as well as for storing data fetched from ROM.

The index register address is provided by the internal bus and by the refresh counter and is multiplexed to the index register decoder.

The content of the index register is transferred to the internal bus through a multiplexer. Writing into the register is accomplished by transferring the content of the internal bus into a temporary register and then to the index register.

#### 3. 4-Bit Adder

The 4-bit adder is of the ripple-through carry type. One term of the addition comes from the "ADB" register which communicates with the internal bus on one side and can transfer data or data to the adder. The other term of the addition comes from the accumulator and carry flip-flop. Both data and data can be transferred. The output of the adder is transferred to the accumulator and carry FF. The accumulator is provided with a shifter to implement rotate right and rotate left instructions. The accumulator also communicates with the command control register, special ROM's, the condition flip-flop and the internal bus. The command control register holds a 3-bit code used for CM-RAM line switching. The special ROM's perform a code conversion for DAA (decimal adjust accumulator) and KBP (Keyboard Process) instructions. The special ROM's also communicate with the internal bus. The condition logic senses ADD = 0 and ACC = 0 conditions, the state of the carry FF, and the state of an external signal (TEST) to implement JCN (jump on condition) and ISZ (increment index register skip if zero) instructions.

#### 4. Instruction Register Decoder and Control

The instruction register (consisting of the OPR Register and OPA Register each 4 bits wide) is loaded with the contents of the internal bus (at M<sub>1</sub> and M<sub>2</sub> time in the instruction cycle) through a multiplexer and holds the instruction fetched from ROM. The instructions are decoded in the instruction decoder and appropriately gated with timing signals to provide the control signals for the various functional blocks. A double cycle FF is set from any one of 5 double-length instructions. Double-length instructions are instructions whose OP-code is 16 bits wide (instead of 8 bits) and that require two system cycles (16 clock cycles) for their execution. Double length instructions are stored in two successive locations in ROM. A condition FF controls JCN and ISZ instructions and is set by the condition logic. The state of an external pin "test" can control one of the conditions in the JCN instruction.

#### 5. Peripheral Circuitry

This includes:

- a. The data bus input-output buffers communicating between data pads and internal bus.

- b. Timing and SYNC generator.

- c. 1 ROM command control (CM-ROM) and the 4 RAM command control (CM-RAM,) output buffers.

- d. Reset flip-flop.

During reset (Reset pin low), all RAM's and static FF's are cleared, and the data bus is set to "O". After reset, program control will start from "O" step and CM-RAM is selected. To completely clear all registers and RAM locations in the CPU the reset signal must be applied for at least 8 full instruction cycles (64 clock cycles) to allow the index register refresh counter to scan all locations in memory. (256 clock cycles for the 4002 RAM).

#### 6. <u>Instruction Repertoire</u>

The instruction repertoire of the 4004 consists of:

- a. 16 machine instructions (5 of which are double length)

- b. 14 accumulator group instructions

- c. 15 input/output and RAM instructions

The instruction set and its format will be briefly described in the next section. Section VII will then describe each instruction in detail.

B. CPU Instruction Set Format, Index Register Organization, and Operation of the Address Register and Command Lines

#### Instruction Set Format

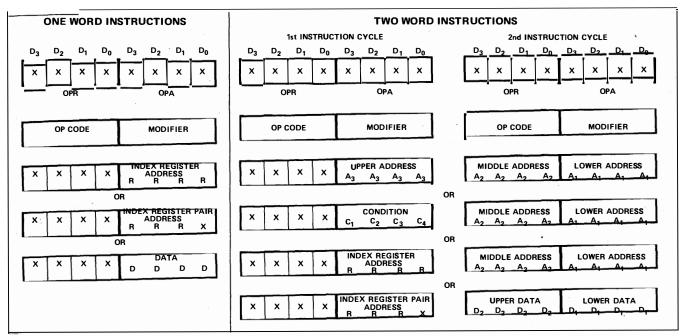

#### a. Machine Instructions

- 1-word instructions 8 bits wide and requiring 8 clock periods (1 instruction cycle)

- 2-word instructions -16 bits wide and requiring 16 clock periods (2 instruction cycles) for execution

A 1-word instruction occupies one location in ROM (each location can hold one 8-bit word) and a 2-word instruction occupies two successive locations in ROM. Each instruction word is divided into two 4-bit fields. The upper 4 bits is called the OPR and contains the operation code. The lower 4 bits is called the OPA and contains the modifier. For a single word machine instruction the operation code (OPR) contains the code of the operation that is to be performed (add, subtract, load, etc.). The modifier (OPA) contains one of 4 things:

- (1) A register address

- (2) A register pair address

- (3) 4 bits of data

- (4) An instruction modifier

For a 2-word machine instruction the 1st word is similar to a 1-word instruction, however, the modifier (OPA) contains one of 4 things:

- (1) A register address

- (2) A register pair address

- (3) The upper portion of another ROM address

- (4) A condition for jumping

Table I - Machine Instruction Format

The 2nd word contains either the middle portion (in OPR) and lower portion (in OPA) of another ROM address or 8 bits of data (the upper 4 bits in OPR and the lower 4 bits in OPA).

The upper 4 bits of instruction (OPR) will always be fetched before the lower 4 bits of instruction (OPA) during  $M_1$  and  $M_2$  times respectively. Table I illustrates the contents of each 4-bit field in the machine instructions.

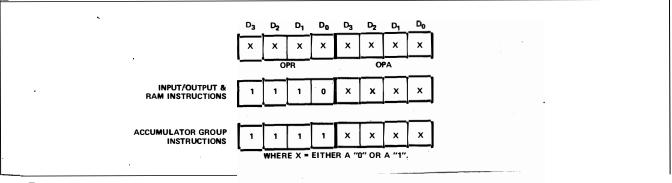

## b. Input/Output & RAM Instructions and Accumulator Group Instructions

In these instructions (which are all single word) the OPR contains a 4-bit code which identifies either the I/O instruction or the accumulator group instruction and the OPA contains a 4-bit code which identifies the operation to be performed. Table II illustrates the contents of each 4-bit field.

Table II - I/O and Accumulator Group Instruction Formats

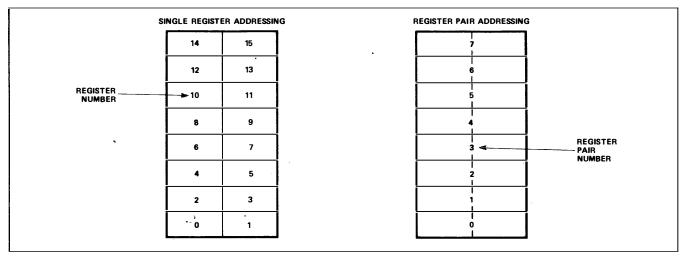

#### 2. Index Register Organization

The index register can be addressed in two modes

- a. By specifying 1 out of 16 possible locations with an OPA code of the form  ${\tt RRRR}^{(1)}$  (See Table III).

- b. By specifying 1 out of 8 pairs with an OPA code of the form  $RRRX^{(2)}$  (See Table III).

When the index register is used as a pair register, the even number register (RRRO) is used as the location of the middle address or the upper data fetched from the ROM, the odd number register (RRR1) is used as the location of the lower address or the lower data fetched from the ROM.

Table III - Index Register Organization

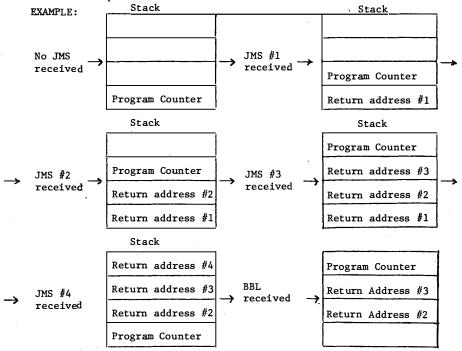

#### Operation of the Address Register (Program Counter and Stack)

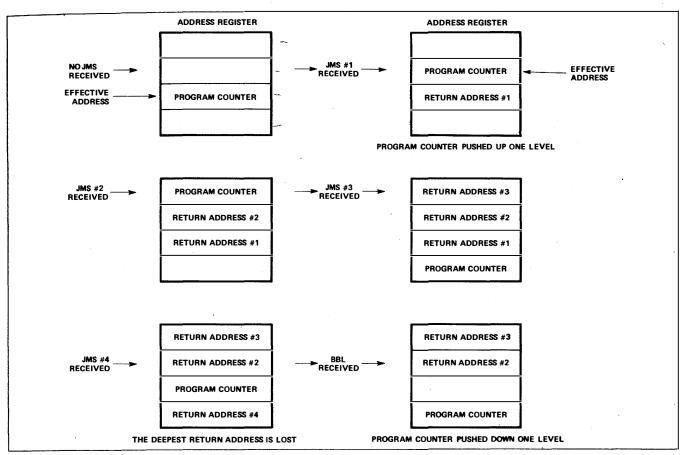

The address register contains four 12-bit registers; one register is used as the program counter and stores the instruction address. the other 3 registers make up the push down stack.

Initially any one of the 4 registers can be used as the program counter to store the instruction address. In a typical sequence the program counter is incremented by 1 after the last address is sent out. This new address then becomes the effective address. If a JMS (Jump to Subroutine) instruction is received by the CPU, the program control is transferred to the address called out in JMS instruction. This address is stored in the register just above the old program counter which now saves the address of the next instruction to be executed following the last JMS. (3) This return address becomes the effective address following the BBL(Branch back and load) instruction at the end of the subroutine.

<sup>(1)</sup> In this case the instruction is executed on the 4-bit content addressed by RRRR.

<sup>(2)</sup> In this case the instruction is executed on the 8-bit content addressed by RRRX, where X is specified for each instruction.

<sup>(3)</sup> Since the JMS instruction is a 2-word instruction the old effective address is incremented by 2 to correctly give the address of the next instruction to be executed after the return from JMS.

Table IV - Operation of the Address Register on a Jump to Subroutine Instruction

In summary, then, a JMS instruction pushes the program counter up one level and a BBL instruction pushes the program counter down one level. Since there are 3 registers in the push down stack, 3 return addresses may be saved. If a fourth JMS occurs, the deepest return address (the first one stored) is lost.

Table IV shows the operation of the address stack.

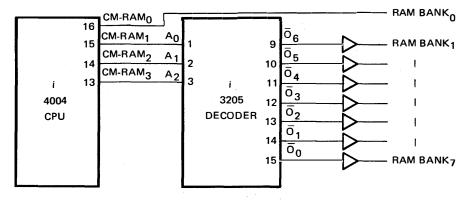

#### 4. Operation of The Command Lines and the SRC Command

The CPU command lines (CM-ROM, CM-RAM $_{\rm i}$ ) are used to control the ROM's and RAM's by indicating to them how to interpret the data bus content at any given time.

The command lines allow the implementation of RAM bank, chip, register and character addressing, ROM chip addressing, as well as activating the instruction control in each ROM and RAM chip at the time the CPU receives an I/O and RAM group instruction.

In a typical system configuration the CM-ROM line can control up to sixteen 4001's and each CM-RAM $_{1}$  line can control up to four 4002's.

Each CM-RAM<sub>i</sub> line can be selected by the execution of the DCL (Designate Command Line) instruction. The CM-ROM line, however, is always enabled. (1)

<sup>(1)</sup> If the number of ROM's in the system needs to be more than 16, external circuitry can be used to route CM-ROM to two ROM banks. The same comment applies to the CM-RAM; lines if more than 16 RAM's need to be used.

For the execution of an I/O and RAM group instruction the following steps are necessary:

- (1) The appropriate command line must be selected (by DCL)

- (2) The ROM chip and RAM chip, register and character must be selected using the SRC (Send Register Control) instruction.

- (3) An I/O and RAM instruction must be fetched (WRM, RDM, WRR, . . . .)

Figure 4. Operation of the Command Control Lines

Following is a detailed explanation of each step.

- (1) Prior to execution of the DCL instruction the desired  ${\rm CM-RAM}_{\dot{1}}$  code must be stored in the accumulator (for example through an LDM instruction).

- (2) During DCL the CM-RAM<sub>i</sub> code is transferred from the accumulator to the command control register in the CPU. One CM-RAM<sub>i</sub> line is then activated (selecting one RAM bank) during the next instruction which would be an SRC.

The CM-RAM<sub>i</sub> code remains in the command control register until a new DCL instruction is received. Each time a new SRC instruction is executed it will operate on the same RAM bank. This allows all RAM and I/O instructions to be executed within the same RAM bank without the necessity of executing another DCL instruction each time. DCL does not affect CM-ROM. Only the RAM on the designated command line will latch the SRC.

If up to 4 RAM chips are used in a system, it is convenient to arrange them in a bank controlled by  $CM-RAM_O$ . This is because  $CM-RAM_O$  is automatically selected after the application of at least one RESET (usually at start-up time.) In this case DCL is unnecessary and Step 1 & 2 are omitted).

The SRC instruction specified an index register pair in the CPU, whose content is an 8-bit address (this 8-bit address has previously been stored in the register pair) used to select a RAM chip, register and character and a ROM chip. This address is sent to the data bus during X2 and X3 time of the SRC instruction cycle. At X2 time the CM-ROM line and the selected CM-RAM; line are in a logic true state to indicate which bank of RAMs and ROMs are to respond to the 8-bit address that is now on the data bus. The 8-bit address is interpreted in the following way:

by the ROM's and Ine first 4-bits (X2 time) select one chip out of 16; a flip-flop is set in the selected chip.

b) The second 4-bits (X3 time) are ignored.

a) The first four bits sent out at X2 time select one out of four chips and one out of four registers. The two higher order bits (D3, D2) select the chip and the two lower order bits (D1, D0) select the register.

by the RAM's

b) The second 4-bits (X3 time) select one 4-bit character out of 16; The address is stored in the address register of

the selected chip.

(See Section V for a detailed description of the RAM chip)

(4) At this time one ROM chip and one RAM chip, register and character, have been selected. If the CPU fetches an I/O and RAM instruction, it will cause the CM-ROM and the selected CM-RAM; line to be logical true at M2 time. This allows the previously selected ROM's and RAM's to receive the modifier of the instruction. The selected ROM and RAM will decode the instruction (as well as the CPU) and appropriately execute it during the execution time of the same instruction cycle.

It should be added that the CM-ROM and the selected CM-RAM $_{

m i}$ lines are always in a logical true state at A3 time of any instruction cycle.

CM-ROM equals "1" at A3 time indicates to ROM's that the code at A3 time is the chip number of a ROM within their bank. This feature allows the user to expand the system to more than 16 ROM chips.

${

m CM-RAM_{\mbox{\scriptsize i}}}$  equals "1" at A3 time has no meaning for the RAM chips, however, it could be meaningful if ROM's and RAM's were controlled by a CM-RAMi line.

Figure 4 summarizes the operation of the command lines in the various instruction cycles.

#### C. Basic Instruction Set

Table V shows the basic instruction set of the 4004 (CPU). Section VII will describe each instruction in detail.

[Those instructions preceded by an asterisk (\*) are 2 word instructions that occupy 2 successive locations in ROM]

MACHINE INSTRUCTIONS (Logic 1 = Low Voltage = Negative Voltage; Logic 0 = High Voltage = Ground)

| MNEMONIC | OPR<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>     | OPA<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                                                         | DESCRIPTION OF OPERATION                                                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP      | 0000                                                                   | 0 0 0 0                                                                                                                    | No operation.                                                                                                                                                                                                                             |

| *JCN     | 0 0 0 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> C <sub>4</sub><br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> | Jump to ROM address $A_2$ $A_2$ $A_2$ $A_2$ $A_1$ $A_1$ $A_1$ $A_1$ (within the same ROM that contains this JCN instruction) if condition $C_1$ $C_2$ $C_3$ $C_4$ $C_4$ is true, otherwise skip (go to the next instruction in sequence). |

| *FIM     | 0 0 1 0<br>D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> | R R R 0<br>D <sub>1</sub> D <sub>1</sub> D <sub>1</sub> D <sub>1</sub>                                                     | Fetch immediate (direct) from ROM Data D <sub>2</sub> , D <sub>1</sub> to index register pair location RRR. (2)                                                                                                                           |

| SRC      | 0 0 1 0                                                                | RRR1                                                                                                                       | Send register control. Send the address (contents of index register pair RRR) to ROM and RAM at X <sub>2</sub> and X <sub>3</sub> time in the Instruction Cycle.                                                                          |

| FIN      | 0 0 1 1                                                                | RRR0                                                                                                                       | Fetch indirect from ROM. Send contents of index register pair location 0 out as an address. Data fetched is placed into register pair location RRR.                                                                                       |

| JIN      | 0 0 1 1 -                                                              | RRR1                                                                                                                       | Jump indirect. Send contents of register pair RRR out as an address at $A_1$ and $A_2$ time in the Instruction Cycle.                                                                                                                     |

| *JUN     | 0 1 0 0<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | A <sub>3</sub> A <sub>3</sub> A <sub>3</sub> A <sub>3</sub><br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> | Jump unconditional to ROM address A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> .                                                                                                                                                      |

| *JMS     | 0 1 0 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | A <sub>3</sub> A <sub>3</sub> A <sub>3</sub> A <sub>3</sub><br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> | Jump to subroutine ROM address A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> , save old address. (Up 1 level in stack.)                                                                                                                |

| INC      | 0 1 1 0                                                                | RRRR                                                                                                                       | Increment contents of register RRRR. (3)                                                                                                                                                                                                  |

| *ISZ     | 0 1 1 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | R R R R<br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub>                                                     | Increment contents of register RRRR. Go to ROM address A <sub>2</sub> , A <sub>1</sub> (within the same ROM that contains this ISZ instruction) if result ≠0, otherwise skip (go to the next instruction in sequence).                    |

| ADD      | 1 0 0 0                                                                | RRRR                                                                                                                       | Add contents of register RRRR to accumulator with carry.                                                                                                                                                                                  |

| SUB      | 1 0 0 1                                                                | RRRR                                                                                                                       | Subtract contents of register RRRR to accumulator with borrow.                                                                                                                                                                            |

| LD       | 1 0 1 0                                                                | RRRR                                                                                                                       | Load contents of register RRRR to accumulator.                                                                                                                                                                                            |

| хсн      | 1 0 1 1                                                                | RRRR                                                                                                                       | Exchange contents of index register RRRR and accumulator.                                                                                                                                                                                 |

| BBL      | 1 1 0 0                                                                | DDDD                                                                                                                       | Branch back (down 1 level in stack) and load data DDDD to accumulator.                                                                                                                                                                    |

| LDM      | 1 1 0 1                                                                | DDDD                                                                                                                       | Load data DDDD to accumulator,                                                                                                                                                                                                            |

Table V - Basic CPU Instruction Set

#### INPUT/OUTPUT AND RAM INSTRUCTIONS

(The RAM's and ROM's operated on in the I/O and RAM instructions have been previously selected by the last SRC instruction executed.)

| MNEMONIC           | OPR<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | OPA<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | DESCRIPTION OF OPERATION                                                                                                                |

|--------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| WRM                | 1 1 1 0                                                            | 0 0 0 0                                                            | Write the contents of the accumulator into the previously selected RAM main memory character.                                           |

| WMP                | 1 1 1 0                                                            | 0 0 0 1                                                            | Write the contents of the accumulator into the previously selected RAM output port, (Output Lines)                                      |

| WRR                | 1 1 1 0                                                            | 0 0 1 0                                                            | Write the contents of the accumulator into the previously selected ROM output port. (I/O Lines)                                         |

| WPM                | 1 1 1 0                                                            | 0 0 1 1                                                            | Write the contents of the accumulator into the previously selected half byte of read/write program memory (for use with 4008/4009 only) |

| WRφ <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 0 0                                                            | Write the contents of the accumulator into the previously selected RAM status character 0.                                              |

| WR1 <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 0 1                                                            | Write the contents of the accumulator into the previously selected RAM status character 1.                                              |

| WR2 <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 1 0                                                            | Write the contents of the accumulator into the previously selected RAM status character 2.                                              |

| WR3 <sup>(4)</sup> | 1 1 1 0                                                            | 0 1 1 1                                                            | Write the contents of the accumulator into the previously selected RAM status character 3.                                              |

| SBM                | 1 1 1 0                                                            | 1 0 0 0                                                            | Subtract the previously selected RAM main memory character from accumulator with borrow.                                                |

| RDM                | 1 1 1 0                                                            | 1 0 0 1                                                            | Read the previously selected RAM main memory character into the accumulator.                                                            |

| RDR                | 1 1 1 0                                                            | 1 0 1 0                                                            | Read the contents of the previously selected ROM input port into the accumulator. (I/O Lines)                                           |

| ADM                | 1 1 1 0                                                            | 1 0 1 1                                                            | Add the previously selected RAM main memory character to accumulator with carry.                                                        |

| RDφ <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 0 0                                                            | Read the previously selected RAM status character 0 into accumulator.                                                                   |

| RD1 <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 0 1                                                            | Read the previously selected RAM status character 1 into accumulator.                                                                   |

| RD2 <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 1 0                                                            | Read the previously selected RAM status character 2 into accumulator.                                                                   |

| RD3 <sup>(4)</sup> | 1 1 1 0                                                            | 1 1 1 1                                                            | Read the previously selected RAM status character 3 into accumulator.                                                                   |

#### **ACCUMULATOR GROUP INSTRUCTIONS**

| CLB | 1 1 1 1  | 0 0 0 0 | Clear both. (Accumulator and carry)                                                                      |

|-----|----------|---------|----------------------------------------------------------------------------------------------------------|

| CLC | 1 1 1 1  | 0 0 0 1 | Clear carry.                                                                                             |

| IAC | 1 1 1 1  | 0 0 1 0 | Increment accumulator.                                                                                   |

| СМС | 1 1 1 1  | 0 0 1 1 | Complement carry.                                                                                        |

| CMA | 1 1 1 1  | 0 1 0 0 | Complement accumulator.                                                                                  |

| RAL | 1 1 1 1  | 0 1 0 1 | Rotate left. (Accumulator and carry)                                                                     |

| RAR | 1 1 1 1  | 0 1 1 0 | Rotate right. (Accumulator and carry)                                                                    |

| TCC | 1 1 1 1  | 0 1 1 1 | Transmit carry to accumulator and clear carry.                                                           |

| DAC | 1 1 1 1  | 1 0 0 0 | Decrement accumulator.                                                                                   |

| TCS | 1 1 1 1  | 1 0 0 1 | Transfer carry subtract and clear carry.                                                                 |

| STC | 1 1 1 1  | 1 0 1 0 | Set carry.                                                                                               |

| DAA | 1 1 1 1  | 1 0 1 1 | Decimal adjust accumulator.                                                                              |

| КВР | 1 1 1 1  | 1 1 0 0 | Keyboard process. Converts the contents of the accumulator from a one out of four code to a binary code. |

| DCL | 1 1 1 1  | 1 1 0 1 | Designate command line.                                                                                  |

| L   | <u> </u> | L       |                                                                                                          |

NOTES: (1)The condition code is assigned as follows:

$C_1 = 1$  Invert jump condition  $C_2 = 1$  Jump if accumulator is zero  $C_4 = 1$  Jump if test signal is a 0  $C_1 = 0$  Not invert jump condition  $C_3 = 1$  Jump if carry/link is a 1

$<sup>^{(2)}</sup>$ RRR is the address of 1 of 8 index register pairs in the CPU.

$<sup>^{(3)}</sup>$ RRRR is the address of 1 of 16 index registers in the CPU.

<sup>(4)</sup> Each RAM chip has 4 registers, each with twenty 4-bit characters subdivided into 16 main memory characters and 4 status characters. Chip number, RAM register and main memory character are addressed by an SRC instruction. For the selected chip and register, however, status character locations are selected by the instruction code (OPA).

#### IV. 4001 - 256 x 8 MASK PROGRAMMABLE ROM AND 4 BIT I/O PORT

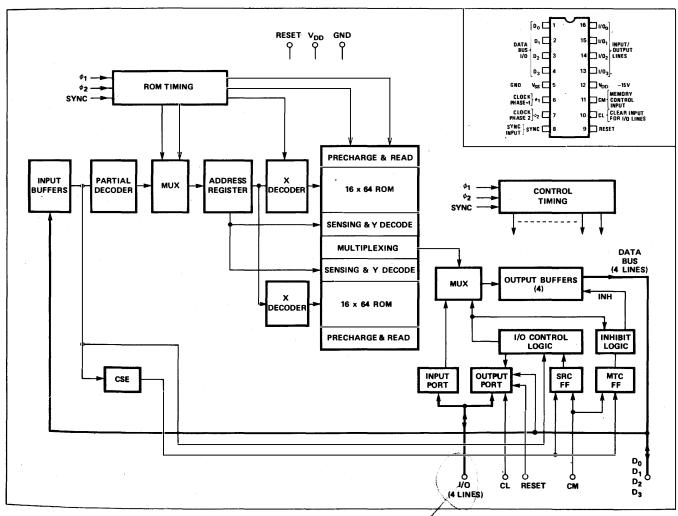

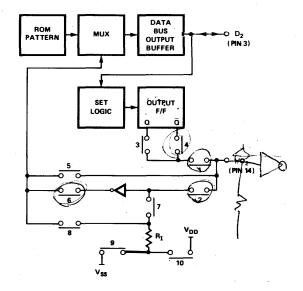

The 4001 performs two basic and distinct functions: As a ROM it stores  $256 \times 8$  words of program or data tables; as a vehicle of communication with peripheral devices it is provided with 4 I/O pins and associated control logic to perform input and output operations. (The block diagram is shown in Figure 5.)

In the ROM mode of operation the 4001 will receive an 8-bit address during A1 and A2 time (see Figure 2) and a chip number, together with CM-ROM during A3 time. When CM-ROM is present, only the chip whose metal option code matches the chip number code sent during A3 (CSE = "1") is allowed to send data out during the following two cycles:  $M_1$  and  $M_2$ . The activity of the 4001 in the ROM mode ends at  $M_2$ . Before going into the I/O mode of operation we must first review two basic instructions used in conjunction with it.

#### 1. SRC Instruction (Send address to ROM and RAM)

When the CPU executes an SRC instruction it will send out 8 bits of data during  $X_2$  and  $X_3$  and will activate the CM-ROM and one CM-RAM<sup>(1)</sup> line at  $X_2$ . Data at  $X_2$ , with simultaneous presence of CM-ROM, is interpreted by the 4001 as the chip number of the unit that should later perform an I/O operation. Data at  $X_3$  is ignored. In the case of the 4002, data at  $X_2$  will designate the chip number (one out of 4 chips) and the register number (one out of 4 registers); data at  $X_3$  will designate the 4-bit character (one out of 16) to be operated upon. After SRC only one 4001 and one 4002 will be ready to execute a following I/O instruction.

#### 2. I/O and RAM Instructions

I/O and RAM instructions allow the CPU to communicate with the I/O ports of the 4001's and 4002's. When the CPU receives an I/O instruction it will activate the CM-ROM and one CM-RAM line during M2, in time for 4001's and 4002's to receive the second part (OPA) of the I/O instruction. The OPA portion of the I/O instruction is a code specifying which I/O operation should be performed. There are 15 different operations possible. The only ones affecting the 4001 operation are RDR - read ROM port, and WRR - write ROM port.

In the I/O mode of operation, the selected 4001 (by SRC) after receiving RDR will transfer the information present at its I/O pins to the data bus at X2. If the instruction received was WRR, the data present on the data bus at  $X_2.\emptyset_2$  will be latched on the output flip-flops associated with the I/O lines.

<sup>(1)</sup> Only one out of four CM-RAM lines is allowed to be activated at any given time. CM-RAM line selection (RAM bank switching) is accomplished by the CPU when a "designate command line" (DCL) instruction is executed. If no DCL is executed prior to SRC, the CM-RAM<sub>O</sub> will automatically be activated at X<sub>2</sub> provided that RESET was applied at least once to the System (most likely at the start-up time). See detailed definition of system instruction in Section VII.

Figure 5 shows the block organization of the 4001. The ROM array has a dynamic mode of operation and is divided into two blocks of  $16 \times 64$  cells each. Multiplexing is needed for both address to address register and data to data bus output buffer operations.

The MTC flip-flop controls the outputting of data. It is set at  $A_3$ , (see Figure 2), if CM-ROM and CSE (chip select) are "1". CSE is a single 4-input AND gate of the 4 data bus lines, using Di or Di according to the chip number that the user wants to assign to the chip. This is accomplished by metal mask option.

The SRC flip-flop is set by CM-ROM and CSE at  $X_2$ , (see Figure 2), and presets the I/O logic for a following input or output operation.

<u>TIMING</u> generates all internal timing signals for the ROM and I/O control using SYNC,  $\emptyset_1$  and  $\emptyset_2$ . A RESET(1) signal will clear all static flip-flops and will inhibit data out.

The output flip-flops associated with I/O pins can also be cleared using an external CL pin.

(1) RESET is used for the start-up of the system.

Figure 5. 4001 ROM Block Diagram

#### ROM Options and Ordering the ROM

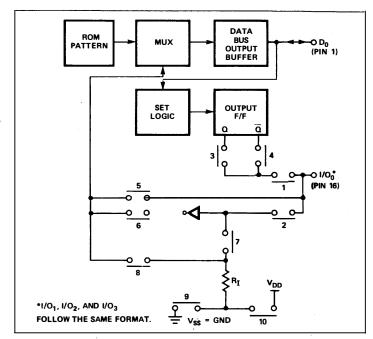

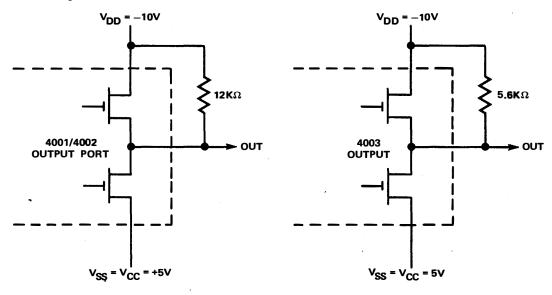

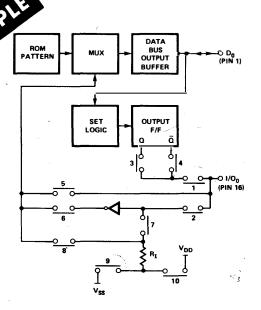

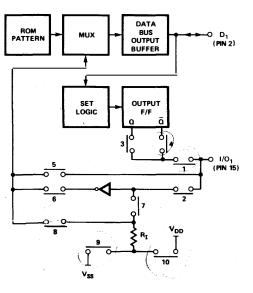

Each I/O pin on each ROM can be uniquely chosen to be either an input or output line by metal option. Also each input or output can either be inverted or direct. When the pin is chosen as an input it may have an onchip resistor connected to either VDD or VSS. Figure 6 shows the available options for each I/O pin.

When ordering a 4001 the following information must be specified:

- 1. Chip number

- 2. All the metal options for each I/O pin

- 3. ROM pattern to be stored in each of the 256 locations.

A blank customer truth table is available upon request from Intel. A copy of this table is shown in the appendix.

Figure 6. 4001 Available Metal Options for Each I/O Pin

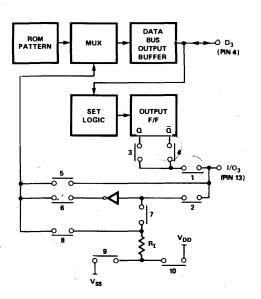

#### V. 4002 - 320 BIT RAM AND 4 BIT OUTPUT PORT

The 4002 performs two distinct functions. As a RAM it stores 320 bits arranged in 4 registers of twenty 4-bit characters each (16 main memory characters and 4 status characters). As a vehicle of communication with peripheral devices, it is provided with 4 output lines and associated control logic to perform output operations. (The block diagram is shown in Figure 7).

In the RAM mode, the operation is as follows: When the CPU receives an SRC instruction it will send out the content of the designated index register pair during  $X_2$  and  $X_3$  and will activate one CM-RAM line at  $X_2$  for the previously (1) selected RAM bank.

The data at  $X_2$  and  $X_3$  is interpreted as shown below:

|                                           | X <sub>2</sub>                                | X <sub>3</sub>                                                                        |  |  |  |

|-------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| D <sub>3</sub> D <sub>2</sub><br>Chip No. | D <sub>1</sub> D <sub>0</sub><br>Register No. | D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> Main Memory Character No. |  |  |  |

| (0 through 3)                             | (0 through 3)                                 | (0 through 15)                                                                        |  |  |  |

The status character location (0 through 3) as well as the operation to be performed on it are selected by the OPA portion of the I/O and RAM instructions.

<sup>(1)</sup> Bank switching is accomplished by the CPU after receiving a "DCL" (designate command line) instruction. Prior to execution of the DCL instruction the desired CM-RAM code has been stored in the accumulator (for example through an LDM instruction.) During DCL the CM-RAM code is transferred from the accumulator to the CM-RAM register. The RAM bank is then selected starting with the next instruction.

For chip selection, the 4002 is available in two metal options, 4002-1 and 4002-2. An external pin,  $P_0$ , is also available for chip selection. The chip number is assigned as follows:

| Chip No. | 4002 Option | P <sub>0</sub> | D <sub>3</sub> D <sub>2</sub> @ X <sub>2</sub> |  |  |

|----------|-------------|----------------|------------------------------------------------|--|--|

| 0        | 4002-1      | GND            | 0 0                                            |  |  |

| 1        | 4002-1      | $v_{DD}$       | 0 1                                            |  |  |

| 2        | 4002-2      | GND            | 1 0                                            |  |  |

| 3        | 4002-2      | $V_{DD}$       | 1 1                                            |  |  |

Figure 7. 4002 RAM Block Diagram

Presence of CM-RAM during  $X_2$  tells 4002 s that an SRC instruction was received. For a given combination of data at  $X_2$  on  $D_2$ ,  $D_3$ , only the chip with the proper metal option and  $P_0$  state will be ready for the I/O or RAM operation that follows.

The twenty 4-bit characters for each 4002 register are arranged as follows:

- 1. 16 characters addressable by an SRC instruction: Four 16-character registers constitute the "main" memory.

- 4 characters addressable by the OPA of an I/O instruction: Four 4-character registers constitute the "status character" memory.

Two separate X decoders switch between main and status character memories.

When an I/O or RAM instruction is received by the CPU, the CPU will activate one CM-RAM line during  $\rm M_2$ , in time for the 4002's to receive the OPA (2nd part of the instruction), which will specify the I/O or RAM operation to be performed. Shown below is a list of the 15 possible I/O and RAM operations.

The I/O and RAM operations are divided into Read operations (IOR) and Write operations (IOW). The state of  $D_3$  will determine if the operation is a read or a write.  $D_3 = 1$  for IOR,  $D_3 = 0$  for IOW (see Basic Instruction Set, shown in Section IIIc).

For each I/O instruction the action is as shown in the following table:

| Instr.<br>Mnem, | 4001<br>I/O Oper. | 4002<br>I/O Oper. | 4002<br>RAM Op. | 4001 Data Bus Output<br>Buffer Enabled | 4002 Data Bus Output<br>Buffer Enabled | 4004 Data Bus Output<br>Buffer Enabled |

|-----------------|-------------------|-------------------|-----------------|----------------------------------------|----------------------------------------|----------------------------------------|

| WRM             |                   |                   | х               |                                        |                                        | ×                                      |

| WMP             |                   | x                 |                 |                                        |                                        | x                                      |

| WRR             | х                 |                   |                 |                                        |                                        | х ,                                    |

| WRØ             | 4                 |                   | х               |                                        |                                        | ×                                      |

| WR1             |                   |                   | x               |                                        |                                        | x                                      |

| WR2             |                   |                   | x               |                                        |                                        | ×                                      |

| WR3             |                   |                   | х               |                                        |                                        | x                                      |

| SBM             |                   |                   | х               |                                        | x                                      |                                        |

| RDM             |                   |                   | х               |                                        | x                                      |                                        |

| RDR             | x                 | _                 |                 | х                                      |                                        |                                        |

| ADM             |                   |                   | х               |                                        | x                                      |                                        |

| RDØ             |                   |                   | х               |                                        | x                                      |                                        |

| RD1             |                   |                   | x               |                                        | x                                      |                                        |

| RD2             |                   |                   | х               |                                        | x                                      |                                        |

| RD3             |                   |                   | х               |                                        | x                                      |                                        |

In the I/O mode of operation, the selected 4002 chip (by SRC), after receiving the OPA of an I/O instruction (CM-RAM activated at  $M_2$ ), will decode the instruction.

If the instruction is WMP, the data present on the data bus during  $X2.\emptyset2$  will set the output flip-flops associated with the I/O pins. That information will be available until next WMP for peripheral devices control.

An external signal - RESET - when applied to the chip, will cause a clear of all output and control static flip-flops and will clear the RAM array. To completely clear the memory, RESET must be applied for at least 32 instruction cycles (256 clock periods) to allow the internal refresh counter to scan the memory. During RESET the data bus output buffers are inhibited (floating condition).

Figure 7 shows the block organization of the 4002. The RAM array uses a dynamic cell, therefore it must be periodically refreshed. A refresh counter scans the memory array and the memory content is refreshed during an idle portion of the system cycle ( $M_1$  and  $M_2$ ). An address multiplexer allows loading the content of either the refresh counter or the address register into the decoder.

The RAM control is composed of an SRC flip-flop, chip selection logic, an instruction register, instruction decoder and I/O control logic. This block controls the loading of the address register, the status and main memory decoder switching, the generation of memory timing, the enable of the data bus input-output buffers, the RAM read/write operations, and the loading of the output flip-flops.

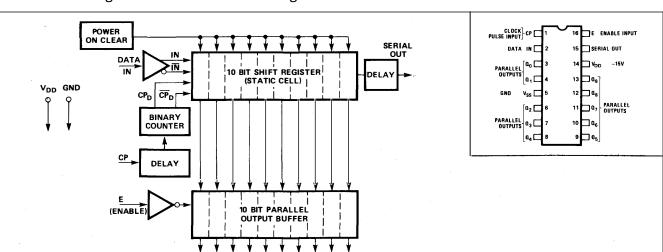

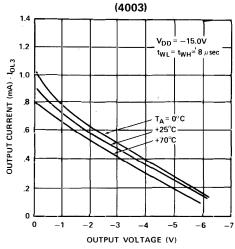

#### VI. 4003 10-BIT SERIAL-IN/PARALLEL-OUT, SERIAL-OUT SHIFT REGISTER

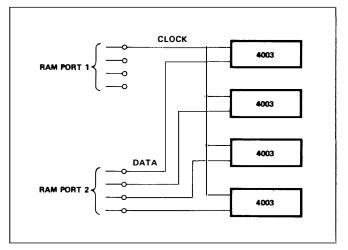

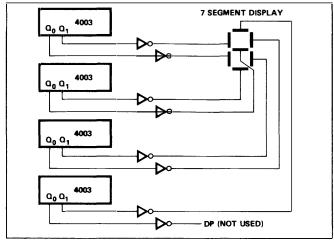

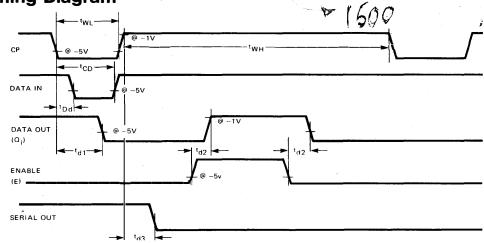

The 4003 is a 10-bit serial-in, parallel-out, serial-out shift register with enable logic. The 4003 is used to expand the number of ROM and RAM I/O ports to communicate with peripheral devices such as keyboards, printers, displays, readers, teletypewriters, etc.

Data is loaded serially and is available in parallel on 10 output lines which are accessed through enable logic. When enabled (E = low), the shift register contents is read out; when not enabled (E = high), the parallel-out lines are at  $V_{\rm SS}$ . The serial-out line is not affected by the enable logic.

Data is also available serially permitting an indefinite number of similar devices to be cascaded together to provide shift register length multiples of 10.

The data shifting is controlled by the CP signal. An internal power-on-clear circuit will clear the shift register ( $Q_i = V_{SS}$ ) between the application of the supply voltage and the first CP signal.

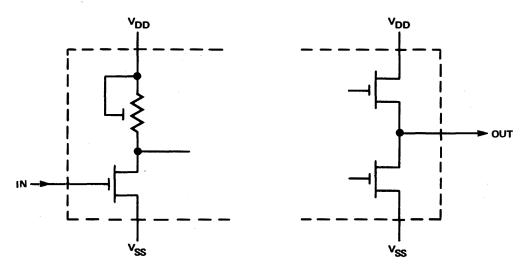

The 4003 output buffers are push-pull ratio type, useful for multiple key depression rejection when a 4003 is used in conjunction with a keyboard. In this mode if up to three output lines are connected together, the state of the output is high (Logic "0") if at least one line is high.

The 4003 is a single phase static shift register; however, the clock pulse (CP) maximum width is limited to 10 msec. Data-in and CP can be simultaneous. To avoid race conditions, CP is internally delayed.

Fig. 8 shows the block organization of the 4003.

$\mathbf{Q_0} \ \mathbf{Q_1} \ \mathbf{Q_2} \ \mathbf{Q_3} \ \mathbf{Q_4} \ \mathbf{Q_5} \ \mathbf{Q_6} \ \mathbf{Q_7} \ \mathbf{Q_8} \ \mathbf{Q_9}$

Figure 8. 4003 Shift Register Block Diagram

#### VII. DETAILED INSTRUCTION REPERTOIRE OF THE MCS-4

#### A. Instruction Format

As previously discussed, the MCS-4 micro computer set has two types of instruction.

- a) 1 word instruction with an 8-bit code and an execution time of 10.8 usec.

- b) 2 word instruction with a 16-bit code and an execution time of 21.6 µsec.

Due to the time multiplexed operation of the system, the 8-bit instruction is fetched 4-bits at a time on two successive clock periods. The first 4-bit code is called OPR, the second 4-bit code is called OPA.

The instruction formats were illustrated in Tables I and II

#### B. Symbols and Abbreviations

The following Symbols and abbreviations will be used thorughout the next few sections:

| the content of                                                          |

|-------------------------------------------------------------------------|

| is transferred to                                                       |

| Accumulator (4-bit)                                                     |

| Carry/link Flip-Flop                                                    |

| Accumulator Buffer Register (4-bit)                                     |

| Index register address                                                  |

| Index register pair address                                             |

| Low order program counter Field (4-bit)                                 |

| Middle order program counter Field (4-bit)                              |

| High order program counter Field (4-bit)                                |

| Order i content of the accumulator                                      |

| Order i content of the command register                                 |

| RAM main character location                                             |

| RAM status character i                                                  |

| Data bus content at time T                                              |

| The 3 registers in the address register other than the program counter. |

|                                                                         |

Throughout the text "page" means a block of 256 instructions whose address differs only on the most significant 4 bits (all of the instructions on one page are all stored in one ROM).

Example: page 7 means all locations having addresses between 0111 0000 0000 and 0111 1111 1111

#### C. Format for Describing Each Instruction

Each instruction will be described as follows:

- (1) Mnemonic symbol and meaning

- (2) OPR and OPA code

- (3) Symbolic representation of the instruction

- (4) Description of the instruction (if necessary)

- (5) Example and/or exceptions (if necessary)

#### D. One Word Machine Instructions

Mnemonic: NOP (No Operation)

OPR OPA: 0000 0000 Symbolic: Not applicable

Description: No operation performed

Mnemonic: LDM (Load Data to Accumlator)

OPR OPA: 1101 DDDD

Symbolic: DDDD. → ACC

Description: The 4 bits of data, DDDD stored in the OPA field of

instruction word are loaded into the accumulator. The previous contents of the accumlator are lost. The

carry/link bit is unaffected.

Mnemonic: LD (Load index register to Accumulator)

OPR OPA: 1010 RRRR

Symbolic: (RRRR)—➤ACC

Description: The 4 bit content of the designated index register (RRRR)

is loaded into the accumulator. The previous contents of the accumulator are lost. The 4 bit content of the index register and the carry/link bit are unaffected.

Mnemonic: XCH (Exchange index register and accumlator)

OPR OPA: 1011 RRRR

Symbolic: (ACC)→ ACBR, (RRRR)→ ACC, (ACBR)→ RRRR

Description: The 4 bit content of the designated index register is

loaded into the accumulator. The prior content of the accumulator is loaded into the designated register. The

carry/link bit is unaffected.

Mnemonic: ADD (Add index register to accumulator with carry)

OPR OPA: 1000 RRRR

Symbolic:  $(RRRR) + (ACC) + (CY) \rightarrow ACC, CY$

Description: The 4 bit content of the designated index register is added to the content of the accumulator with carry.

added to the content of the accumulator with carry. The result is stored in the accumulator. The carry/link is set to 1 if a sum greater than  $15_{10}$  was generated to indicate a carry out; otherwise, the carry/link is set to 0. The 4 bit content of the index register is un-

affected.

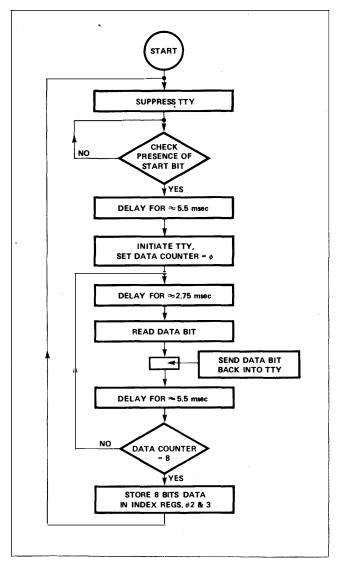

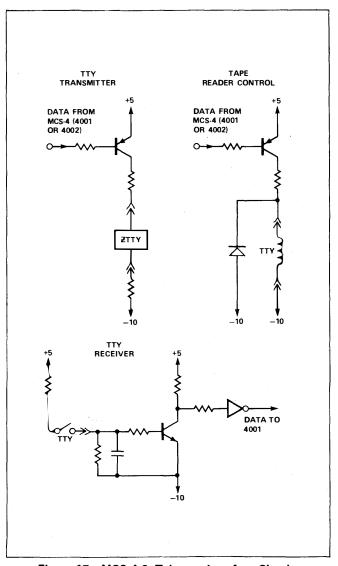

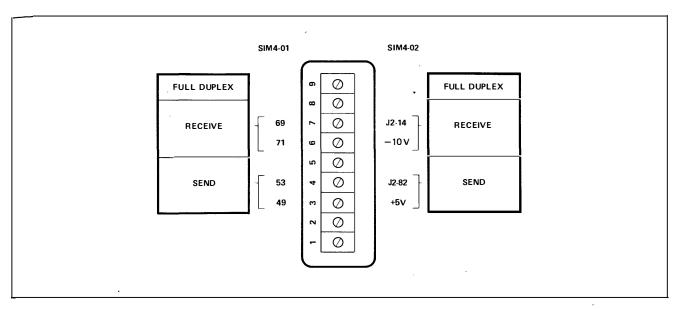

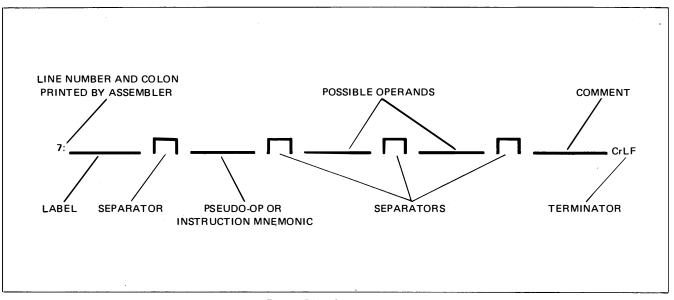

CARRY —→ c4 s<sub>3</sub> s2 s<sub>1</sub> s<sub>0</sub> ← SUM (CY) (ACC)