## Fault Tolerance using Stable Memory

Edited by

Brian Coghlan Trinity College Dublin

> Germán Fabregat LISITT

## **Authors**

Michel Banâtre IRISA/INRIA Campus universitaire de Beaulieu F-35042 Rennes cedex France michel.banatre@irisa.fr

David Boyce ex Bull U.K. Cherry Tree Lane Hemel Hempstead U.K.

Brian Coghlan

Department of Computer Science

Trinity College Dublin

Ireland

brian.coghlan@cs.tcd.ie

Mark Cotton ex Bull U.K. Cherry Tree Lane Hemel Hempstead U.K. mcotton@sco.com

Germán Fabregat Departamento de Informática Universidad Jaume I, Campus del Penyeta Roja sn 12071 Castellón España fabregat@vents.uji.es

Alain Gefflaut

IRISA/INRIA

Campus universitaire de Beaulieu

F-35042 Rennes cedex

France

alain.gefflaut@irisa.fr

Jeremy Jones Department of Computer Science Trinity College Dublin Ireland jeremy.jones@cs.tcd.ie Philippe Joubert ex IRISA/INRIA Campus universitaire de Beaulieu F-35042 Rennes cedex France philippe.joubert@bull.net

Pete Lee

Department of Computing Science

University of Newcastle

Newcastle upon Tyne, NE1 7RU

U.K.

p.a.lee@newcastle.ac.uk

Antonio Marquez ETRA Valencia España antonio.marques@dg3.cec.be

Rafael Martínez Instituto de Robótica Universitat de València Hugo de Moncado, 4 Entlo., 46010 Valencia España rafael.martinez@uv.es

Isi Mitrani

Department of Computing Science

University of Newcastle

Newcastle upon Tyne, NE1 7RU

U.K.

isi.mitrani@newcastle.ac.uk

Christine Morin

IRISA/INRIA

Campus universitaire de Beaulieu

F-35042 Rennes cedex

France

christine.morin@irisa.fr

christine.morin@ir Antonio Pérez

Departamento de Arquitectura y Tecnología de Sistemas Informáticos Facultad de Informática

Universidad Politécnica de Madrid

España

aperez@fi.upm.es

Juan José Serrano

Departamento de Ingeniería de Sistemas

Computación y Automática

Universidad Politécnica de Valencia

España

juanjo@aii.upv.es

Axel Wegner ARTTIC Hamburg GmbH Katharinenstr. 11,3. Stock D-20457 Hamburg Germany aw@arttic.com

## **Contributors**

Ekaterina Ametistova ex Department of Computing Science University of Newcastle Newcastle upon Tyne, NE1 7RU U.K.

Vicente Cerverón

Dpto. de Informática y Electrónica

Universitat de València

Doctor Moliner, 50, 46100 Burjassot Valencia

España

vicente.cerveron@uv.es

Henry Vui Chung ex Department of Computer Science Trinity College Dublin Ireland

Marylène Clatin IRISA/INRIA Campus universitaire de Beaulieu F-35042 Rennes cedex France

Andrew Cockburn ex Bull U.K. Cherry Tree Lane Hemel Hempstead U.K.

Cornelius Frankenfeld ex Stollmann GmbH Hamburg Germany A. García Departamento de Arquitectura y Tecnología de Sistemas Informáticos

Facultad de Informática

Universidad Politécnica de Madrid

España

Pedro Gil

Departamento de Ingeniería de Sistemas Computación y Automática Universidad Politécnica de Valencia

España

Brian Hennessy ex Department of Computer Science

Trinity College Dublin

Ireland

Dominic Herity

ex Department of Computer Science

Trinity College Dublin

Ireland

Keith Heron

Department of Computing Science

University of Newcastle

Newcastle upon Tyne, NE1 7RU

U.K.

Madhu Kashup

Bull U.K.

Cherry Tree Lane

Hemel Hempstead

U.K.

Danny Keogan

ex Department of Computer Science

Trinity College Dublin

Ireland

M. A. Liébana

Departamento de Arquitectura y Tecnología de Sistemas Informáticos

Facultad de Informática

Universidad Politécnica de Madrid

España

Gregorio Martín Instituto de Robótica Universitat de València Hugo de Moncado, 4 Entlo., 46010 Valencia España gregorio@glup.irobot.uv.es

Paula McGrath ex Department of Computer Science Trinity College Dublin Ireland

#### L. M. Muñoz

Departamento de Arquitectura y Tecnología de Sistemas Informáticos Facultad de Informática Universidad Politécnica de Madrid España

Philip O'Carroll ex Department of Computer Science Trinity College Dublin Ireland

Rafael Ors Departamento de Ingeniería de Sistemas Computación y Automática Universidad Politécnica de Valencia España

Carlos Pérez

Dpto. de Informática y Electrónica

Universitat de València

Doctor Moliner, 50, 46100 Burjassot Valencia

España

carlos.perez@uv.es

#### L. Prieto

Departamento de Arquitectura y Tecnología de Sistemas Informáticos Facultad de Informática Universidad Politécnica de Madrid España

Santiago Rodríguez Departamento de Arquitectura y Tecnología de Sistemas Informáticos Facultad de Informática Universidad Politécnica de Madrid España Vicente Santonja Departamento de Ingeniería de Sistemas Computación y Automática Universidad Politécnica de Valencia España

Andrew Thomas ex Department of Computing Science University of Newcastle Newcastle upon Tyne, NE1 7RU U.K.

### **Preface**

**Stable** 1. Firmly established; not to be easily moved, shaken or overthrown; firmly fixed or settled; as, a *stable* government; a *stable* structure. 2. In *physics*, a term applied to that condition of a body in which, if its equilibrium be disturbed, it is immediately restored, as in the case when the centre of gravity is below the point of support. 3. Steady in purpose; constant; firm in resolution; not easily diverted from a purpose; not fickle or wavering; as, a *stable* man; a *stable* character. 4. Abiding; durable; not subject to be overthrown or changed; as, this life is not *stable*. SYN. Fixed, established, immovable, steady, constant, abiding, strong.

**Storage** 1. The act of storing; the act of depositing in a store or warehouse for safe-keeping; the safe-keeping of goods in a warehouse. 2. The price charged or paid for keeping goods in a store.

Ogilvie's Imperial Dictionary of the English Language, edited by Charles Annandale, 1895

It is not so surprising that after a hundred years the conjunction of the above two words now has a meaning in the context of computer storage. This book describes work on stable storage technology undertaken within the European Union ESPRIT project P5212 (FASST), as well as in the Basic Research Action QMIPS, and will be of interest to both theoreticians and pragmatists.

The focus of the book is the problem of recovering processor failures in shared memory multiprocessors. We propose an architecture designed for transparently tolerating processor failures. The main component of this architecture is  $Stable\ Memory\ (SM)$ , which provides a hardware-supported backward error recovery mechanism. This technique copes with standard caches and cache coherence protocols and avoids rollback propagation.

That the FASST project, which suffered more than the usual quota of difficulties, most notably the bankruptcy of its prime contractor, should have engendered more than the usual quota of high quality work, is a continuing source of interest for those that were involved.

Brian Coghlan Trinity College Dublin

Germán Fabregat LISITT

## Acknowledgements

The Editors would like to thank the Authors for their contributions, the various host institutions and companies for their permission to publish, and the Commission of the European Communitaires for its financial and administrative support. Finally, for the use of editing facilities, the Editors would like to thank Trinity College Dublin, Universidad Jaume I at Campus del Penyeta Roja sn, and Prof.J.Imberger of the University of Western Australia.

## **Contents**

| 1                    | Faul | lt Tolerance 19                                                                                      |

|----------------------|------|------------------------------------------------------------------------------------------------------|

|                      | 1.1  | Introduction                                                                                         |

|                      | 1.2  | Fault Tolerance Issues                                                                               |

|                      | 1.3  | Backward Error Recovery in a Shared Memory Environment                                               |

|                      | 1.4  | A Basic Recovery Protocol for a Shared Memory Environment                                            |

|                      |      | 1.4.1 Definitions                                                                                    |

|                      |      | 1.4.2 The protocol principles                                                                        |

|                      |      | 1.4.3 A more rigorous approach to the protocol                                                       |

|                      | 1.5  | Summary                                                                                              |

| 2                    | Mad  | J. 115                                                                                               |

| 4                    | 2.1  | delling         31           SMP Cache Coherence Protocols                                           |

|                      | 2.1  | 2.1.1 Berkeley Cache Coherency Protocol                                                              |

|                      | 2.2  | Analytical Modelling of SMP Caches                                                                   |

|                      | 2.2  | 2.2.1 Protocol Definitions                                                                           |

|                      |      | 2.2.2 Cache Line States                                                                              |

|                      |      |                                                                                                      |

|                      |      |                                                                                                      |

|                      |      | 2.2.4 Performance Metrics       41         2.2.5 Comparison to Numerical Simulation Results       42 |

|                      | 22   | Queueing Models that include Checkpointing and Recovery                                              |

|                      | 2.3  |                                                                                                      |

|                      | 2.4  |                                                                                                      |

|                      |      | 2.4.1 Multiprocessor system without checkpointing and recovery                                       |

|                      |      | 2.4.2 Non-degradable multiprocessor system with checkpointing and recovery                           |

|                      | 2.5  | 2.4.3 Degradable multiprocessor system with checkpointing and recovery                               |

|                      | 2.5  | Summary                                                                                              |

| 3 FASST Architecture |      |                                                                                                      |

|                      | 3.1  | The FASST Architecture                                                                               |

|                      |      | 3.1.1 Basic Features of the Stable Memory                                                            |

|                      |      | 3.1.2 Influence of cache coherence protocols                                                         |

|                      | 3.2  | Performance Evaluation                                                                               |

|                      |      | 3.2.1 Methodology and workload                                                                       |

|                      |      | 3.2.2 Experimental results                                                                           |

|                      |      | 3.2.3 Stable memory implementation                                                                   |

|                      |      | 3.2.4 Dependency management                                                                          |

|                      | 3.3  | Summary                                                                                              |

| 4 Stable Memory      |      | ole Memory 83                                                                                        |

| •                    | 4.1  | FASST Recovery Protocol                                                                              |

|                      |      | 4.1.1 Stable Memory                                                                                  |

|                      |      | 4.1.2 Dependency management                                                                          |

|                      |      | 4.1.3 Synchronization                                                                                |

|                      |      | 4.1.4 Read and Write Commands                                                                        |

|                      |      | 111.1 Items and 11110 Community                                                                      |

|   |             | 4.1.5 Behaviour of the processor initiating a commit      | 1  |

|---|-------------|-----------------------------------------------------------|----|

|   |             |                                                           | 3  |

|   |             | 4.1.7 SM behaviour during recovery operations             |    |

|   |             | 4.1.8 Atomic operations                                   |    |

|   |             | 4.1.9 Rollback due to a processor failure                 |    |

|   |             | 1                                                         |    |

|   | 4.2         | 1 1                                                       |    |

|   | 4.2         | Stable Memory Hardware                                    | -  |

|   |             | 4.2.1 Information flow                                    | -  |

|   |             | 4.2.2 Fast Serial Link                                    | -  |

|   |             | 4.2.3 Futurebus+ Interface                                | -  |

|   |             | 4.2.4 Other considerations                                | 0  |

|   |             | 4.2.5 Copy-on-write                                       | 0  |

|   |             | 4.2.6 System Interface                                    | 19 |

|   |             | 4.2.7 Initialization phase                                | 0  |

|   | 4.3         | Fault tolerance issues                                    | 1  |

|   | 4.4         | Expected performance                                      | 1  |

|   |             |                                                           |    |

| 5 | Proc        | essing Units 11                                           | 5  |

|   | 5.1         | Fail-stop Processors                                      | 6  |

|   | 5.2         | Futurebus+                                                |    |

|   | U. <u>_</u> | 5.2.1 Data Transfer Bus                                   |    |

|   |             | 5.2.2 Arbitration bus and system coordination             |    |

|   |             | 5.2.3 Cache Coherence                                     |    |

|   |             |                                                           |    |

|   | <i>5</i> 2  |                                                           |    |

|   | 5.3         | Dual Processing Units                                     |    |

|   |             | 5.3.1 System Memory Map                                   |    |

|   |             | 5.3.2 Interrupt scheme                                    |    |

|   |             | 5.3.3 Arbitration Messages                                |    |

|   | 5.4         | The Demonstrator                                          |    |

|   | 5.5         | <i>DPU</i> Prototype                                      |    |

|   |             | 5.5.1 Intel i486/DX2 Bus Subsystem                        | .5 |

|   |             | 5.5.2 Comparators and error control                       | :5 |

|   |             | 5.5.3 Cache memory and controller                         | 5  |

|   |             | 5.5.4 <i>Host Bus</i> subsystem                           | 6  |

|   |             | 5.5.5 FB FPLA EPLD                                        | 6  |

|   |             | 5.5.6 CSR LMC FPLA and CSR Bus subsystem                  |    |

|   |             | 5.5.7 Futurebus+ interface                                |    |

|   |             | 5.5.8 Support and Miscellaneous Logic                     |    |

|   |             | 5.5.9 Error detection levels                              |    |

|   | 5.6         | DPU Demonstrator software                                 |    |

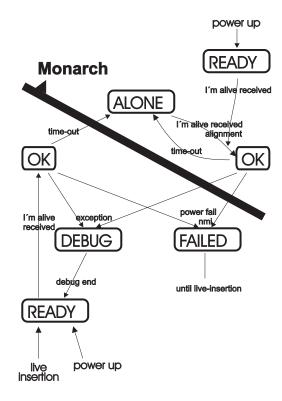

|   | 5.0         | 5.6.1 Event-driven State Machine                          | _  |

|   |             |                                                           | _  |

|   | <i>5</i> 7  | 11                                                        |    |

|   | 5.7         | Evaluation of the dependability of the $DPU$ Demonstrator |    |

|   | 5.8         | Summary                                                   | 8  |

| _ | Cana        | u-Joury Changes                                           | 'n |

| 6 |             | ndary Storage 13                                          |    |

|   | 6.1         | Secondary Storage                                         |    |

|   |             | 6.1.1 Disk Arrays                                         |    |

|   | 6.2         | Redundant Arrays of Independent Disks (RAID)              |    |

|   |             | 6.2.1 Taxonomy of RAID                                    | 1  |

|   |             | 6.2.2 The First RAID Prototype                            | 5  |

|   | 6.3         | Stable Disk                                               | 5  |

|   | 6.4         | RAID Controller for the Stable Disk                       | -7 |

|   |             | 6.4.1 Information Flow                                    | .9 |

|   |             | 6.4.2 nMR Operation                                       | 0  |

|   |             |                                                           |    |

|   | 6.5 | Stable Memory for the Stable Disk                                                                                  |

|---|-----|--------------------------------------------------------------------------------------------------------------------|

|   |     | 6.5.1 Intra-bank Checkpointing                                                                                     |

|   |     | 6.5.2 Inter-bank Checkpointing                                                                                     |

|   |     | 6.5.3 Log-mode Checkpointing                                                                                       |

|   |     | 6.5.4 Switch-mode Checkpointing                                                                                    |

|   |     | 6.5.5 Protection Logic                                                                                             |

|   | 6.6 | Integration into the FASST Recovery Protocol                                                                       |

|   |     | 6.6.1 Dependency management                                                                                        |

|   |     | 6.6.2 Synchronisation                                                                                              |

|   |     | 6.6.3 Read and Write Commands                                                                                      |

|   |     | 6.6.4 Behaviour of the processor initiating a commit                                                               |

|   |     | 6.6.5 Behaviour of other processors                                                                                |

|   |     | 6.6.6 Stable device behaviour during recovery operations                                                           |

|   |     | 6.6.7 Atomic operations                                                                                            |

|   |     | 6.6.8 Rollback due to a processor failure                                                                          |

|   |     | 6.6.9 Various primitives used in the protocol description                                                          |

|   | 6.7 | Influence on performance                                                                                           |

| , | C4  | Co-84-mous                                                                                                         |

| ′ | -   | em Software System software principles                                                                             |

|   | 7.1 | 7 1 1                                                                                                              |

|   |     | •                                                                                                                  |

|   |     |                                                                                                                    |

|   |     | 7.1.3 Standard vs non-standard processes                                                                           |

|   | 7.0 | 7.1.4 Memory management                                                                                            |

|   | 7.2 | The Mach Microkernel                                                                                               |

|   | 7.3 | OSF1/mk                                                                                                            |

|   |     | 7.3.1 BSD Server                                                                                                   |

|   |     | 7.3.2 Source Tree of OSF1/mk         185           7.3.3 Monoprocessor & Multiprocessor Configurations         186 |

|   |     |                                                                                                                    |

|   |     | 7.3.4 Compilations: Scripts, Makefiles & Configurations                                                            |

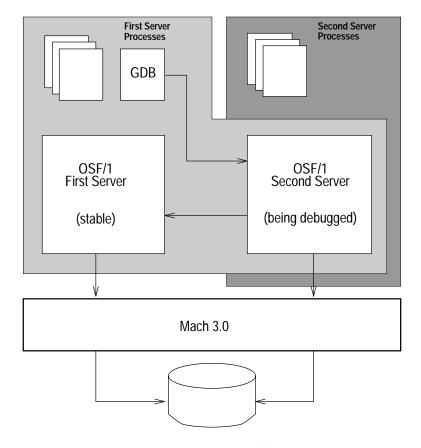

|   |     | 7.3.6 Debugging a Server                                                                                           |

|   | 7.4 | System Call Extensions to a Server                                                                                 |

|   | 7.4 | ·                                                                                                                  |

|   |     | 7.4.1 Adding the mq open System Call                                                                               |

|   | 7.5 | Driver Extensions to the Microkernel                                                                               |

|   | 1.5 | 7.5.1 Developing Device Drivers in User-Space                                                                      |

|   |     | 7.5.1 Developing Device Drivers in Oser-space                                                                      |

|   |     | 7.5.3 Dynamically Adding Device Drivers                                                                            |

|   |     | 7.5.4 Binding Threads to I/O Capable CPUs                                                                          |

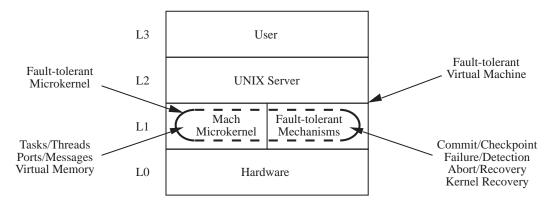

|   | 7.6 | Fault Tolerance Extensions to the Microkernel                                                                      |

|   | 7.0 | 7.6.1 Fault Tolerant Mechanisms required in the Microkernel                                                        |

|   |     | 7.6.2 Checkpointing                                                                                                |

|   |     | 7.6.3 Rollback                                                                                                     |

|   |     | 7.6.4 Standard and Non-standard processes                                                                          |

|   | 7.7 | Unresolved Microkernel Issues                                                                                      |

|   | 7.7 | Proposal 1: Boot process handling                                                                                  |

|   | 7.0 | 7.8.1 Mach booting                                                                                                 |

|   |     | 7.8.2 An implementation proposal for boot handling                                                                 |

|   | 7.9 | Proposal 2 : Non-standard I/O process handling                                                                     |

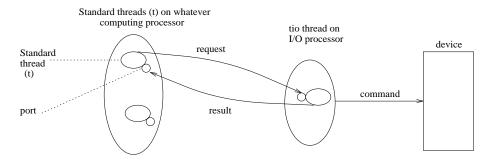

|   | 1.9 | 7.9.1 I/O handling in Sequoia                                                                                      |

|   |     | 7.9.2 Reliable I/O Design Principles                                                                               |

|   |     | 7.9.3 Device management in the Mach microkernel                                                                    |

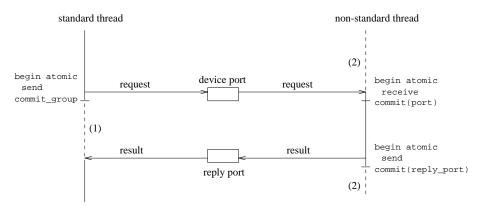

|   |     | 7.9.4 A first implementation proposal for reliable I/O                                                             |

|   |     |                                                                                                                    |

| 7.9.5 | A second implementation proposal for reliable I/O | 226 |

|-------|---------------------------------------------------|-----|

| 7.9.6 | Comments                                          | 229 |

# **List of Figures**

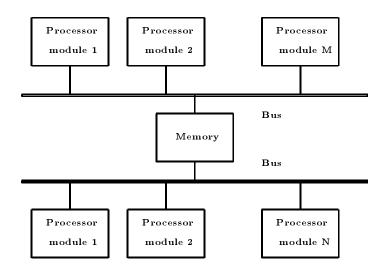

| 1.1  | A typical shared memory architecture                                                               | 20 |

|------|----------------------------------------------------------------------------------------------------|----|

| 1.2  | Communicating processes and recovery                                                               | 25 |

| 2.1  | De la la contrata de mariel de la Processa                                                         | 22 |

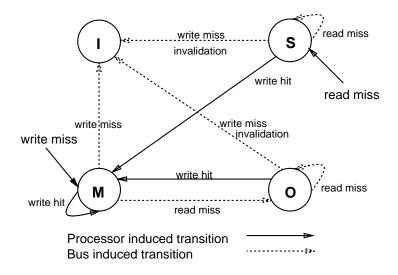

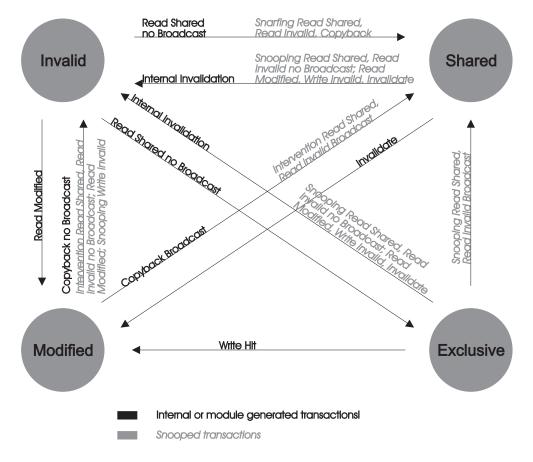

| 2.1  | Berkeley state transition diagram                                                                  | 33 |

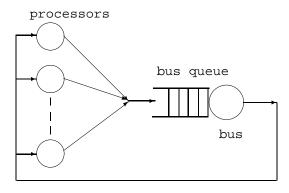

| 2.2  | A multiprocessor system                                                                            | 34 |

| 2.3  | The cache queue                                                                                    | 39 |

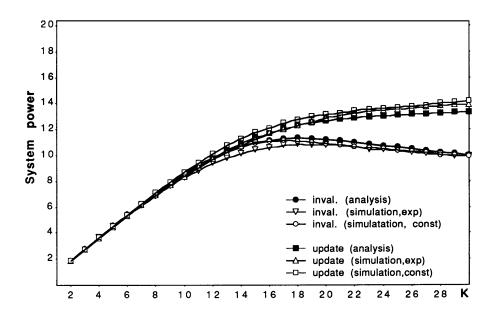

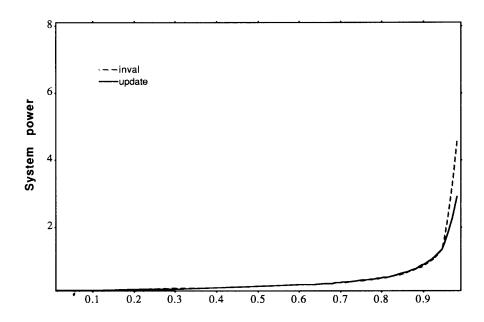

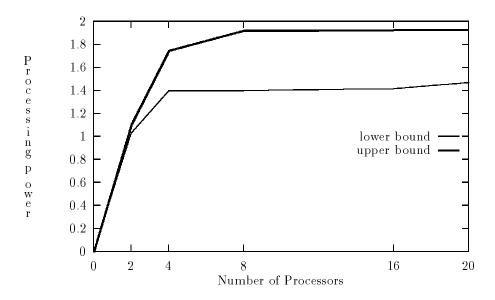

| 2.4  | System power versus number of processors, $\alpha = 0.85$ , $\gamma = 0.8$                         | 43 |

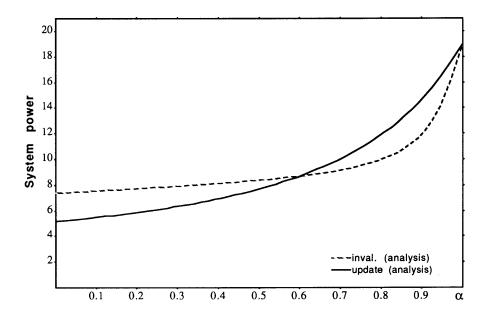

| 2.5  | System power versus <i>read</i> probability, $K = 25$ , $\gamma = 0.8$                             | 43 |

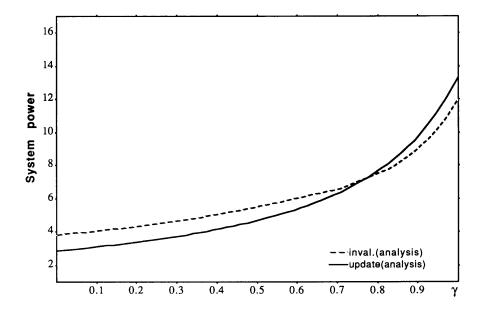

| 2.6  | System power versus <i>hit</i> probability, $K = 25$ , $\alpha = 0.5$                              | 44 |

| 2.7  | System power versus <i>hit</i> probability, $K = 8$ , $\alpha = 0.95$                              | 44 |

| 2.8  | Two multiprocessing nodes connected to a single shared memory                                      | 45 |

| 2.9  | Processor Model                                                                                    | 46 |

|      | Simplified Processor Model                                                                         | 46 |

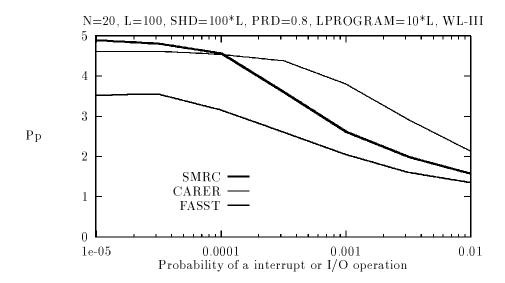

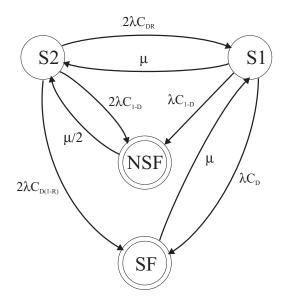

|      | FASST queueing model                                                                               | 49 |

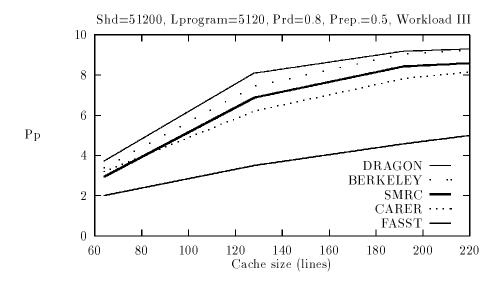

|      | Influence of cache size on performance                                                             | 50 |

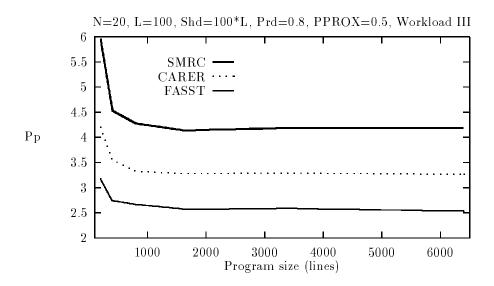

|      | Influence of program size on performance                                                           | 50 |

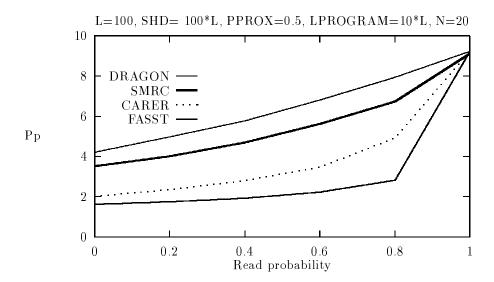

| 2.14 | Influence of read probability on performance                                                       | 51 |

| 2.15 | Influence of the checkpointing rate on performance                                                 | 51 |

| 2.16 | Reliability for a multiprocessor system without checkpointing and recovery                         | 52 |

| 2.17 | Availability for a multiprocessor system without checkpointing and recovery                        | 52 |

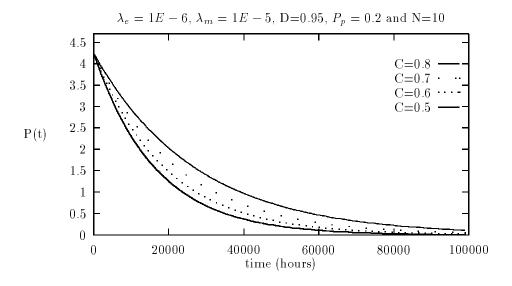

| 2.18 | Influence of the processor and memory fault rates on the performability of a multiprocessor system |    |

|      | without checkpointing and recovery                                                                 | 53 |

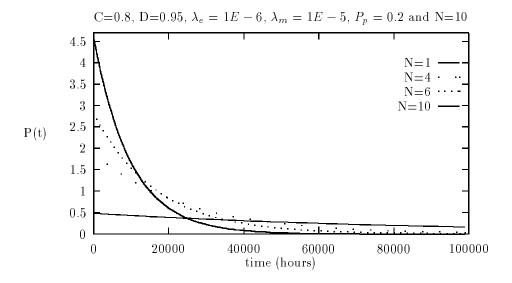

| 2.19 | Influence of the number of processors on the performability of a multiprocessor system without     |    |

|      | checkpointing and recovery                                                                         | 53 |

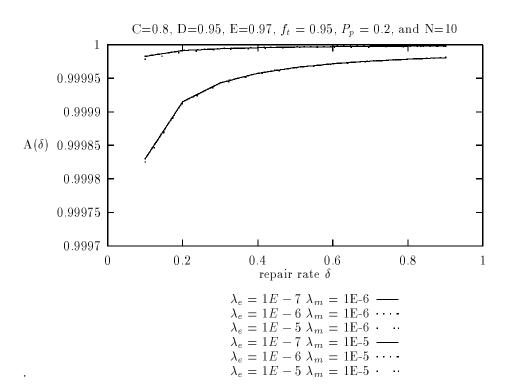

| 2.20 | Reliability for a non-degradable (CARER) multiprocessor system with checkpointing and recovery     | 54 |

| 2.21 | Availability for a non-degradable (CARER) multiprocessor system with checkpointing and recovery    | 54 |

| 2.22 | Influence of processor and memory fault rates on the performability of a non-degradable (CARER)    |    |

|      | multiprocessor system with checkpointing and recovery                                              | 55 |

| 2.23 | Influence of transient fault coverage on the performability of a non-degradable (CARER) multi-     |    |

|      | processor system with checkpointing and recovery                                                   | 55 |

| 2.24 | Influence of permanent fault rate on the performability of a non-degradable (CARER) multipro-      |    |

|      | cessor system with checkpointing and recovery                                                      | 56 |

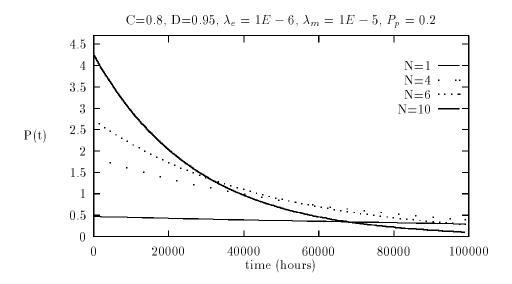

| 2.25 | Influence of the number of processors on the performability of a non-degradable (CARER) multi-     |    |

|      | processor system with checkpointing and recovery                                                   | 56 |

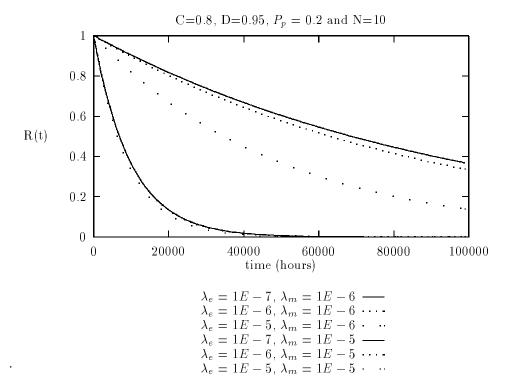

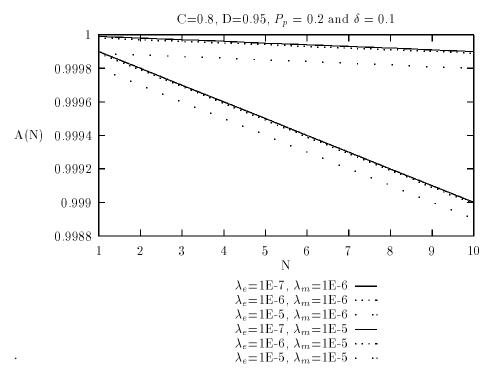

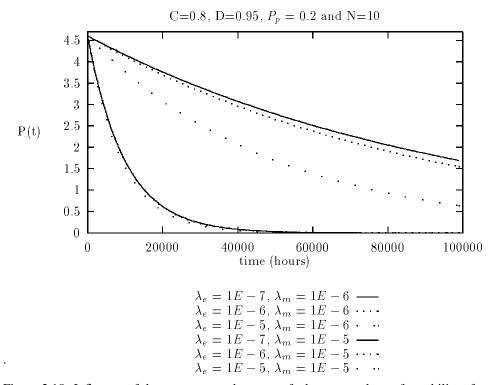

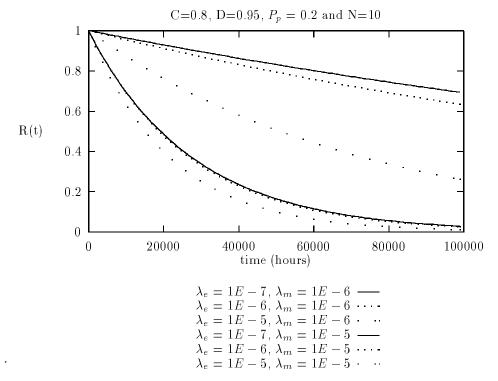

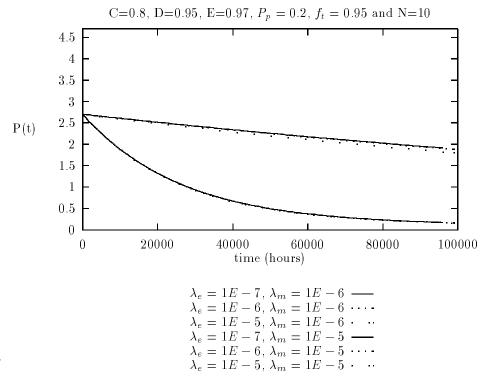

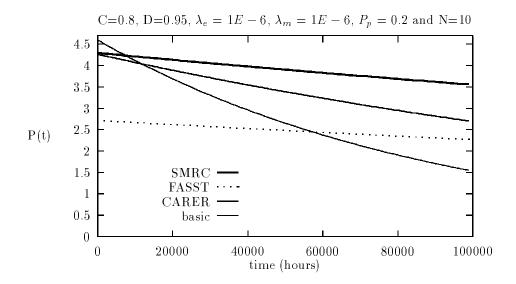

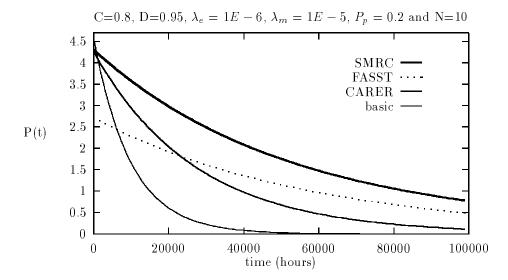

| 2.26 | Reliability for a degradable (FASST) multiprocessor system with checkpointing and recovery         | 57 |

| 2.27 | Availability for a degradable (FASST) multiprocessor system with checkpointing and recovery        | 57 |

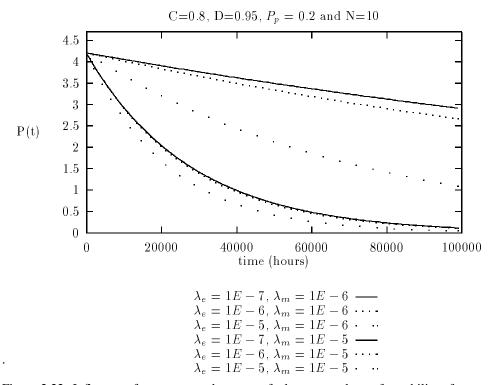

| 2.28 | Influence of processor and memory fault rates on the performability of a degradable (FASST)        |    |

|      | multiprocessor system with checkpointing and recovery                                              | 58 |

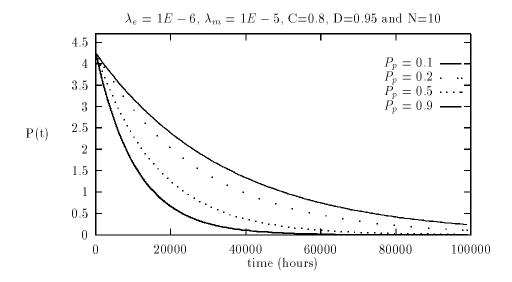

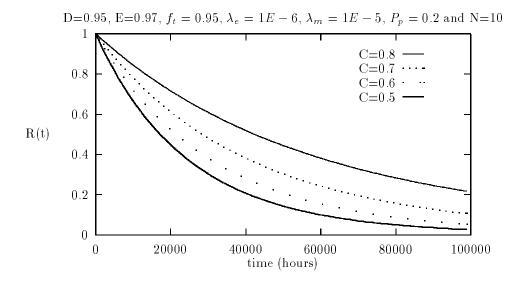

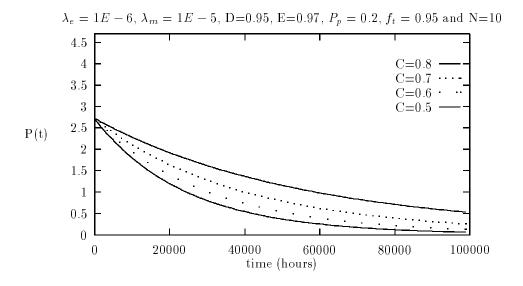

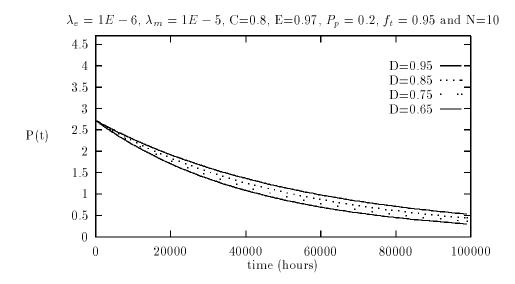

| 2.29 | Influence of transient fault coverage on the performability of a degradable (FASST) multiprocessor |    |

|      | system with checkpointing and recovery                                                             | 58 |

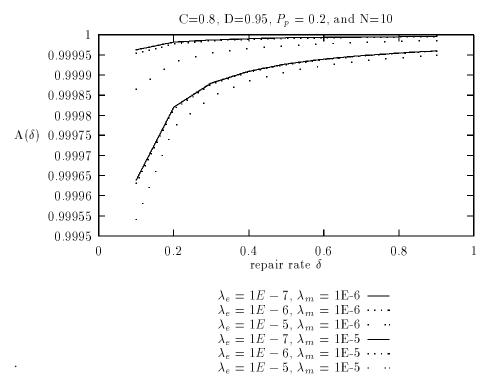

| 2.30 | Influence of permanent fault coverage on the performability of a degradable (FASST) multiproces-   |    |

|      | sor system with checkpointing and recovery                                                         | 59 |

| 2.31 | Influence of permanent fault rate on the performability of a degradable (FASST) multiprocessor                                                                                           |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|      | system with checkpointing and recovery                                                                                                                                                   |  |  |  |  |  |

| 2.32 | 2 Influence of the number of processors on the performability of a degradable (FASST) multiproces-                                                                                       |  |  |  |  |  |

|      | sor system with checkpointing and recovery                                                                                                                                               |  |  |  |  |  |

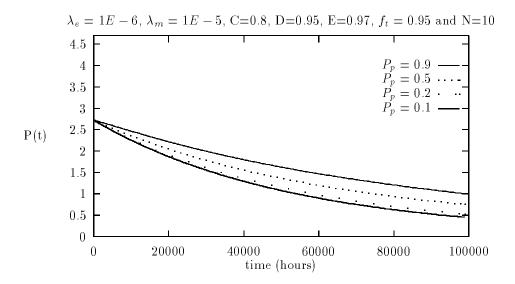

| 2.33 | Performability comparison with memory fault rate $\lambda_m = 10^{-6} \dots \dots$ |  |  |  |  |  |

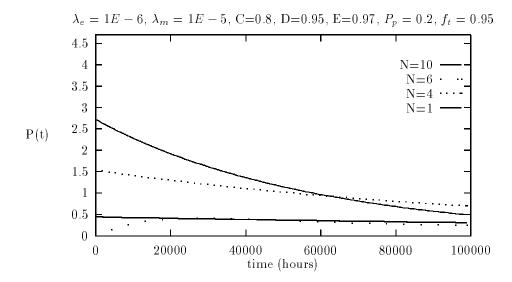

| 2.34 | Performability comparison with memory fault rate $\lambda_m = 10^{-6}$                                                                                                                   |  |  |  |  |  |

| 2.35 | Processing power for cache coherent dual bus model using the Write-Once protocol 61                                                                                                      |  |  |  |  |  |

|      | Upper bound model for cache coherent dual bus                                                                                                                                            |  |  |  |  |  |

|      | Lower bound model for cache coherent dual bus                                                                                                                                            |  |  |  |  |  |

|      |                                                                                                                                                                                          |  |  |  |  |  |

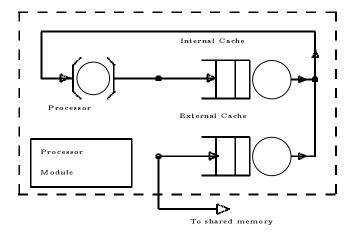

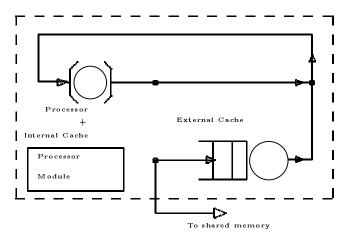

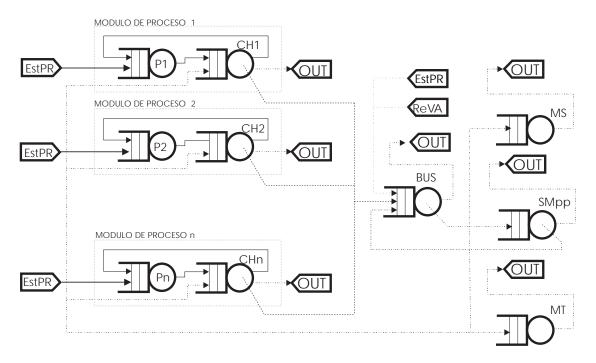

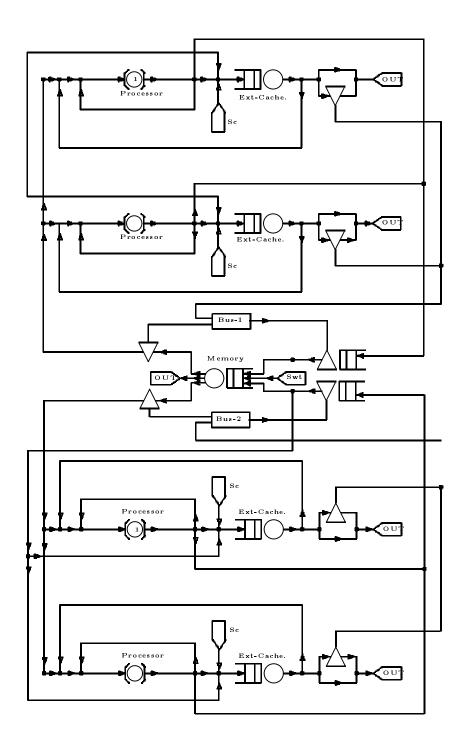

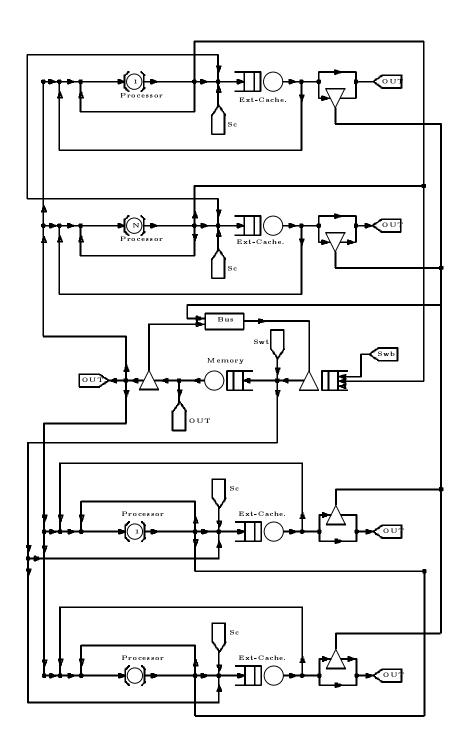

| 3.1  | The FASST architecture                                                                                                                                                                   |  |  |  |  |  |

| 3.2  | Computing a dependency group                                                                                                                                                             |  |  |  |  |  |

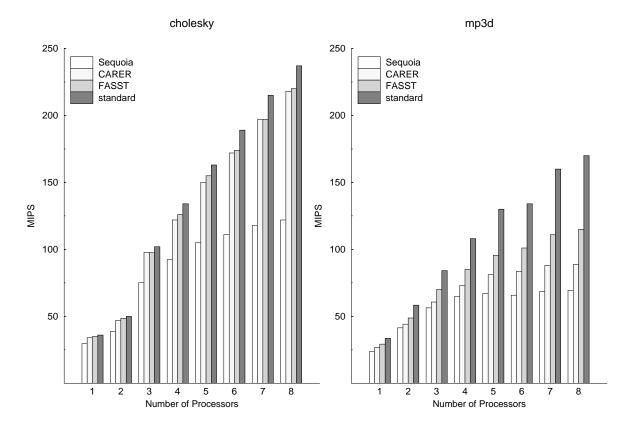

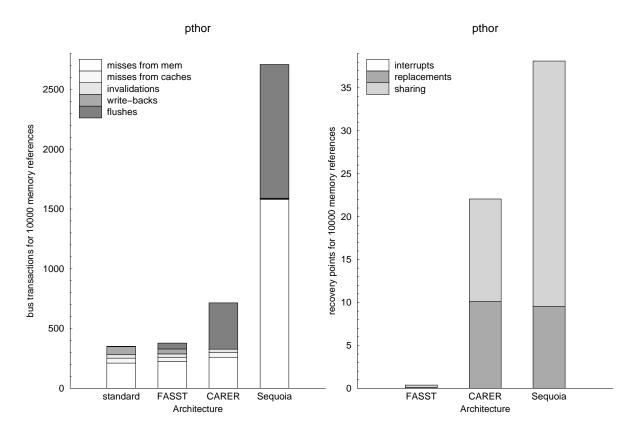

| 3.3  | Performance                                                                                                                                                                              |  |  |  |  |  |

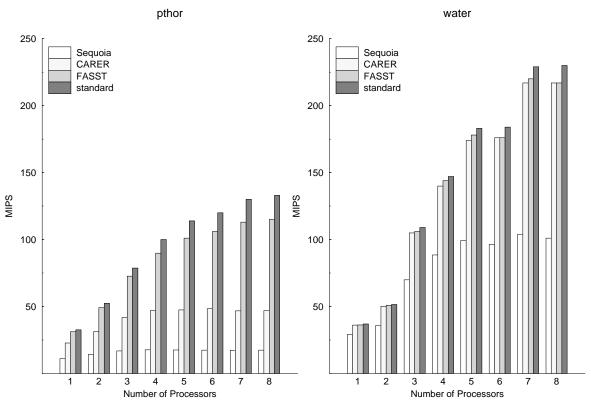

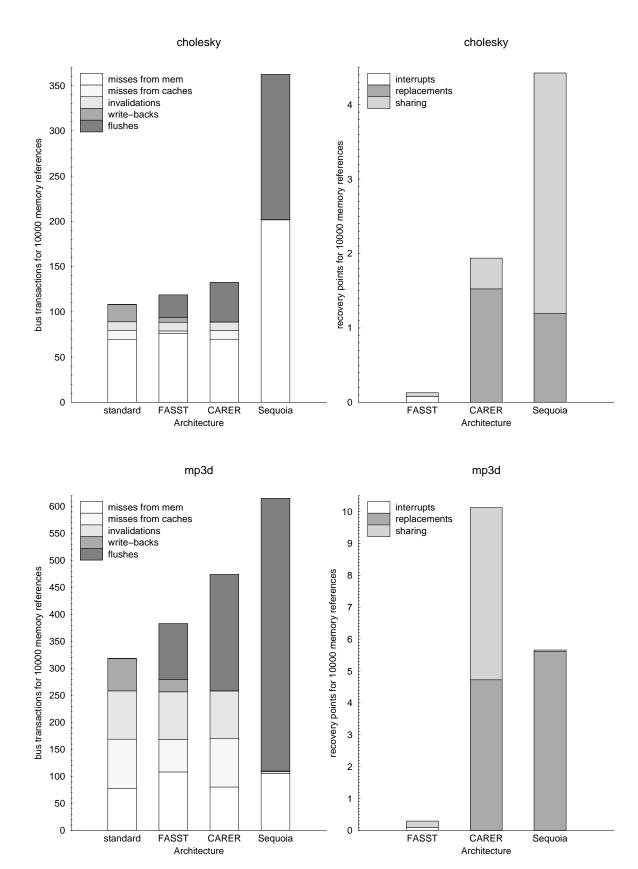

| 3.4  | Application behaviour with 8 processors                                                                                                                                                  |  |  |  |  |  |

| 3.5  | Application behaviour with 8 processors                                                                                                                                                  |  |  |  |  |  |

| 3.6  | Stable memory implementation                                                                                                                                                             |  |  |  |  |  |

| 3.7  | efficiency of dependency management                                                                                                                                                      |  |  |  |  |  |

|      |                                                                                                                                                                                          |  |  |  |  |  |

| 4.1  | The FASST architecture                                                                                                                                                                   |  |  |  |  |  |

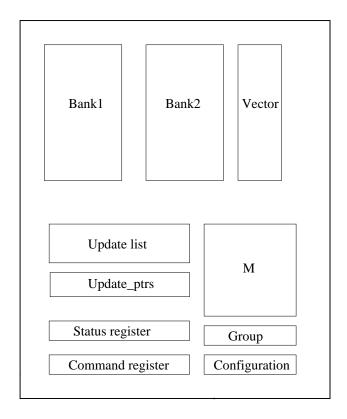

| 4.2  | Stable memory structure                                                                                                                                                                  |  |  |  |  |  |

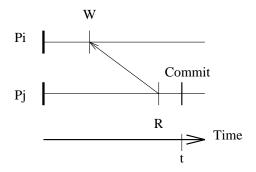

| 4.3  | Read after write dependency: Commit                                                                                                                                                      |  |  |  |  |  |

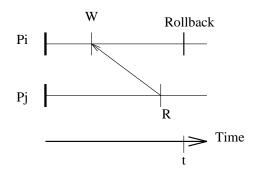

| 4.4  | Read after write dependency: Rollback                                                                                                                                                    |  |  |  |  |  |

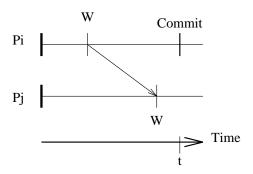

| 4.5  | Write after write dependency: Commit                                                                                                                                                     |  |  |  |  |  |

| 4.6  | Write after write dependency: <i>Rollback</i>                                                                                                                                            |  |  |  |  |  |

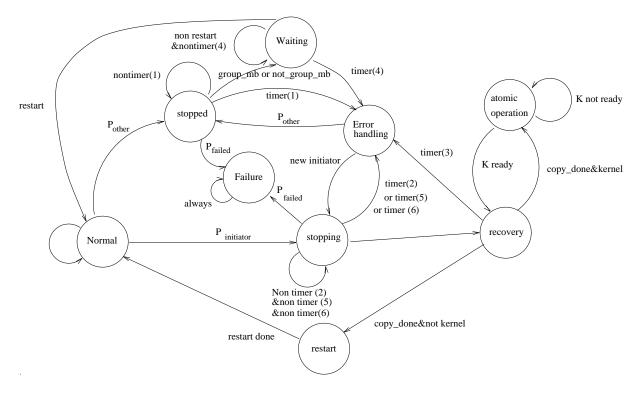

| 4.7  | Processor automaton                                                                                                                                                                      |  |  |  |  |  |

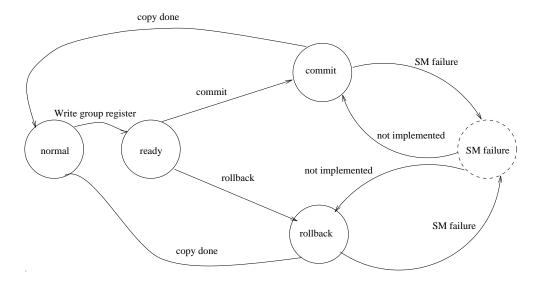

| 4.8  | <i>SM</i> states                                                                                                                                                                         |  |  |  |  |  |

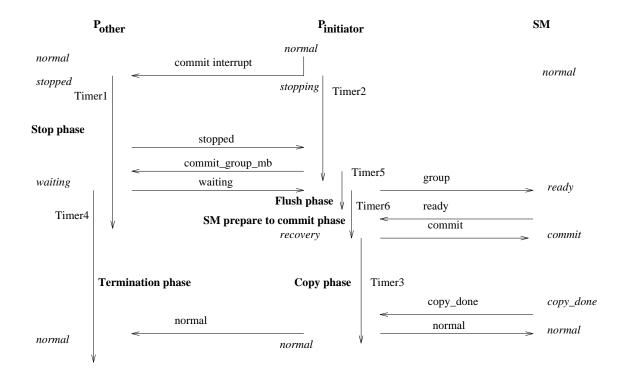

| 4.9  | Timeout protection                                                                                                                                                                       |  |  |  |  |  |

|      | Atomic operation                                                                                                                                                                         |  |  |  |  |  |

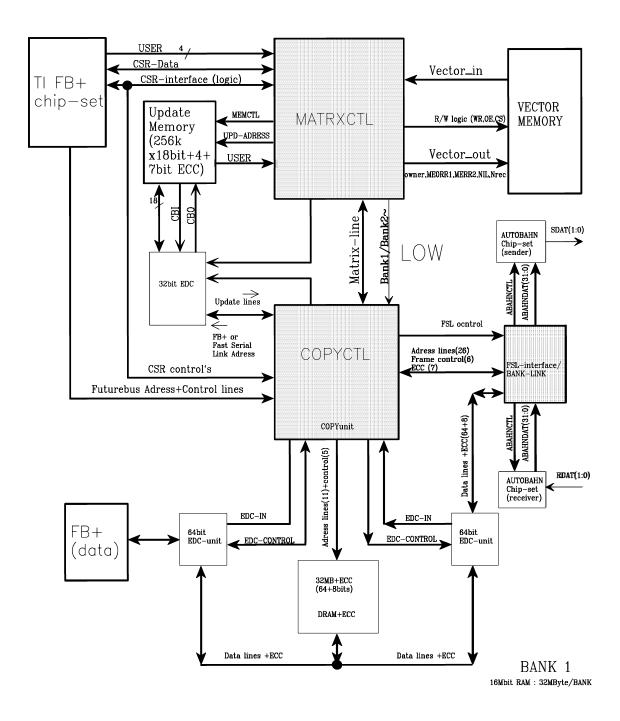

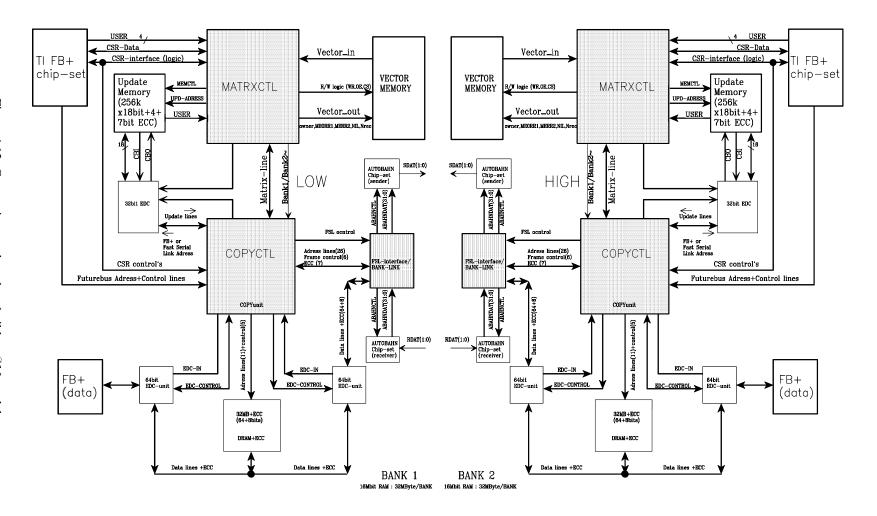

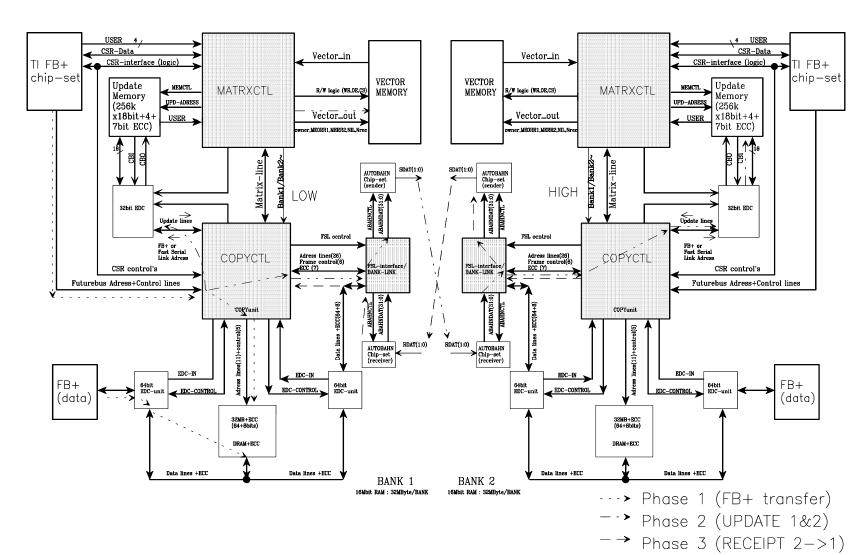

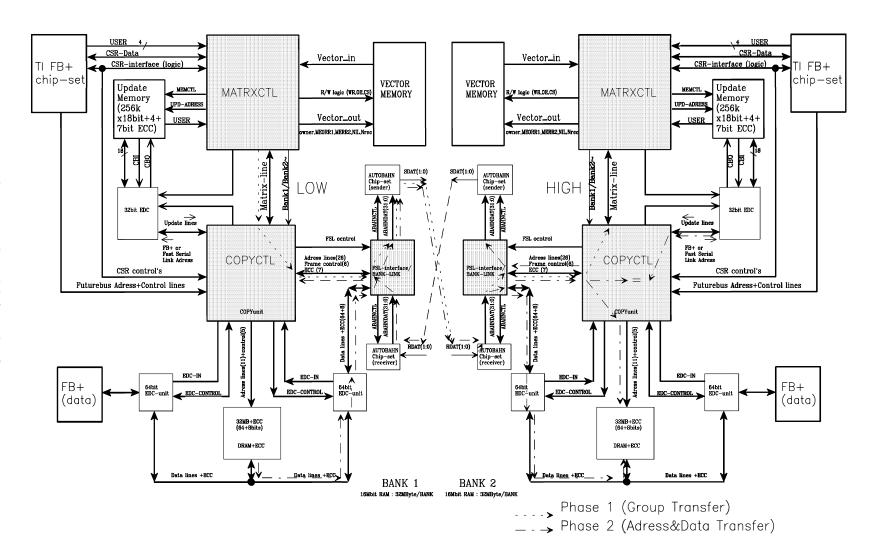

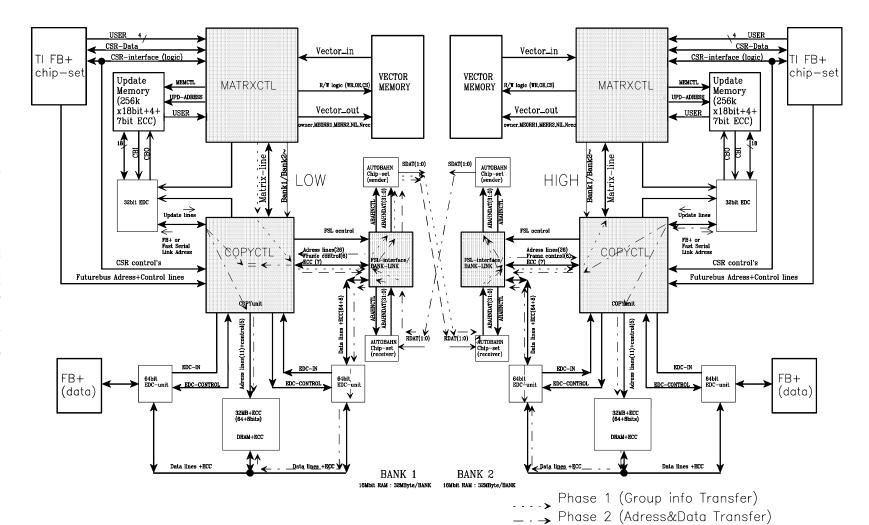

|      | SM board block diagram                                                                                                                                                                   |  |  |  |  |  |

|      | Connecting two boards to build an $SM$ module                                                                                                                                            |  |  |  |  |  |

|      | Update information flow                                                                                                                                                                  |  |  |  |  |  |

| 1.13 | Commit information flow                                                                                                                                                                  |  |  |  |  |  |

|      | Rollback information flow                                                                                                                                                                |  |  |  |  |  |

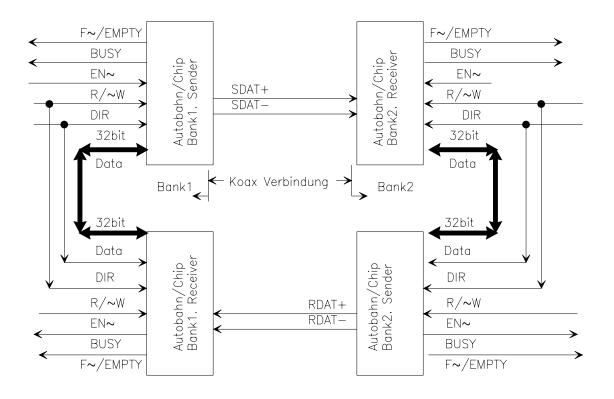

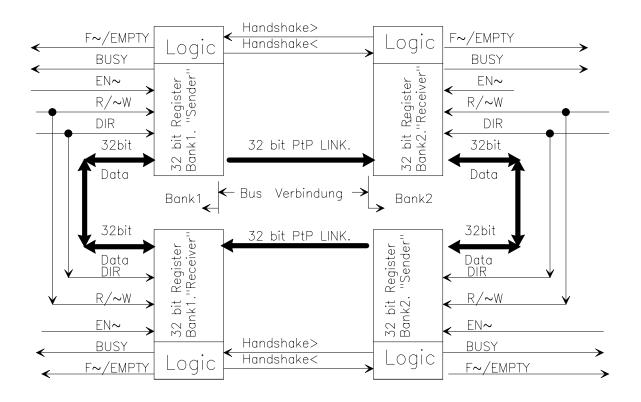

|      | Autobahn chipset                                                                                                                                                                         |  |  |  |  |  |

|      | Autobahn chipset emulation                                                                                                                                                               |  |  |  |  |  |

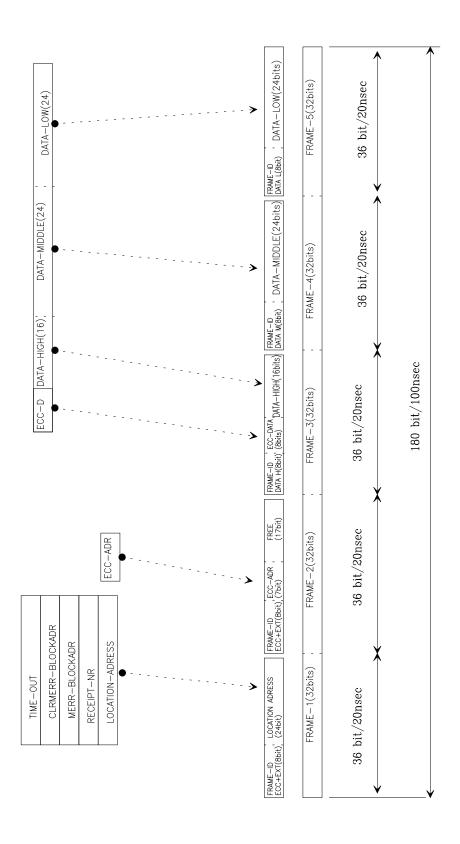

|      | Frame format and frames used                                                                                                                                                             |  |  |  |  |  |

|      |                                                                                                                                                                                          |  |  |  |  |  |

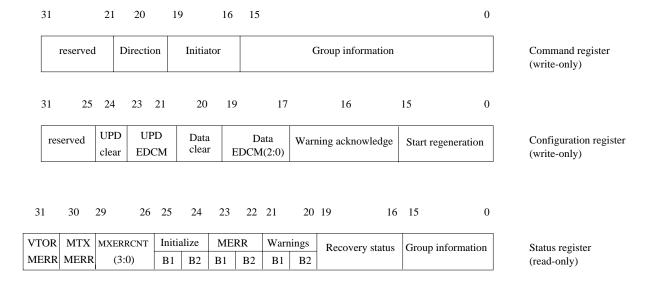

|      | <i>SM</i> registers                                                                                                                                                                      |  |  |  |  |  |

|      | Vector information                                                                                                                                                                       |  |  |  |  |  |

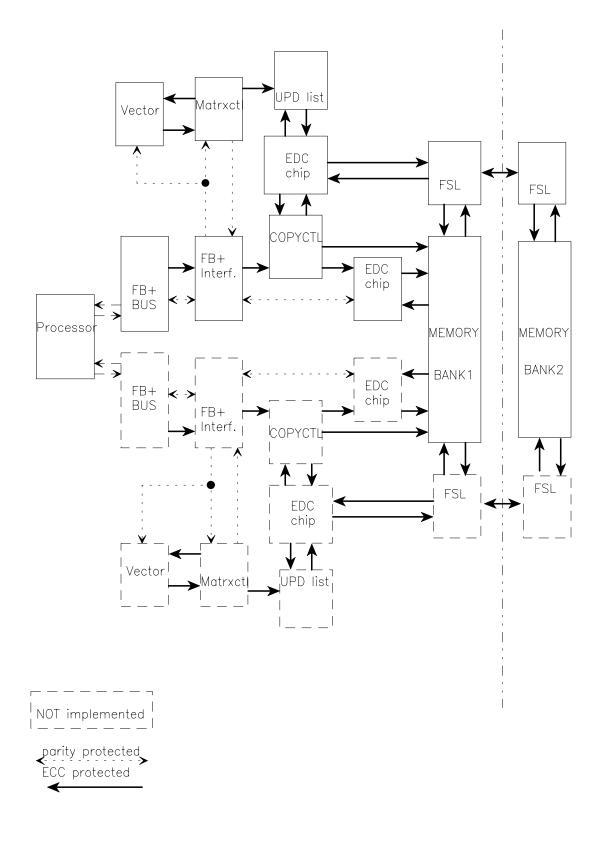

| 4.21 | SM information flow                                                                                                                                                                      |  |  |  |  |  |

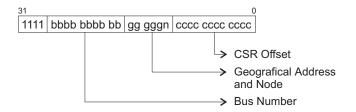

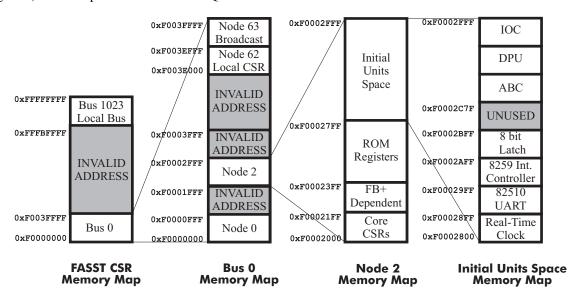

| 5.1  | CSR Space Address Format                                                                                                                                                                 |  |  |  |  |  |

| 5.2  | Futurebus+ Cache Coherence Protocol                                                                                                                                                      |  |  |  |  |  |

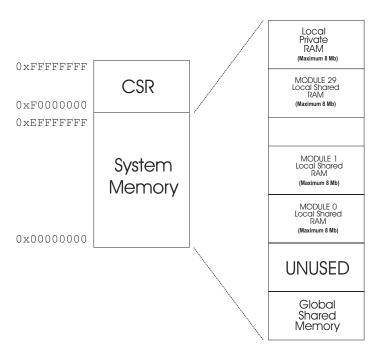

| 5.3  | DPU System Memory Map                                                                                                                                                                    |  |  |  |  |  |

|      | •                                                                                                                                                                                        |  |  |  |  |  |

| 5.4  |                                                                                                                                                                                          |  |  |  |  |  |

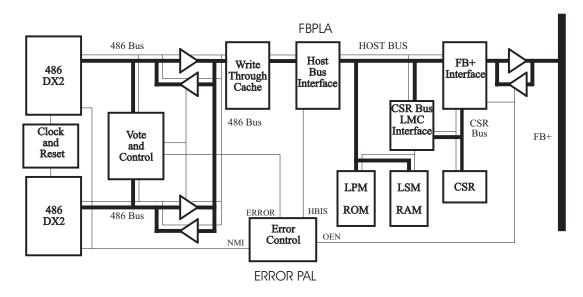

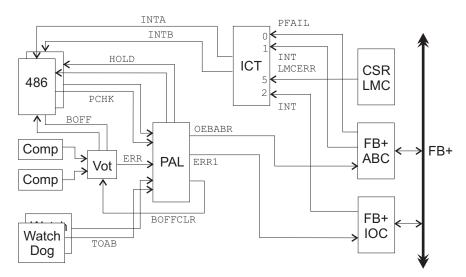

| 5.5  | Block Diagram of the <i>DPU</i>                                                                                                                                                          |  |  |  |  |  |

| 5.6  | Bus 0, Node 2, CSR memory map                                                                                                                                                            |  |  |  |  |  |

| 5.7  | Error detection hierarchy                                                                                                                                                                |  |  |  |  |  |

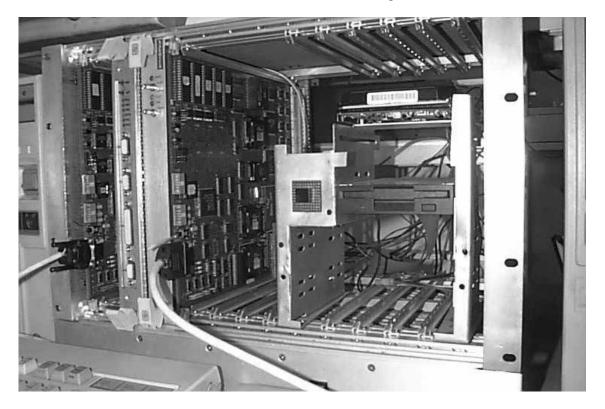

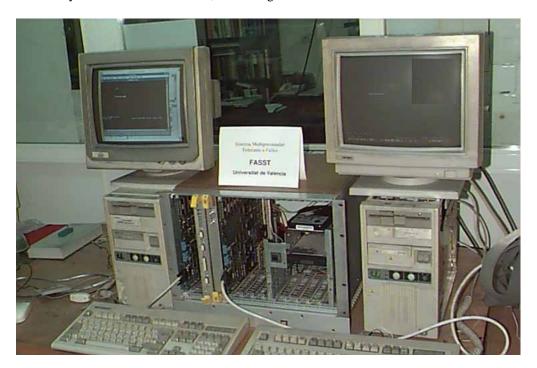

| 5.8  | Photograph of the application execution environment                                                                                                                                      |  |  |  |  |  |

| 5.9  | ESM module structure                                                                                                                                                                     |  |  |  |  |  |

|      | Macroscopic model                                                                                                                                                                        |  |  |  |  |  |

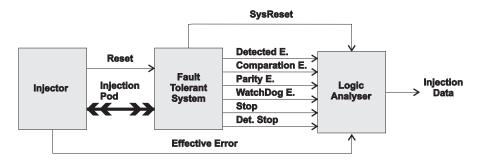

| 5.11 | The injection environment                                                                                                                                                                |  |  |  |  |  |

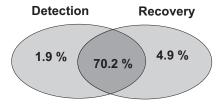

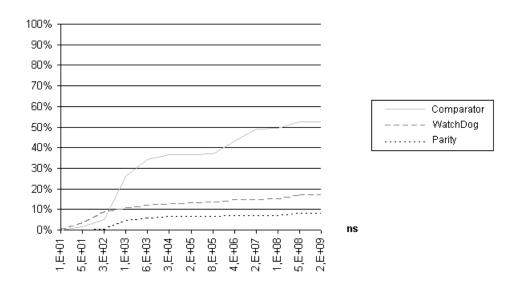

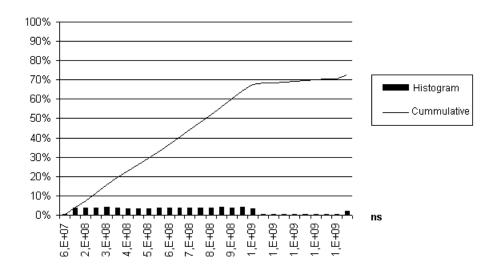

|      | DPU Demonstrator coverages                                                                                                                                                               |  |  |  |  |  |

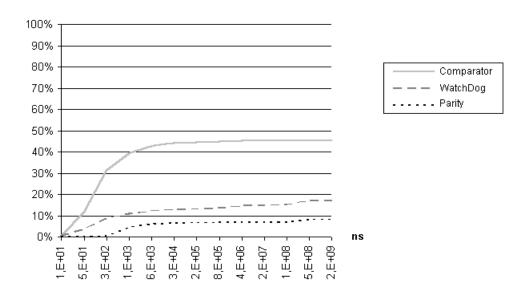

|      | Error detection coverages versus time                                                                                                                                                    |  |  |  |  |  |

|      | Module halt coverages versus time                                                                                                                                                        |  |  |  |  |  |

| 5.15 | System reconfiguration coverages versus time                                                                                                                                             |  |  |  |  |  |

| <i>c</i> 1 | DAID L. 12                                                                                    | 1.42 |

|------------|-----------------------------------------------------------------------------------------------|------|

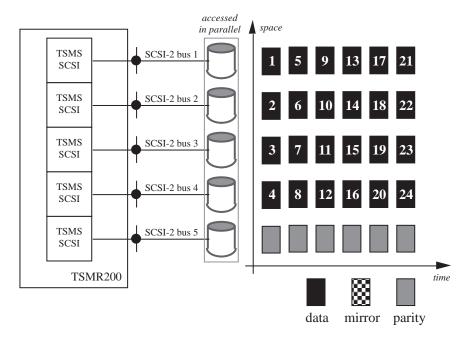

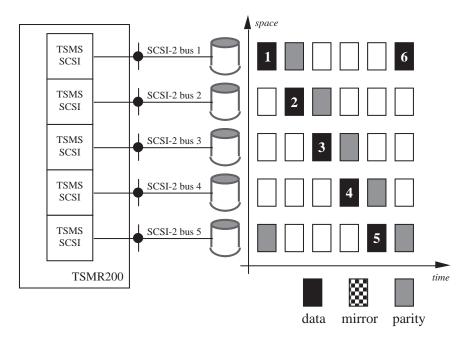

| 6.1        | RAID Level 3                                                                                  |      |

| 6.2        | RAID Level 5                                                                                  |      |

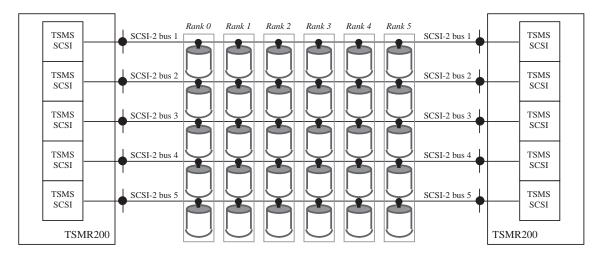

| 6.3        | Multiple Rank RAID with Duplex Controllers                                                    |      |

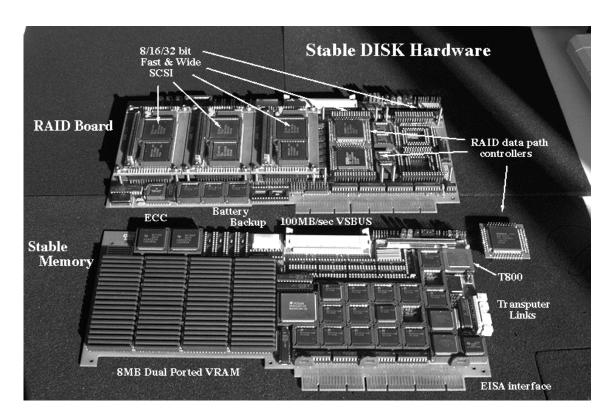

| 6.4        | Stable Disk: RAID Controller and Stable Memory                                                |      |

| 6.5        | Stable Disk: RAID Chassis and Corollary host                                                  |      |

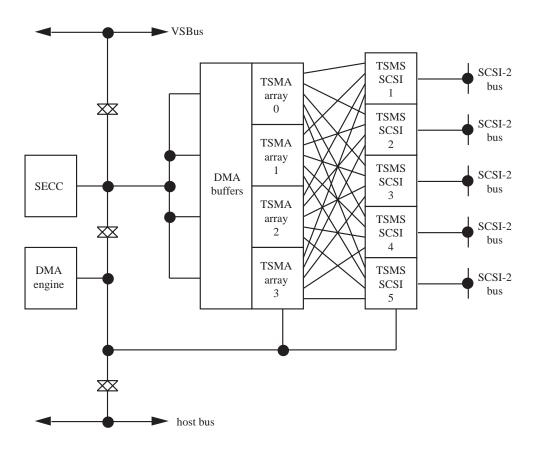

| 6.6        | RAID Controller Block Diagram                                                                 |      |

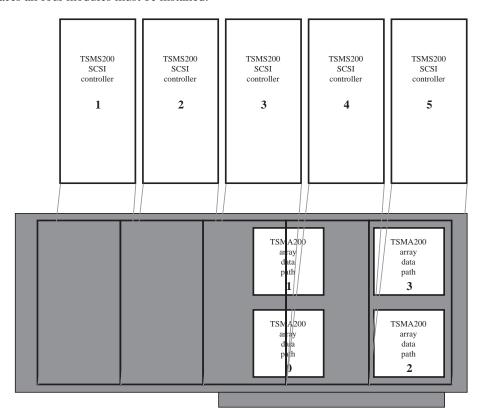

| 6.7        | Layout of modules on the RAID Controller                                                      | 148  |

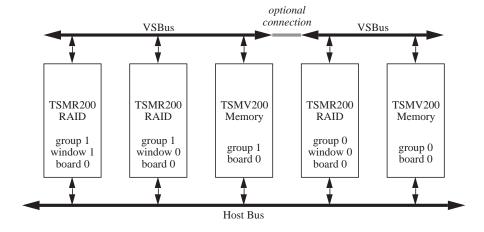

| 6.8        | Interconnection of RAID Controllers and Stable Memories using the VSBus                       | 150  |

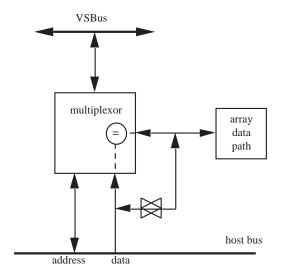

| 6.9        | Bus Interface/Comparator for nMR Operation                                                    | 150  |

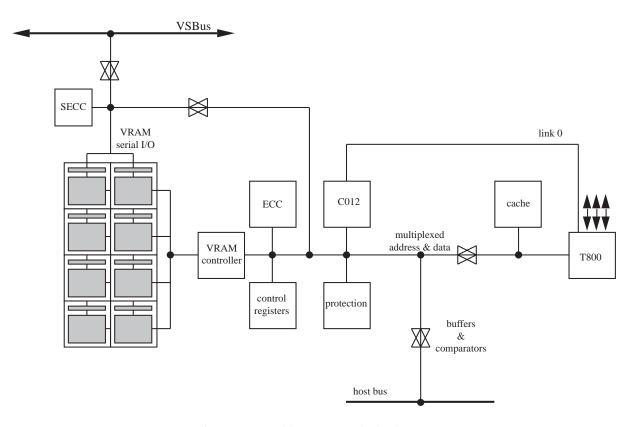

| 6.10       | Stable Memory Block Diagram                                                                   | 152  |

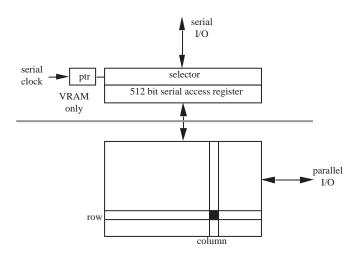

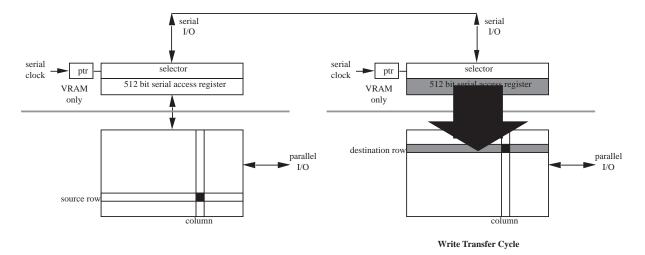

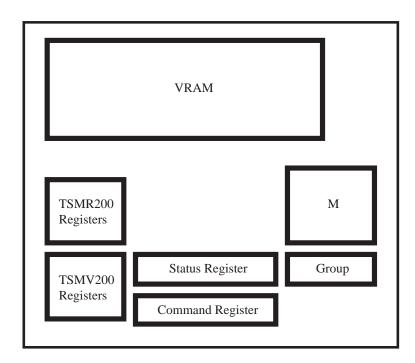

| 6.11       |                                                                                               |      |

| 6.12       | Simplified VRAM Block Diagram                                                                 |      |

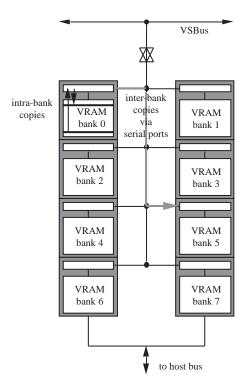

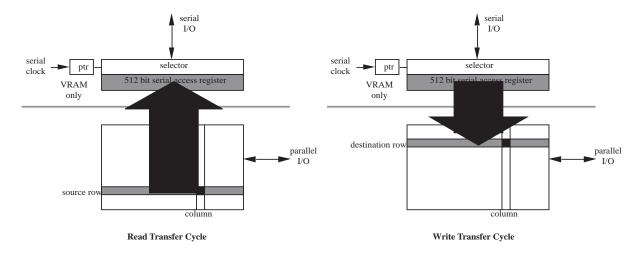

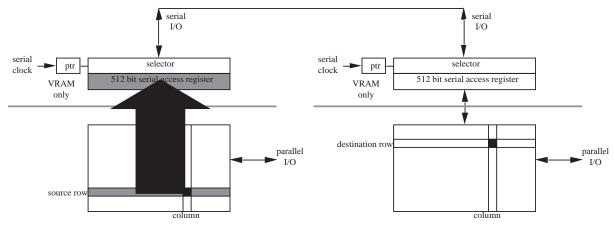

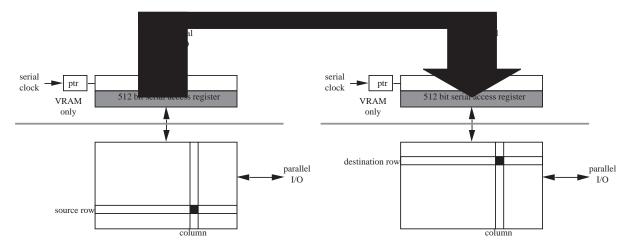

|            | Intra-bank Transfer                                                                           |      |

|            | Inter-bank Transfer                                                                           |      |

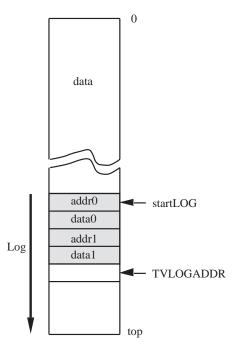

|            | One Possible VRAM Organisation for Log-mode Checkpointing                                     |      |

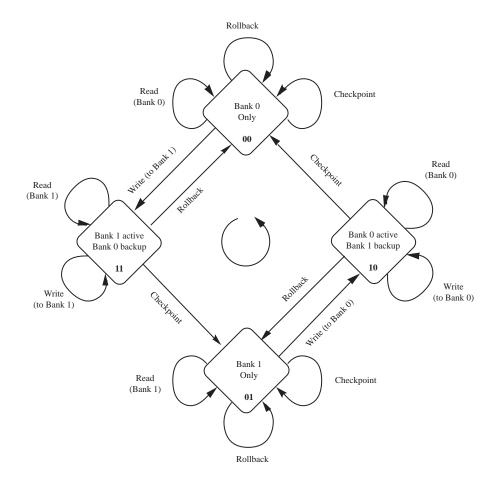

|            | Switch-mode Checkpointing State Transition Diagram for a Stable Location                      |      |

|            | Protection Logic Operation                                                                    |      |

|            | Stable Disk logical structure                                                                 |      |

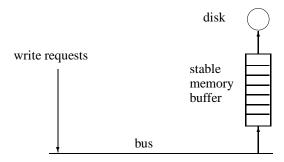

|            | Buffered disk requests                                                                        |      |

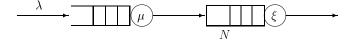

|            | A two-node tandem network model                                                               |      |

|            |                                                                                               |      |

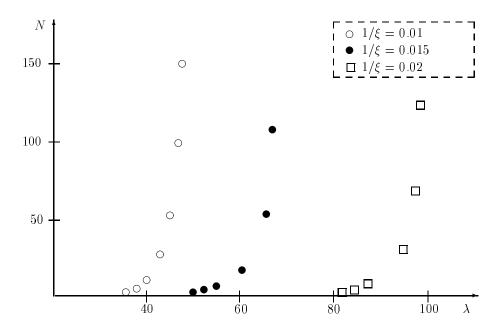

| 0.21       | Value of N such that $W \le 0.05$ sec. $1/\mu = 0.0001$                                       | 1/3  |

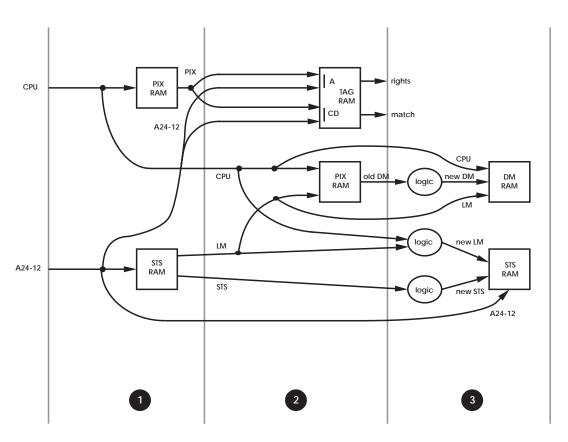

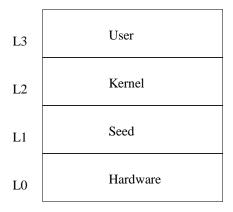

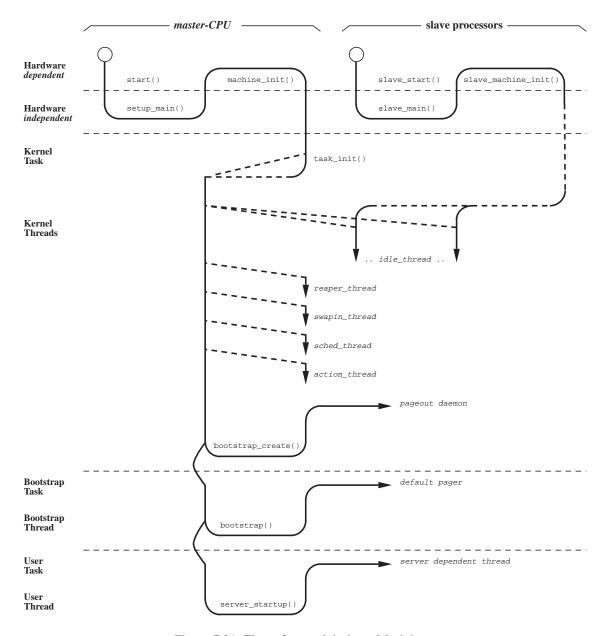

| 7.1        | Structure of the system software                                                              | 176  |

| 7.1        | The short-term scheduler: specifications                                                      |      |

| 7.2        | The short-term scheduler implementation                                                       |      |

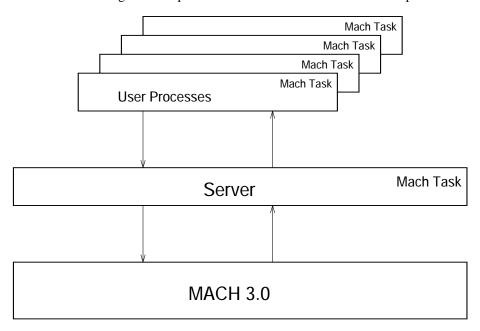

| 7.3<br>7.4 | Overview of OSF1/mk software architecture                                                     |      |

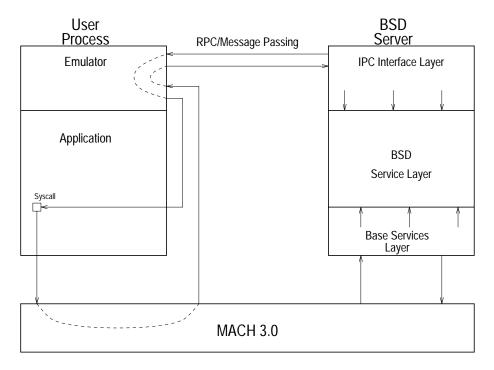

|            |                                                                                               |      |

| 7.5        | Software architecture of BSD server                                                           |      |

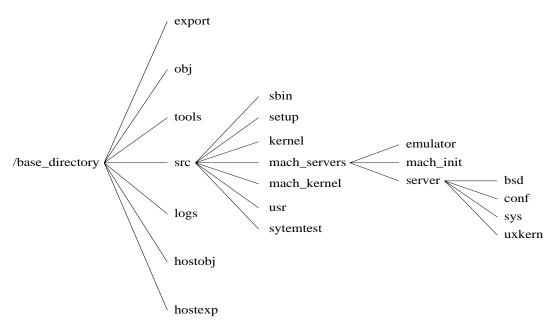

| 7.6        | Source tree of OSF1/mk Version 4.1                                                            |      |

| 7.7        |                                                                                               | 189  |

| 7.8        |                                                                                               | 189  |

| 7.9        | Virtual machine                                                                               |      |

| 7.10       |                                                                                               | 196  |

| 7.11       |                                                                                               | 196  |

|            | 1 6 6                                                                                         | 198  |

|            | Checkpointing and rollback                                                                    |      |

|            | Two dependent processes that checkpoint at context switches                                   |      |

|            | Two dependent processes that checkpoint at any time                                           | 199  |

| 7.16       | Two dependent standard processes                                                              | 200  |

| 7.17       | Dependency relationships between the processes in Figure 7.16                                 | 200  |

| 7.18       | Two dependent processes: S3 is a standard process and NS4 is a non-standard process           | 200  |

| 7.19       | A standard and a non-standard process, where dependent processes are checkpointed immediately |      |

|            | after a dependency is created                                                                 | 201  |

| 7.20       | A standard and a non-standard process, where processes are checkpointed immediately before a  |      |

|            | dependency is created                                                                         | 201  |

| 7.21       |                                                                                               | 205  |

|            |                                                                                               | 207  |

|            | ·                                                                                             | 209  |

|            |                                                                                               | 210  |

|            | •                                                                                             | 211  |

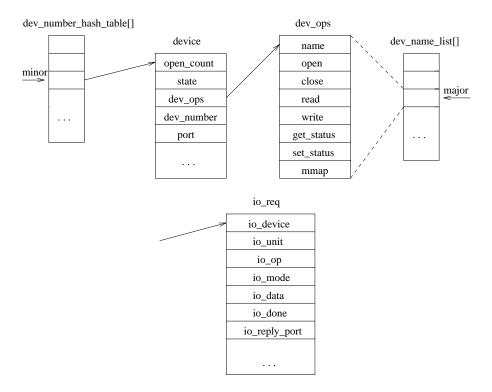

|            | Generic layer data structures                                                                 | 214  |

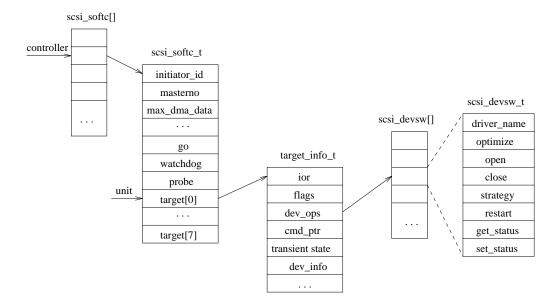

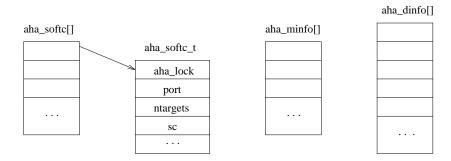

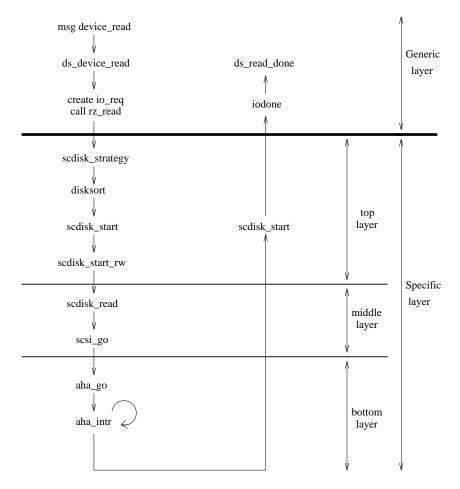

|            | •                                                                                             | 215  |

|            |                                                                                               | 215  |

|            |                                                                                               | 216  |

|            | <u>*</u>                                                                                      |      |

| 7.30       | Console device specific layer data structures                                                 | ∠10  |

| 7.31 | Console device write path                                           | 217 |

|------|---------------------------------------------------------------------|-----|

| 7.32 | Console device read path                                            | 218 |

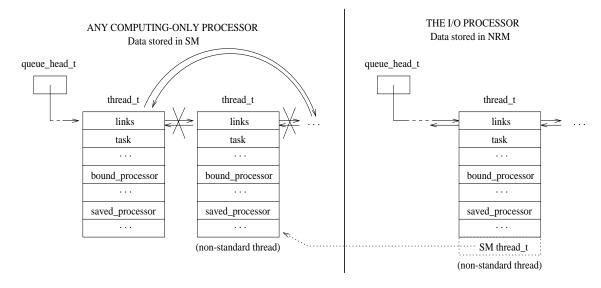

| 7.33 | SM and NRM data structures                                          | 221 |

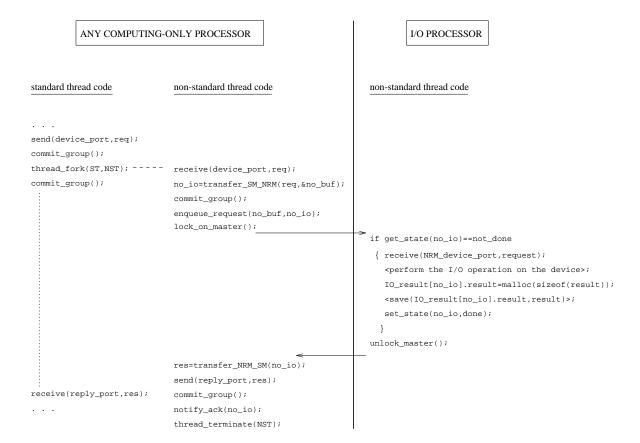

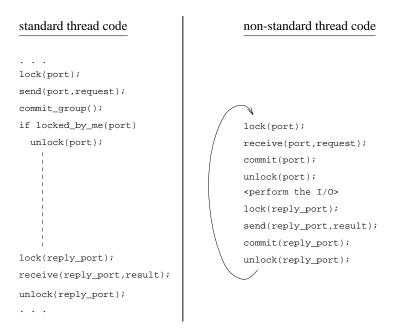

| 7.34 | An I/O operation development for the first implementation proposal  | 225 |

| 7.35 | Scheduling and forward error recovery actions                       | 225 |

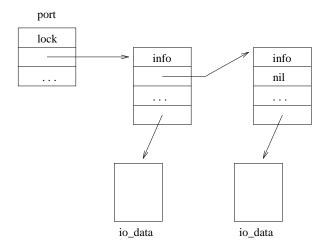

| 7.36 | A device port structure                                             | 227 |

| 7.37 | An I/O operation development for the second implementation proposal | 227 |

## **List of Tables**

| 4.1 | Assessment of chip count necessary to implement a $SM$      | 100 |

|-----|-------------------------------------------------------------|-----|

| 5.1 | Futurebus+ global memory map for the Demonstrator           | 122 |

| 5.2 | Demonstrator non- $DPU$ components                          | 123 |

| 5.3 | ESM Events                                                  | 133 |

| 5.4 | Injected faults                                             | 136 |

| 5.5 | Median of the latency times in nanoseconds                  | 137 |

| 6.1 | Historical Rates of Improvement in Disk Technology          | 140 |

| 6.2 | Switch-mode Checkpointing Truth Table for a Stable Location | 157 |

## Chapter 1

## **Fault Tolerance**

### 1.1 Introduction<sup>1</sup>

Multiprocessor systems based upon standard microprocessors are becoming ever-more commonplace, providing significant computational power at a fraction of the cost traditionally associated with systems of such power. While multiprocessors with distributed memory have gained much attention due to their theoretical peak performance claims, shared-memory multiprocessors continue to be the focus of development of several manufacturers, primarily due to the ease with which such systems can support traditional computing environments and programming paradigms. Nowadays, shared memory systems span the complete range of computing requirements from the personal workstation up to the supercomputer, and with the advent of hardware for distributed shared memory, shared memory has reclaimed a central architectural role.

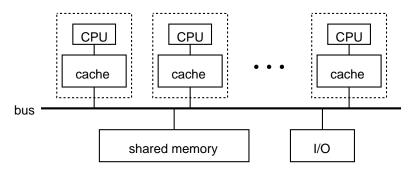

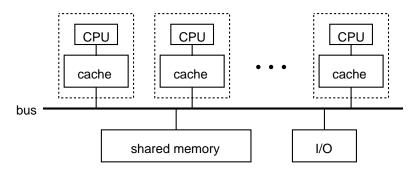

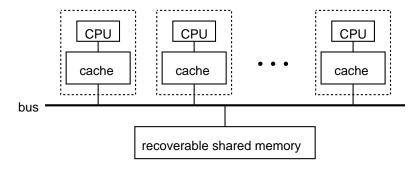

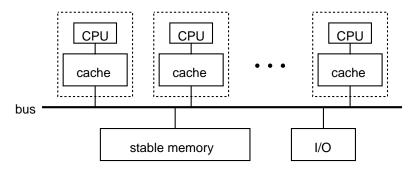

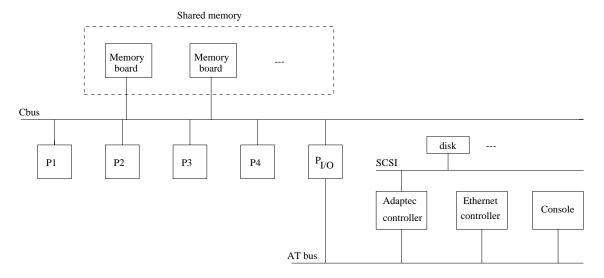

The dominant organisation of a typical shared-memory multiprocessor is as shown in Figure 1.1, with a single shared bus used to connect processing elements to the shared memory and peripherals. Caches private to the processing elements together with various flavours of snoopy cacheing protocols minimise the bottleneck effect of the single bus. A discussion of the advantages and disadvantages of such architectures is not the concern of this book, and we merely observe that shared bus systems are likely to continue to be constructed. What is of concern to this book is how such systems can be constructed such that hardware faults affecting the processors in the system can be tolerated so that a reliable processing service can be provided in spite of those processor failures.

Figure 1.1: A typical shared memory architecture

The need for enhanced reliability is becoming an ever-more critical requirement as computing systems are used for applications where even short breaks in service are unacceptable. Moreover, it is simply infeasible with the complexity and range of present-day software systems to expect that such systems can be enhanced to implement hardware-fault tolerance. What is required is a hardware architecture that can transparently tolerate processor faults, that is, without affecting the executing software and requiring no changes to be made to that software. The presentation of such an architecture for shared memory multiprocessor systems is the primary purpose of this book.

The remainder of this book is organised as follows. First we examine the fundamental problems of providing fault tolerance in a shared-memory multiprocessor, identifying the basic facilities that must be implemented and exemplifying these facilities with examples from some of the fault tolerant multiprocessor systems which are already available commercially, and discussing further the problems of error recovery in multiprocessor systems. Results from simulations of various architectures are also discussed.

We then introduce a fault tolerant architecture which directly supports shared memory semantics. The concept of stable memory, which implements some of the features necessary for transparent fault tolerance, and which is the key novel feature in the architecture, is described in detail, along with associated architectural components.

For simplicity and brevity, the book concentrates on the problems of tolerating processor failures in a shared memory environment and the novel solutions to these problems. Other hardware fault scenarios, such as bus failures, are not covered here, although are clearly important for a complete system.

#### 1.2 Fault Tolerance Issues

The basic principles behind fault tolerance are well understood [Lee et al 90]: a fault in a system will give rise to errors; the starting point for fault tolerance is the detection of an error, and an exception can be raised to signal that

<sup>&</sup>lt;sup>1</sup>This chapter contributed by Pete Lee, Department of Computing Science, University of Newcastle, Newcastle upon Tyne, NE1 7RU, U.K.

the fault tolerance provisions in the system need to be invoked. These provisions have to:

- (a) deal with those errors, in particular to remove errors such that the state is no longer erroneous (error recovery); and

- (b) deal with the fault that caused the errors, by identifying its location (fault location), reconfiguring the system to avoid the fault components (fault treatment), and switching the system back to providing its normal operation.

If the above actions are successful, such that the behaviour of the system has not breached the specification of the system, then the system will have successfully tolerated the fault and its effects, and no system failure will be apparent. Preventing system failure is of course the aim of the fault tolerance provisions.

As mentioned previously, this book is concerned with tolerating the faults caused by failures of the microprocessor processors providing the processing power in a multiprocessor with the structure as shown in Figure 1.1, and will therefore concentrate on the application of the above basic principles in this situation. Thus, regarding each processing element as a component of the multiprocessor, we are concerned with providing reliable behaviour in the face of failures affecting these components.

To provide fault tolerance, the first requirement is that the effects of a processor failure are detected. One approach, adopted in the Tandem-16 system [Katzman 78], is to use a single CPU per processing element and to assume that a failure will result in fail-stop behaviour, in that the processing element simply stops if something goes wrong in its logic. The other processors will detect this cessation in service through the absence of the *I'm alive* messages which an active processor regularly broadcasts to all other processors. Note, however, that the Tandem system is not a shared memory multiprocessor, and such single-CPU configurations for a processing element are not the focus of this book.

More active forms of error detection are provided by replication checks where the activity of a CPU is replicated and the outputs from the replicas compared to detect an error. When duplicated CPUs are used, a comparator can detect differences caused if one of the CPUs fails and can raise an exception (or interrupt) to inform the rest of the system of the failure of this processing element such that the fault tolerance actions can be undertaken. This organisation is used in the processing elements of both the Stratus [Wilson 85] and Sequoia [Bernstein 88] fault tolerant systems.

Higher levels of replication, such as using triplicated CPUs in a TMR organisation, can also be used, for instance as in the Tandem S2 system [Jewett 91]. Here a different approach to fault tolerance is being taken as will be seen. In the case of the duplicated CPU discussed previously, a failure of a CPU results in the failure of the processing element of which it is a part: this processing element failure is a fault in the multiprocessor system, and actions elsewhere in the multiprocessor (as will be discussed shortly) have to provide the fault tolerance such that overall system behaviour is not impacted. In contrast, the application of TMR (and higher levels of replication) is simply the application of fault tolerance internal to the processing element such that failures of components within the processing element are never seen by the rest of the system, and for this reason such applications of redundancy are sometimes referred to as masking redundancy. Thus when a CPU fails in a TMR configuration, the divergence of its results from the other two CPUs can be detected by a voter which rejects the *odd man out* (error recovery), ignores the suspect CPU (fault treatment) and passes on the result of the majority to the rest of the system without interruption.

Returning to the situation of the dual-CPU processing element, errors in the system state (i.e. in the global memory) will have to be dealt with if a processing element fails. Errors could have spread in the system by there being a delay between the CPU failure occurring and the processing element actually stopping, during which time erroneous results could have been generated in the shared memory and hence propagated through the system. In the dual-CPU case, there is unlikely to be such a delay and consequent propagation. However, there may still be errors since some of the state of the system will be contained within the failed processing element and this information may be inaccessible. For instance, the contents of the CPU registers and indeed the program counter are all part of the overall system state, and the caches on the processing element may also contain the up-to-date values of some memory locations. Thus, the global memory state may not be consistent with the processing that has been undertaken in the failed processing element, and some form of error recovery will be needed to cope with these errors. Without such error recovery, successful fault tolerance may not be achievable.

Two overall forms of error recovery could be applied: forward error recovery and backward error recovery [Lee et al 90]. Forward error recovery would require the "patching" up of the system state to fix the problems - for instance, if the failed processing element could be interrogated by another processing element to extract

the necessary values, then the system state could be updated appropriately. However, it is unlikely that such an interrogation could take place reliably if a CPU failure has occurred - some of the information may be within the failed chip (e.g. in on-chip caches). Even with duplicated CPUs, it may be difficult to determine which of the pair has failed with the aim of extracting the information from the remaining "good" CPU. The alternative recovery strategy of backward error recovery requires the state of the whole system to be recovered to a prior known state (simulating the reversal of time, and hence called backward error recovery) such that all of the errors are eradicated. This approach is discussed in detail within this book.

The Stratus system effectively uses a forward error recovery scheme, but avoids the need to interrogate the failed processing element by running a computation simultaneously on two processing elements, each of which contains two CPUs (i.e. on 4 CPUs in total). If one processing element fails, then the other processing element can be used to provide all of the "internal" values, such that a new processing element can be brought into lock-step and the processing continued (alternatively, the computation can be continued on the single processing element pair with the hope that another failure does not affect that processing element, in which case no error recovery is required). In contrast, the Sequoia system effectively employs backward error recovery, and their scheme is described in the next section.

After error recovery has been carried out, the errors caused by the processing element fault have been dealt with, and so the next stage of fault tolerance is to deal with the fault itself. The location of the fault will be identified by the exception raised in the dual-CPU configuration. If the fault was deemed to be transient (determined, for example, by running diagnostic checks on the faulty processing element), it may be appropriate to permit that processing element to continue to play a part in the system's activity. If, however, the fault is permanent, then that processing element will not be used further, and the computation it was involved in can be restarted on another of the processing elements in the system. If forward error recovery has been used, for instance as in the Stratus system, no processing will have been lost, whereas if backward recovery has been invoked, as in the Sequioa system, some processing will have to be repeated. Note, however, that in a shared memory environment it is a relatively straightforward task to ensure that a computation can be picked up by another processing element - all of the information concerning that computation can be in shared memory and is accessible to all of the processing elements. In a distributed memory situation, as in the Tandem-16 system, this task can be much more complex.

Thus the designer of a fault tolerant multiprocessor is faced with typical engineering trade-offs. Indeed, the different designs taken by Sequoia, Stratus and the Tandem S2 systems suggest that a number of engineering trade-offs are feasible, and that each approach has its place. By adopting triplicated (or higher) levels of redundancy in the processing elements, the need for error recovery can be avoided. However, the cost and difficulties associated with this approach suggest that a design based on duplicated CPUs with provisions for backward error recovery might be more cost-effective. In this book we concentrate on this dual-CPU, backward error recovery approach and on the design of a special form of memory which supports backward error recovery in a shared memory environment. First, though, the basic problems of, and terminology for, backward error recovery in this environment must be discussed so that the facilities that must be provided can be identified.

## 1.3 Backward Error Recovery in a Shared Memory Environment

The basic functions required for backward error recovery are that a processor can:

- (a) establish a recovery point;

- (b) recover the state back to that recovery point (roll back); and

- (c) commit a recovery point.

The time between the establishment of a recovery point and its eventual commitment is termed a recovery region. A recovery point is thus a point in a computation to which the state can be reset and hence the computation can be restarted from that point. If the establishment of the recovery point preceded the occurrence of a processor failure, then recovery to that recovery point must eradicate all of the potentially erroneous effects of that fault (as discussed in the previous section).

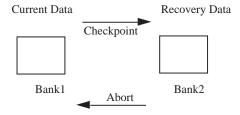

To provide recovery, recovery data must be recorded, for which one of several techniques can be adopted. For example, a checkpoint can be taken when the recovery point is established, that is, a complete copy of the state taken and kept somewhere safe. Since the complete state is likely to be large, and a processor is unlikely to

update a significant percentage of its state, more dynamic and optimal facilities can be provided. Shadow paging [Reuter 80] provides a form of incremental checkpointing, by keeping a copy of only those memory pages that have been altered. The recovery cache [Lee et al 80] also provided incremental recording of recovery data.

The Sequoia system makes use of a blocking cache [Bernstein 88] to provide recovery: having established a recovery point, a processor is not permitted to update main memory. Instead all writes are kept local to the processor in a blocking (i.e. non-write-through) cache. If the processor fails, then the state in the main memory represents the state at the recovery point. The commitment of a recovery point by a processor consists of flushing its cache and its internal registers to main memory. Modified data are flushed into two distinct memory modules under processor control in order to handle memory and processor failures.

The CARER architecture [Wu et al 90] makes also use of a blocking cache with the assumption of fault free memory and cache. Assuming that memory is fault free avoids the need for a second memory module for recovery data and hence avoids the loss of time that would be necessary for copying modified data between the two modules. Assuming that caches are fault free limits the work to be done at commit time because blocks residing in cache can be included as recovery data. At commit time, all processor registers are first flushed to the cache and then all modified blocks in the cache are marked *unwritable*. This terminates the commit operation. *Unwritable* blocks belong to the recovery point and have to be written back to memory if they are subsequently modified or replaced (i.e. copy on write).

While the changes a processor makes to memory can be undone by state restoration techniques such as those described above, not all of the manipulatable entities in a system can be recovered. For instance, as discussed in the previous section, the processing element itself may be unrecoverable in that its contents (registers etc.) may not be accessible if that element has failed, so these have to be explicitly recorded when a recovery point is established (e.g. the program counter must be recorded to allow the computation to be restarted from that point). Also, a processor may manipulate other unrecoverable objects, such as peripherals, and the fault tolerant system must cope with the problem of backward recovery in this situation also.

Since recovery data occupies some system resources, it is normal to commit recovery points at some interval, to allow this recovery data to be discarded. For example, in CARER a recovery point is committed each time modified data in the cache has to be replaced, while in the Sequoia system a recovery point has to be committed when the blocking cache of a processor becomes full. For the tolerance of processor faults it is, in general, sufficient to allow a processor to have a single extant recovery point such that the commitment of a recovery point can be synonymous with the establishment of the next recovery point, and thus two distinct operations (establish and commit) are not needed. In a more general situation, for instance if providing software-fault tolerance by recovery blocks [Horning et al 74], nested recovery regions and hence multiple extant recovery points and separate establish and discard operations make sense. As will be seen, even in the simple case it is useful to be able to separate the completion of a recovery region from the commencement of the next.

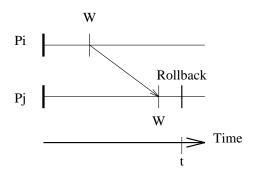

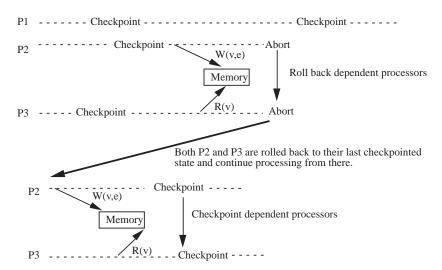

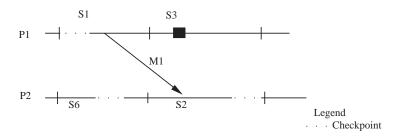

In a shared memory multiprocessor, there is another complication to recovery that must be dealt with, concerning the parallel processors that will be executing simultaneously and the possible flow of information between these processors via shared memory. Consider the following simple situation: two processors P1 and P2 have separately established recovery points, and P1 has written to a memory location that P2 has subsequently read from and acted upon. Now if P1 fails and backward recovery has to be applied, then it is also necessary to recover P2 to its recovery point which preceded the interaction with P1. Only by recovering P1 and P2 is a consistent system state restored. The recovery points of P1 and P2 which correspond to a consistent state are termed a recovery line [Lee et al 90].

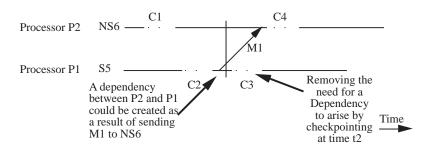

One strategy for identifying a recovery line is to ensure that all processors establish recovery points simultaneously - that is, a system-wide recovery point. If recovery is then required because a processor fails, all processors have to be rolled back. This strategy has the disadvantage of unnecessarily recovering processors when no interactions between a processor and the failing processor have occurred. To avoid this disadvantage effectively requires processors to be recovered independently (rather than globally), and hence requires some other means for solving the problem of interdependencies (i.e. the problem of identifying a recovery line). One method is to avoid the need to identify a recovery line by ensuring that there are no inter-processor dependencies. This can be achieved by not actually providing shared memory (a strategy adopted in the Sequoia architecture) or by committing after each interprocessor interaction in order to remove the dependency (this is essentially what happens in CARER where a processor has to commit its recovery point each time one of its modified blocks in cache is accessed by another processor).

The Sequoia architecture prohibits direct data sharing between processors, leading to significant complications being imposed on the operating system software. While all memory modules can be accessed by all processors, shared data structures must be accessed within explicit critical sections protected by test-and-set locks, and the operating system has to carefully establish and commit recovery points and flush the blocking cache appropriately, to ensure the correct semantics [Bernstein 88].

An alternative solution to identifying recovery lines, which removes the need for the software complexities of the Sequoia approach and the frequent commitments of the CARER approach, is to actually compute a recovery line if recovery is required [Lee et al 90]. In order to do this it is necessary to record inter-processor dependencies which can be used to determine the set of processors which are dependent upon the processor which has failed [Banâtre et al 90a].

It should also be noted that in the Sequoia system it has been necessary to provide custom caches to provide the blocking behaviour. This precludes the use of standard snoopy caches and protocols in such a system. However, the speed of the latest generation of RISC chips is such that their manufacturers provide cache control logic (and chips) as part of their offerings, and it is increasingly difficult (and cost-ineffective) to design custom cacheing systems (and CPUs). Hence, it is desirable that standard processors, caches and cacheing protocols can be used in a shared memory multiprocessor, while still allowing fault tolerance using backward error recovery to be provided.

One may conclude that the concept of *backward error recovery* is now well established as a means of restoring a consistent state to a fault tolerant system should some faults occur [Randell 75]. Several algorithms have been proposed in the literature for providing backward error recovery depending upon the type of faults to be tolerated, the system characteristics, and the fault tolerance strategy.

In a system of communicating processes, should a fault occur, the *recovery control protocol* must determine a set of process states which together constitute a consistent state of the system. Many recovery protocols that assume message passing communication have been proposed in the literature (see for instance [Wood 85, Strom et al 85]). In contrast, the recovery protocol discussed below relies on the fact that communication takes place through shared data, and that the memory itself tracks directly the dependencies between the processors' references to the shared data.

### 1.4 A Basic Recovery Protocol for a Shared Memory Environment<sup>2</sup>

Before we present a basic recovery protocol for processes communicating through shared data, we must first introduce some definitions and background notions concerning backward error recovery in a system of communicating processes.

#### 1.4.1 Definitions

A recovery point is established by a process at a point in time at which the state of the process is saved for possible regeneration in the event of recovery action. A process commits a recovery point when it no longer requires the capability to initiate recovery action to that point. The period of process activity between the establishment of a recovery point and the commitment to it is called the process transaction associated with that point (notice that the meaning of the word transaction here should be distinguished from the one which is usually given in transactional systems [Gray 78] where a transaction may refer to a consistency unit preserving some invariant of the system). The most recently established recovery point of a process is said to be active or equivalently current. A recovery point which cannot possibly be recovered to as a result of a recovery action initiated anywhere in the system is said to be discardable. Some of the above definitions are borrowed from [Lee et al 90].

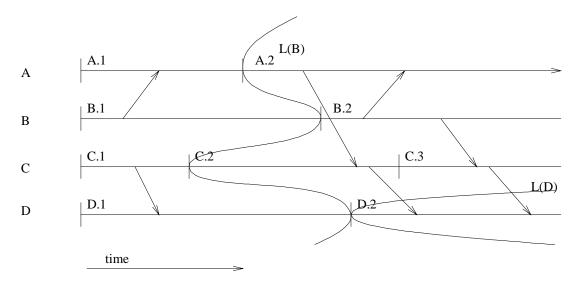

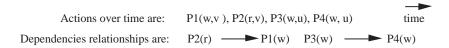

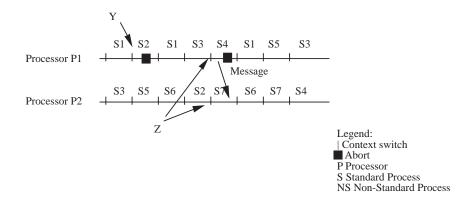

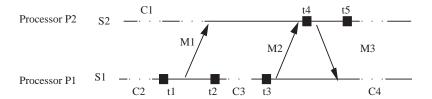

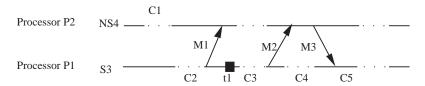

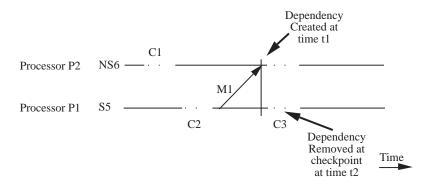

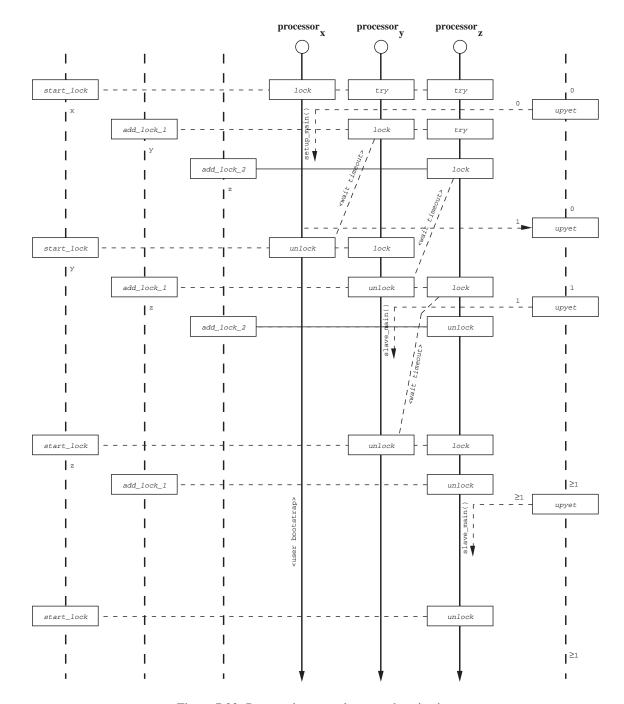

We assume a model of computation of communicating processes where processes implement a succession of *non-nested* transactions, establishing a recovery point immediately on commitment to the preceding one. This is depicted in Figure 1.2 where vertical bars denote the bounds of process transactions. The recovery control management offers the primitive NewProcessTransaction(p) for committing the active recovery point and establishing a new recovery point for process p (as a simplification, initialization is not considered). Information flows between processes are assumed to be directed (unidirectional), and are represented by arrows in Figure 1.2 when occurring between distinct processes. It is further assumed that all information sent out by a process is dependent on all information previously received by that process.

<sup>&</sup>lt;sup>2</sup>This section contributed by Michel Banâtre, Maurice Jégado, Philippe Joubert and Christine Morin, Campus universitaire de Beaulieu, 35042 Rennes Cedex, France

**Definition 1** For any two recovery points rp and rp' belonging to processes p and p' respectively, rp is a *direct* propagator to rp' if and only if information flows from p to p' while rp and rp' are the respective active recovery points of the two processes.

As a particular case, a recovery point of a process is a direct propagator to the next recovery point of the same process (for example, in Figure 1.2, recovery point B.2 is a direct propagator to A.2 and C.3 while A.1 is a direct propagator to A.2). For convenience we will sometimes refer to the propagator relation between process transactions instead of recovery points. A process transaction  $t_1$  is a direct propagator to  $t_2$  if the recovery point established at the beginning of  $t_1$  is a direct propagator to the initial recovery point of  $t_2$ .

**Definition 2** For any two recovery points rp and rp' belonging to processes p and p' respectively, rp is a *propagator* to rp' if and only if the following holds: Either rp is a direct propagator to rp' or else, recursively, there exists a recovery point rp'' belonging to process p'' such that rp is a direct propagator to rp'' and rp'' is a propagator to rp'

For example, in Figure 1.2, recovery point B.2 is a propagator to A.2, C.2, C.3 and D.2. As an obvious consequence of the notion of a *propagator*, we will often refer to the recovery *ancestors* and recovery *descendants* of a recovery point rp:

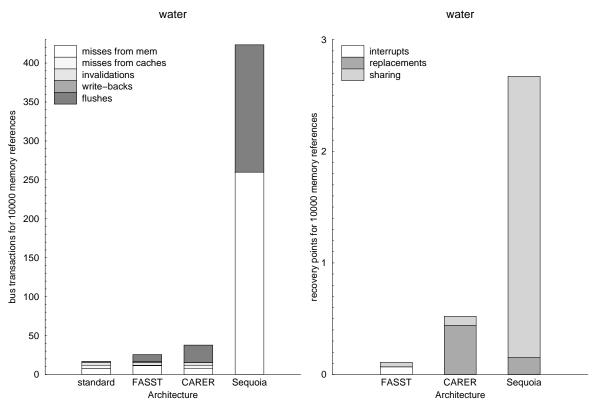

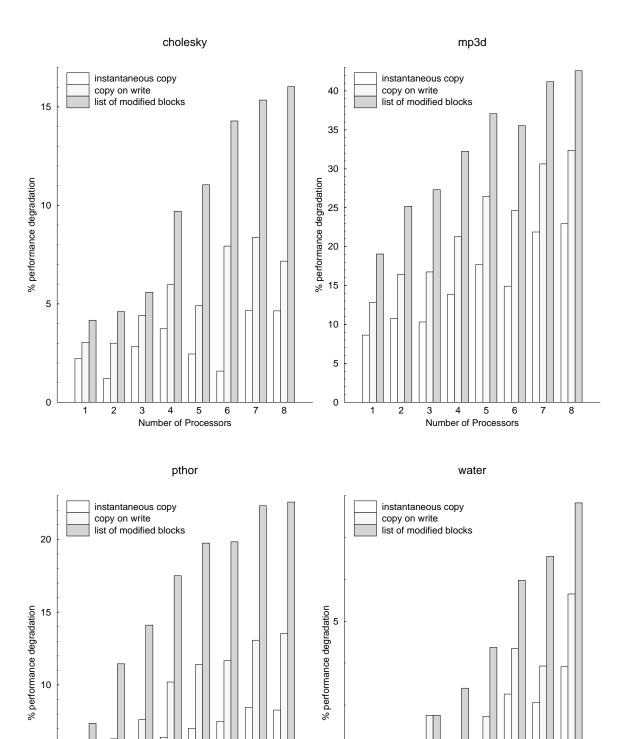

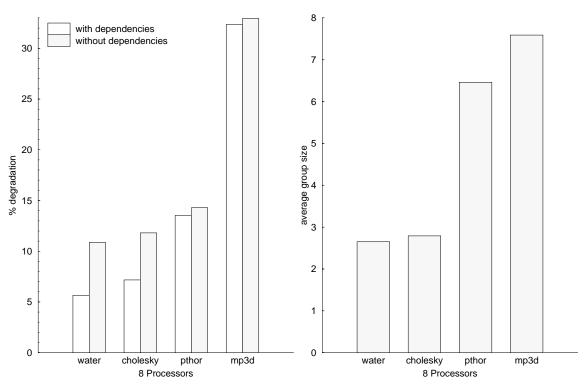

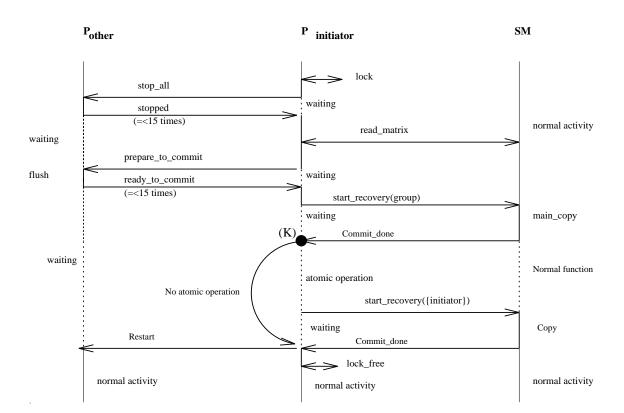

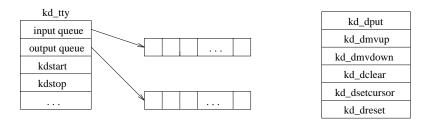

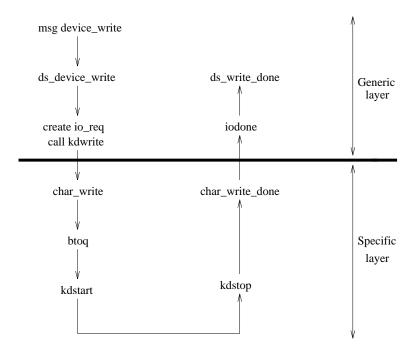

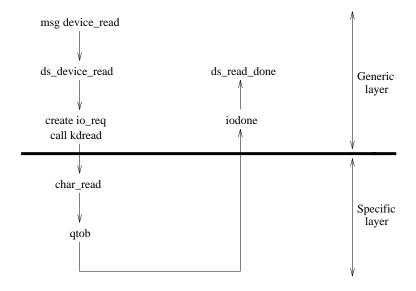

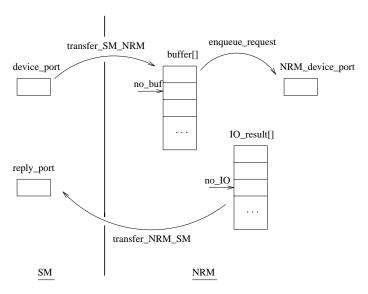

**Definition 3** An ancestor recovery point of rp is a propagator to rp. Conversely, if a recovery point rp' is descendant of rp, rp is a propagator to rp'.