**SCI Europe number:** P25257 **Deliverable number:** D2.2.1a

**Contractual date:** 30<sup>th</sup> September, 1998

Work package: 2.2.1

Document version: 2.0

Document status: Complete

Confidentiality: Consortium

Document date: October, 1998

## Deliverable

# Prototype Tracer

**Partner:** Trinity College Dublin

Author(s): B.A.Coghlan, M.Manzke, E.Barnstedt, R.Cunniffe, J.Dukes

Editor: B.A.Coghlan

**Keywords:** SCI, tracer, analyzer

#### **Abstract:**

In this document we present the technical manual for the prototype tracer developed within the project.

## **ESPRIT Project P25257 SCIEurope**

Deliverable D 2.2.1a

# **Prototype Tracer**

#### October 1998

Dr.B.A.Coghlan Department of Computer Science Trinity College Dublin coghlan@cs.tcd.ie

M.Manzke Department of Computer Science Trinity College Dublin michael.manzke@cs.tcd.ie

E.Barnstedt R.Cunniffe J.Dukes Department of Computer Science Trinity College Dublin

#### Introduction

The definition of Task 2.2.1 is as follows:

| Task           | 2.2.1                                                                     | Test T           | ools Develo | pment                     |  |

|----------------|---------------------------------------------------------------------------|------------------|-------------|---------------------------|--|

| Market and     | There are no commercially available SCI test tools on the market for the  |                  |             |                           |  |

| User Need      | SCI community today.                                                      |                  |             |                           |  |

| Objectives     | To develop the first generation of tracing and debugging tools for use in |                  |             |                           |  |

|                | work package 3 Applications.                                              |                  |             |                           |  |

| Approach       | The tools will be based on needs identified in the Test Requirements      |                  |             |                           |  |

|                | Specification from Task 2.1. There will probably be developed two tools   |                  |             |                           |  |

|                | - one tool able to trace the SCI traffic and either show online or store  |                  |             |                           |  |

|                | the results. This tool will be based as much as possible on present       |                  |             |                           |  |

|                | hardware and software platforms. The other tool will be able to send and  |                  |             |                           |  |

|                | receive SCI traffic according to some traffic profile in order to load    |                  |             |                           |  |

|                | systems with traffic without using real nodes. The prototype tools will   |                  |             |                           |  |

|                | be evaluated during the debugging phase of the Embedded Avionics          |                  |             |                           |  |

|                | System demonstrator in Task 3.3, and the results will be summarised in    |                  |             |                           |  |

|                | a report.                                                                 |                  |             |                           |  |

| Lead Partner   | Trinity                                                                   | 24 person months |             |                           |  |

| Other Partners | D.E.                                                                      | 4 person months  |             |                           |  |

|                | SINTEF                                                                    | 12 person months |             |                           |  |

| Major          | D 2.2.1                                                                   | Q4               | Trinity     | Prototype Tracer/Analyzer |  |

| deliverables   | D 2.2.2                                                                   | Q6               | SINTEF      | Traffic Generation Tool   |  |

|                | D 2.2.3                                                                   | Q8               | Trinity     | Tracer/Analyzer Mk.II     |  |

The objective of this document is to present the Technical Manual for the Prototype Tracer. This represents the hardware and software resources of the Prototype Tracer/Analyzer. The software for the Prototype Analyzer will be presented in a later document.

The Prototype Tracer is not specifically oriented towards SCI, but instead provides general purpose deep trace facilities. B-Link traces will be acquired via a probe card supplied by Dolphin, that attaches to their SCI cards via elastomeric connectors, and breaks out the B-Link signals to a number of connectors that will accept cables for a HP16500 series logic analyser. Trinity will design a probe adapter that will attach to these to distribute the B-Link signals to a multiple of the DT200.1 Deep Trace boards. Pending the probe adapter, the B-Link signals will be connected directly from the probe card to two DT200.1 boards; this will allow some experimentation into detailed trigger/trace needs using the trigger/trace facilities of the DT200.1 boards.

Computer Architecture Group Department of Computer Science Trinity College Dublin Ireland

**Deep Trace DT200.1**

**Technical Manual**

B.A.Coghlan P.O'Carroll M.Manzke E.Barnstedt R.Cunniffe J.Dukes

Tel: +353-1-6081765

Fax: +353-1-6772204

## **Deep Trace DT200.1**

## **Technical Manual**

#### Introduction

Systems performance analysis involves the collection and analysis of traces obtained from a target computer system. By presenting views that illustrate the target's behaviour versus time, a designer can determine how efficiently the target system is operating. These views are traditionally in the form of histograms, charts or tables of statistics. Trace analysis can reveal many interesting system characteristics such as where a processor is spending most of its time, how long critical routines take to execute, how often a cache contains the desired information, how well a cache coherency protocol performs, whether there is excessive contention for locks, how well the load is balanced among processors, and so on. If performance bottlenecks can be located, corrective action can hopefully be taken.

Traditional logic analysers collect traces in real-time, but their capacity is generally limited to the order of 1to 8K samples. With time this is improving, for example, a new trace module has been introduced for the Hewlett Packard HP16500A logic analyser - a fully configured system comprising five HP16542A boards is capable of collecting 1,000,000 x 80bit samples @100MHz. Users cannot write analysis software for the HP16500A itself, but the contents of the trace memory can be transferred to a PC, albeit via a relatively slow RS232 or HP-IB interface for analysis.

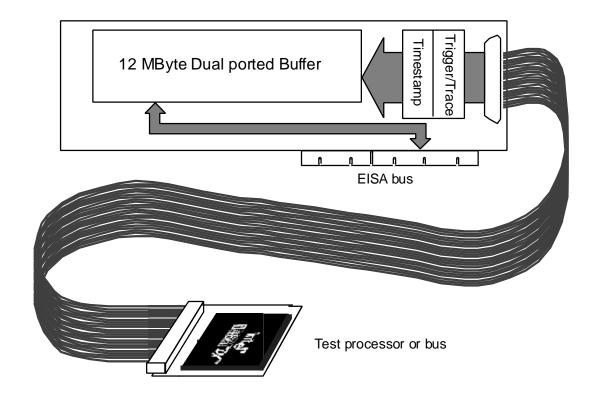

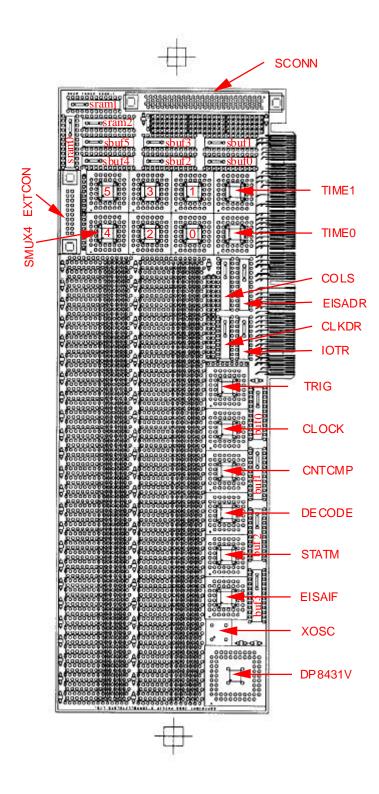

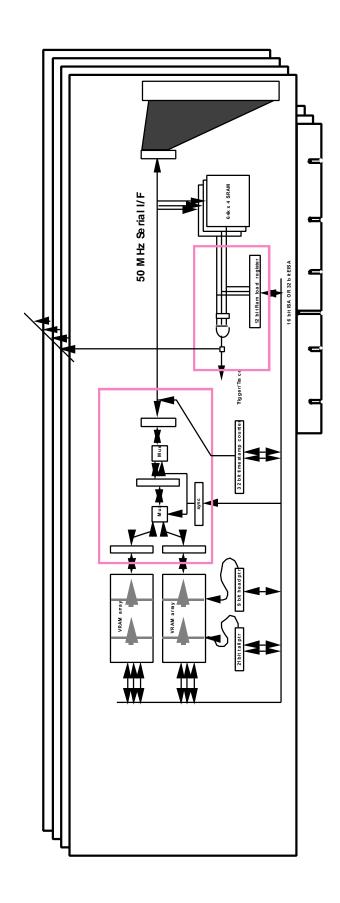

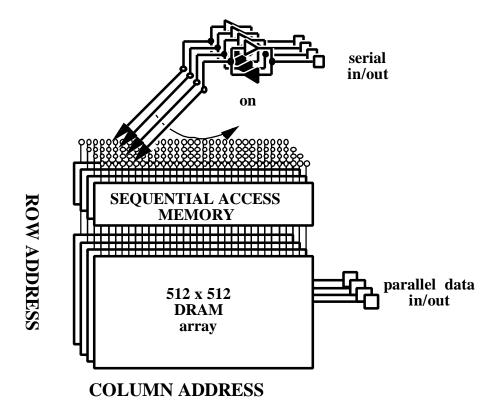

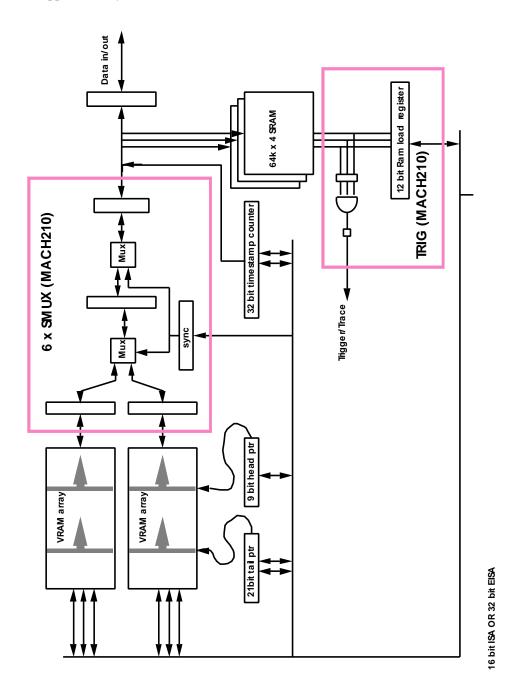

The DT200.1 Deep Tracer is a modular data collection system designed sp ecifically for gathering very long state traces for performance analysis of processor and I/O busses. In a minimal configuration the data collection system consists of two modules, a sampler board which stores the trace and a preprocessor module to collect data from the target bus. This allows traces to be generated from a variety of busses by using different preprocessor modules. This document describes the technical details of the EISA based sampler board DT200.1.

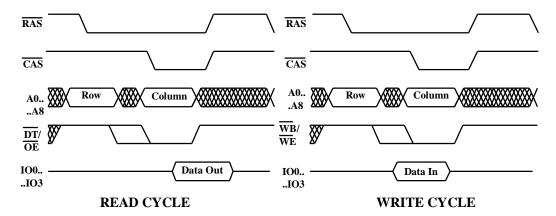

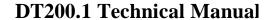

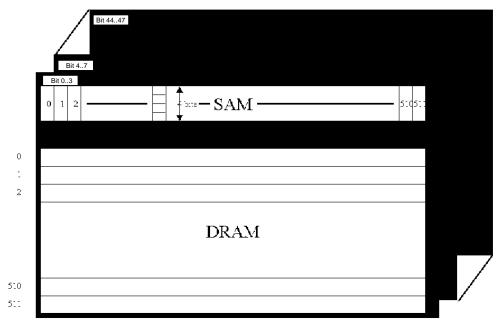

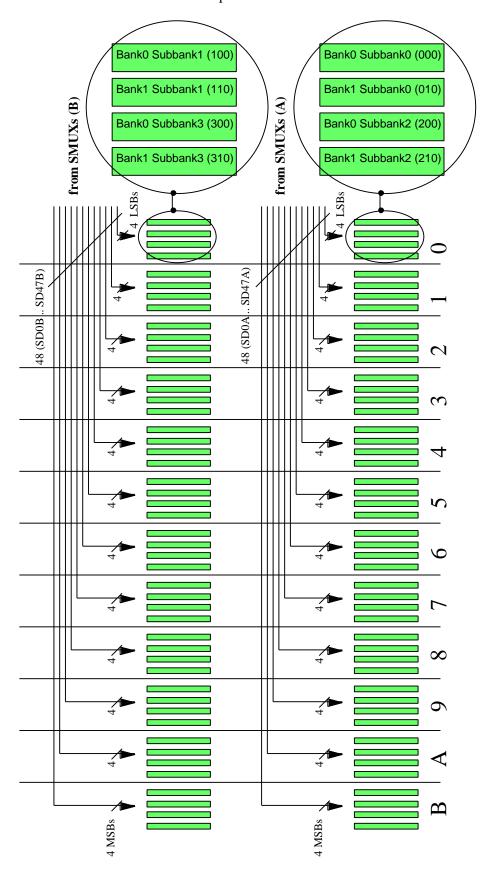

Conceptually the system functions as a very deep FIFO. Data is sampled via the 48 bit serial interface on the positive edge of a clock and stored in a 12MByte VRAM buffer. The buffer wraps around and can be read out via the EISA interface without stopping the sample clock. A block diagram of the trace system is shown below.

#### **Features**

- 2 Million x 48bit samples 12MBytes Dual Ported VRAM

- Max Sample Rate 50MHz on Serial Port Max data rate 300Mbytes/second.

- Standard EISA interface on Parallel Port

33MByte/sec bursting slave allows data to be read out transparently and asynchronously without stopping trace. Autoinitialization on power up. Buffer can be mapped anywhere in EISA address space.

• Real Time Trigger and Trace functions

64k x 12 Trace SRAM gives a minimum of four arbitrary trace ranges

• Expandable in Width and Depth

An interboard connector allows multiple boards to cascaded to increase the sample width, in multiples of 48bits, up to 192bits wide. It is also possible to interleave boards to increase buffer depth in multiples of two million. This also increases the maximum sample rate.

Integral Timestamping

48bit 50MHz timestamp counter plus serial clock synchronizing logic. Interboard connector allows distributed synchronisation of multiple boards.

Bidirectional

Can be programmed to output samples synchronously with an external clock.

Page 7 28th October, 1998

## **Programming Model**

This section contains all the information necessary to write low level code to drive the sampler board. Sample code and header files are presented later in this document. It is recommended that driver software uses the code provided or other trusted routines to ensure the integrity of the collected traces.

## **Register Summary**

The hexadecimal addresses of all the programmable registers are shown below. They are all mapped into Slot Specific EISA I/O space. The actual I/O address is calculated by substituting the Slot number (0..15) for the upper four bits. Slot number is represented by 'Z'.

| offset | mnemonic   | r/w | operation                       |

|--------|------------|-----|---------------------------------|

| 0xZ000 | RESET      | W   | Hard Reset of entire Board      |

| 0xZ004 | ADDRMAP    | r/w | Write EISA Address Map          |

| 0xZ008 | MODE       | r/w | Mode Control Register           |

| 0xZ00C | TRIGCONFIG | r/w | Trigger/Trace Select Reg        |

| 0xZ010 | TIMERESET  | W   | TimeStamp Counter Reset         |

| 0xZ014 | STOPCOUNT  | r/w | Trigger Row Counter             |

| 0xZ018 | HEADPTR    | r/w | Head Pointer Counter            |

| 0xZ01C | OUTPUTENA  | r/w | Output Enables                  |

| 0xZ020 | STATUS     | r   | Trace Status                    |

| 0xZ080 | EISAID     | r   | EISA ID for Slot initialisation |

#### 0xZ000 RESET: Board Reset

Writing any value to this register resets all registers, timestamp counter, EISA interface and internal state machines. After a system reset or power- UP, the VRAM buffer will not respond until .

- 1. the board is RESET by a write to 0xZ000, and then

- 2. a write is made to any register but the RESET register.

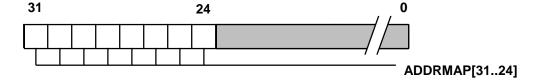

#### **0xZ004** ADDRMAP : EISA Address Map Register

This register specifies the upper 8 bits of the VRAM buffer address map in EISA memory space. It must be written before the buffer can be accessed. After a system reset or power- UP, the VRAM buffer will not respond until first the board is first RESET and then a write is made to any register but the RESET register.

Page 8 28th October, 1998

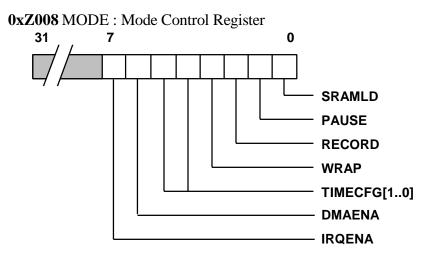

There are 8 mode bits in this register - all are active when non zero. Currently the two most significant bits are not implemented.

SRAMLD enables the trace SRAM to be read and written. It disables sampling but does not stop the timestamp counter.

PAUSE stops the sampler. It is buffered on an open collector line which can be connected to other boards over the inter-board connector. This allows multiple boards to start and stop sampling together.

RECORD specifies the direction of the serial port. RECORD=1 means the board samples the serial bus synchronously with the serial clock. RECORD=0 causes the serial buffers to drive the contents of the sample memory onto the serial bus synchronously to the serial clock. Writing to this bit turns around the VRAM serial ports and resets the output buffer enables - hence it should be set to its intended value before the output buffer enables are configured, i.e. immediately after writing RECORD=1, the timestamp counter outputs will be disabled (but the counter itself is unaffected). Note that since RECORD=1 either enables either the sample input buffers or the timestamp counter outputs (depending upon OUTPUTENA[5..0]), the SRAM cannot be accessed while RECORD=1.

TIMECFG[1..0] specifies the divisor for the timestamp counter: 1, 2, 4 or 8.

WRAP causes the board to ingnore the STOPCOUNT counter and continue sampling when it reaches zero.

DMAENA enables the board to request the host machine to perform DMA on EISA DMA channel 7 when the STOPCOUNT counter reaches zero. Currently, DMAENA is not implemented.

IRQENA causes the board to assert EISA interrupt IRQ12. The interrupt is level triggered so that multiple boards can share the same interrupt. Currently, IRQENA is not implemented.

Page 9 28th October, 1998

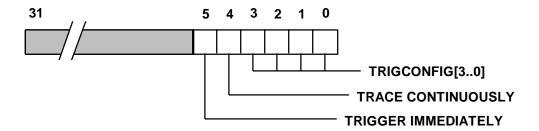

**0xZ00C** TRIGCONFIG: Trigger/Trace Channel Configuration

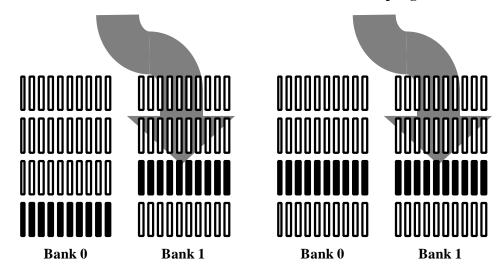

The four least sigificant bits select the four SRAM trigger/trace channels. A logic 0 in TRIGCONFIG[3..0] selects the channel as a trace and logic 1 selects it as a trigger channel. The TRACE CONTINOUSLY bit forces acceptance of every sample. The TRIGGER IMMEDIATELY bit forces the STOPCOUNT to begin counting down immediately.

#### 0xZ010 TIMERESET: Reset TimeStamp Counter

Writing any value to this location resets the timestamp counter. The signal is driven by an open collector buffer onto the inter-board connector so that multiple boards can be synchronised.

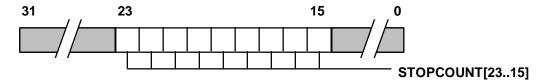

#### **0xZ014** STOPCOUNT : Sample Stop Counter

This register holds the absolute number of samples to be stored before the the sampling stops. The buffer stores samples incrementally in blocks of 2048x48 wrapping around to the base address when it reaches the top of the the buffer. As soon as the SRAM detects a trigger value the stop counter is enabled. The counter decrements with every second block of 2048 samples stored. Loading 0x00000000 into this register causes the board to stop immediately after the trigger so that the trigger value is at the end of the trace. Writing 0x00FF8000 into STOPCOUNT means the the trigger value will occur at the start of the trace. Bits [31..24] and [14..0] will always read as a logic 1. If it is possible to atomically update this register, then very long traces may be generated provided the data can be read out of the EISA interface as fast as it is acquired. Writing to this register will reset the timestamp counter.

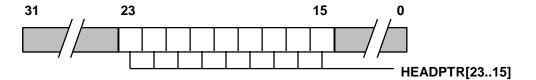

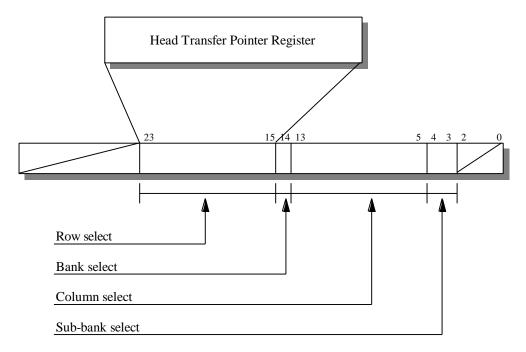

#### 0xZ018 HEADPTR: Head Transfer Pointer

This location holds the 24 bit address offset where the next block of 2048 samples will be stored. Bits [31..24] and [14..0] will always read as a logic 1. Writing to this register will reset the timestamp counter.

Page 10 28th October, 1998

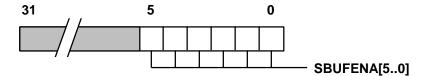

0xZ01C OUPUTENA: Serial Buffer Output Enables

Each of the active bits in this register represents a different byte in the serial port. A logic 1 in OUTPUTENA[5..0] enables the corresponding byte[5..0] of the sample. Disabling an individual sample buffer enables the corresponding byte of the timestamp register, if the RECORD mode bit is set. As a precaution against damaging the buffers this register is reset every time the direction of the sample buffers is changed by toggling the RECORD bit., i.e. toggling RECORD turns around the VRAM serial ports and resets the output buffer enables - hence RECORD should be set to its intended value before the output buffer enables are configured.

#### 0xZ020 STATUS: Trace Status Register

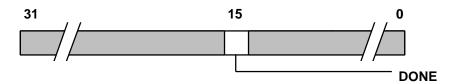

This read only register indicates whether the STOPCOUNT has reached zero. The DONE bit will be a logic zero when the STOPCOUNT counter is non-zero, and a logic 1 when the STOPCOUNT counter reaches zero. Bits [31..16] and [14..0] should always be treated as undefined values.

#### 0xZ080 EISAID : Slot Specific EISA ID Register

This read only register contains the unique EISA ID for the board. This allows the board to be initialised on power up by the system board from initialisation values stored in the BIOS CMOS RAM. It also allows the driver software to scan the EISA slot specific I/O addresses to identify which slots contain trace boards, and therefore at what addresses. Currently this register reads out a value of 0x01209212. A sample EISA configuration file is presented later in this document.

## **TimeStamping**

There is a 48 bit synchronous timestamp counter which can be enabled byte by byte onto the sample data stream. OUTPUTENA[5..0] enables byte[5..0] of the counter. The bytes that are not enabled will count anyway. The cycle time is selected by the MODE[5..4] register bits. The following table indicates the clock period for each of the combinations:

| MODE[54] | period |

|----------|--------|

| 00       | 20nS   |

| 01       | 40nS   |

| 10       | 80nS   |

| 11       | 160nS  |

Page 11 28th October, 1998

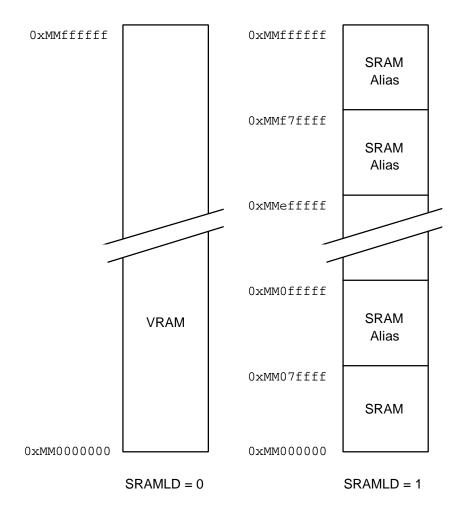

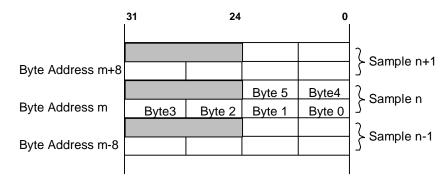

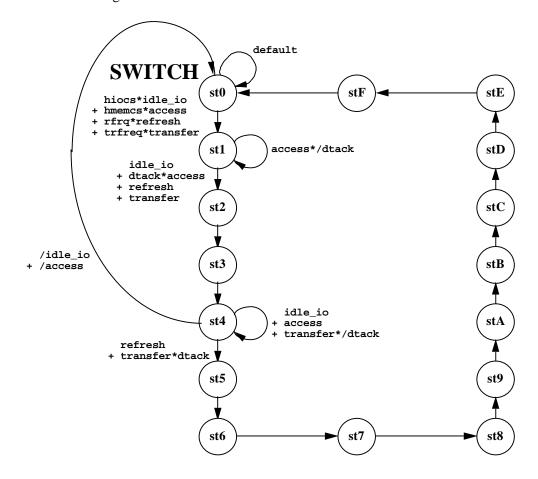

## Sample Buffer Memory Map

The Sample buffer is mapped simply into EISA memory space according to the value of the ADDRMAP register and the SRAMLD bit in the MODE register. As a precaution, the memory map of the board is disabled at power up and after a board reset (after a power- UP or a write to RESET). The SRAMLD bit determines whether the VRAM buffer or the trace SRAM is mapped into EISA memory space. The two cannot be accessed concurrently. The diagram below illustrates the memory map.

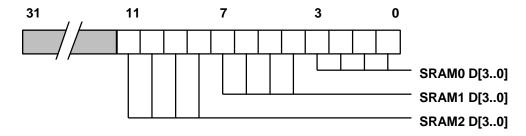

Each 48 bit sample is aligned on a 64 bit boundary in memory as shown below:

Page 12 28th October, 1998

Page 13 28th October, 1998

## **Trigger/Trace Setup**

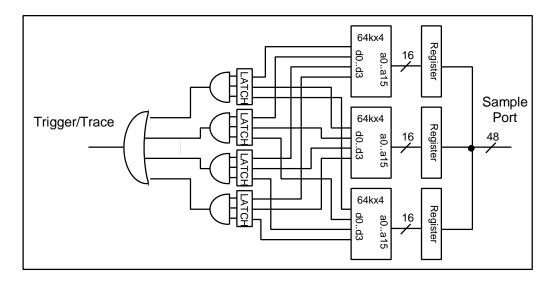

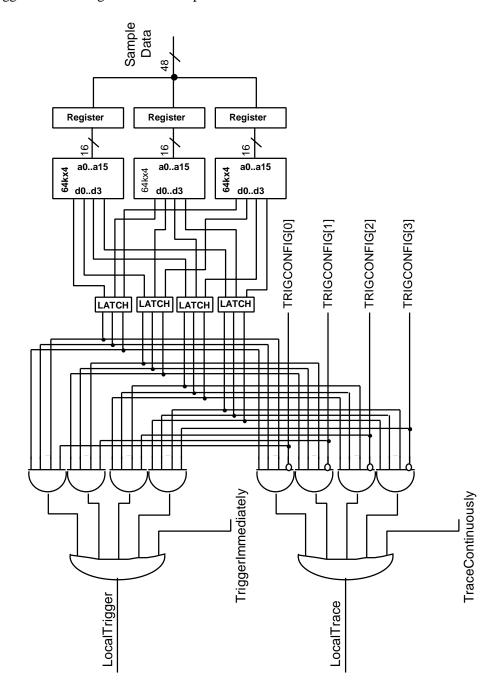

A simplified schematic of the trigger and trace system is shown below.

Essentially, the 48 bit sample data path is broken into three contiguous groups of 16 bits which are connected to the address lines of three 64kx4 SRAMs. SRAM0 a[15..0] is connected to sample data sd[15..0], SRAM1 a[15..0] is connected to sd[31..16] and SRAM2 a[15..0] to sd[47..32]. Each SRAM data line is ANDed with the corresponding data lines from the other two SRAMs and these products are ORed together to give the trigger or trace result.

A triplet of data bits from each SRAM (e.g. d0 on SRAM0 & SRAM1 & SRAM2) is called a *trace channel* and is individually selectable to be a *trigger* (if trigger value is matched, stop sampling when STOPCOUNT register reaches zero) or a *trace* (store sample only if trace value is matched).

Channels are selected as trace or trigger by writing the TRIGCONFIG register. Bits [3..0] of this register individually select the four trace channels as trigger (if set to one) or trace (if reset to zero).

To read or write the SRAM, first the SRAMLD bit of the MODE register must be set, and the RECORD bit must be reset. This disables sampling and maps the SRAM into the lower 128k of the EISA memory address space. Usually PAUSE would also be set. All three SRAMs are read/written together. SRAM0 data is buffered to EISA D[3..0], SRAM1 to EISA D[7..4] and SRAM2 to EISA D[11..9].

By programming the SRAMs with the right values it is possible to trace and/or trigger on multiple different values and even arbitrary ranges of values.

Page 14 28th October, 1998

#### Trace Example 1: Trace/Trigger on a Single Value (D = x)

Suppose the 48 bit value to trace/trigger on is 0x123456789ABC

Choose a trigger/trace channel, say channel #1 (bit zero in each SRAM):

Write a logic 1 into the SRAMLD and PAUSE bits in the MODE register, and a logic 0 into the RECORD bit:

```

(I/O 0xZ008) := (I/O 0xZ008) AND 0xFFFFFFFB (I/O 0xZ008) := (I/O 0xZ008) OR 0x00000003

```

Set up the configuration bit for channel #1

```

(I/O 0xZ00C) := (I/O 0xZ00c) AND 0xFFFFFFFE (Trace)

(I/O 0xZ00C) := (I/O 0xZ00c) OR 0x00000001 (Trigger)

```

Break the value into three blocks of 16 bits and shift left by 2 to calculate the SRAM address:

```

0x1234 << 2 = 0x048D0

0x5678 << 2 = 0x259E0

0x9ABC << 2 = 0x26AF0

```

Write the trigger bitmap into SRAM:

```

(Mem 0xMMX048D0) := 0xXXXXX100

(Mem 0xMMX259E0) := 0xXXXXX010

(Mem 0xMMX26AF0) := 0xXXXXX001

```

#### Trace Example 2: Trace/Trigger on Multiple Values $(D = x \mid y)$

There are two options to load multiple values into the SRAM. It is possible to use a different channel per value but this limits the number of values to four. However if the values happen to occur in the same 64kSample block. (e.g. the two values 0x12345678DEAD and 0x12345678BEEF occur in the same 64kSample block) they can both be put into the same channel.

#### Trace Example 3: WildCarding or "Don't Care" bits.

Sometimes a trace or trigger channel requires that certain bits be wild cards or "don't care". In these cases it is necessary to program the SRAM such that the data read back is high regardless of the state of the wildcard bit. In effect all this means is that a one must be written into the SRAM at the addresses corresponding to the sample data being high and also at the addresses where the sample data is low. Suppose that in the first example bit five must be wildcarded. The trace value is thus:

```

0x123456789A$C where $ == binary 10X1

```

The procedure is the same as before except two addresses are written into SRAM0 the addresses 0xMMX26AF0 & 0xMMX26AF0.

Page 15 28th October, 1998

When two wildcards occur (in the same 64kSample block), there must be four addresses written, and with three wildcard bits, eight addresses and so on. To wildcard sixteen bits, all 64k addresses must be filled with ones in the correct channel.

All updates to the trace SRAM should be ORed in to avoid upsetting the data in different channels.

#### Trace Example 3: Trace/Trigger on a Range (x = D = y)

There are two cases:

Case1: Range occurs entirely within one 64kSample block

```

Trigger on range 0x12345678BEEF = Sample = 0x12345678DEAD

```

Calculate bitmap as before and write bits into SRAM2 & SRAM1. SRAM0 must have a range of addresses written. The Start and finishing addresses are:

```

0xBEEF \ll 2 = 0x2FBBC

0xDEAD \ll 2 = 0x37AB4

```

Note that writing 0x001 into these addresses may overwrite the information in SRAM1 & SRAM2 so the value must be ORed in. The following pseudocode illustrates this:

As with multiple single values, multiple ranges can be placed in the same channel provided they all fall within the same block. Ranges that consist of exact multiples of 64kSamples can also fit in one channel. In this case the lower sixteen bits of the sample data are wildcarded.

#### **Case 2:** Range Overlaps a 64kSample boundary:

If the range overlaps a 64kSample boundary the range must be broken into two ranges and each programmed into a different channel. e.g. the two values 0x12346578ABCD and 0x12345679ABCD specify a range that overlaps one boundary. In this example the range can be broken into two ranges, viz:

```

0x12345678ABCD - 0x12345678FFFF

0x123456790000 - 0x12345679ABCD

```

These ranges will each fit into separate channels as in Case 1 above.

Page 16 28th October, 1998

## **Setup Sequences**

The interactions between RECORD, SRAMLD and OUTPUTENA[5..0] mean that the various registers must be written in an order that precludes these interactions.from undoing the effect of prior writes. As an example, let us consider the sequence of actions needed for starting a trace.

1. Firstly the PAUSE and SRAMLD of the MODE register should be set to a logic 1 and the RECORD bit reset to a logic 0. PAUSE=1 stops tracing. RECORD=0 disables both the sample input buffers and the timestamp buffers, which is a necessary condition for accessing the SRAM with SRAMLD=1.

```

(I/O \ 0xZ008) := (I/O \ 0xZ008) \ AND \ 0xFFFFFFB

(I/O \ 0xZ008) := (I/O \ 0xZ008) \ OR \ 0x00000003

```

- 2. Next the trigger and trace patterns can be preloaded into the SRAM as discussed above.

- 3. Then the trigger/trace configuration can be written to TRIGCONFIG[5..0].

```

(I/O \ OxZOOC) := 0x0000000X (where x is the desired value)

```

4. After this, the STOPCOUNT can be written.

```

(I/O 0xZ014) := 0x00xxx000 (where xxx is the desired value)

```

5. Then the HEADPTR can be written.

```

(I/O \ 0xZ018) := 0x00XXX000 (where XXX is the desired value)

```

6. At this point the RECORD bit needs to be set, before OUTPUTENA is written to, so that when the latter is done, it won't be undone by a subsequent toggle of the RECORD bit.

```

(I/O \ OxZ008) := (I/O \ OxZ008) \ OR \ Ox00000004

```

7. Now OUTPUTENA[5..0] can be written, to enable the sample input buffers or timestamp buffers as required.

```

(I/O \ OxZO1C) := OxOOOOOOOX (where X is the desired value)

```

8. Finally the PAUSE and SRAMLD bits can be reset to allow tracing to begin.

```

(I/O 0xZ008) := (I/O 0xZ008) AND 0xFFFFFFC

```

## **DMA** and Transparent Operation

The EISA interface has been designed as a 33MByte/sec bursting slave that allows data to be read out transparently and asynchronously without affecting data acquisition. The WRAP bit of the MODE register causes the board to ingnore the STOPCOUNT counter and continue sampling when it reaches zero. If this bit is set, then the VRAM buffer wraps around and can be continuously read out via the EISA interface without stopping the sample clock. If it is possible to atomically update the STOPCOUNT register, then very long traces may be generated, provided the data can be read out of the EISA interface, and stored, as fast as it is acquired.

Page 17 28th October, 1998

The DONE bit of the STATUS register allows a very simple loop to be constructed:

```

... set up registers, etc.

/* now start tracing to bottom half of VRAM */

(I/O 0xZ008) := (I/O 0xZ008) AND 0xFFFFFFD

(clear PAUSE)

(I/O 0xZ018) := 0x00000000

(HEADPTR <- bottom half of VRAM)

(I/O 0xZ014) := 0x00800000

(STOPCOUNT <- half VRAM size)

while(1)

do

sleep(1)

}while !(DONE)

/* then start tracing to top half of VRAM */

(I/O 0xZ018) := 0x00800000

(HEADPTR <- top half of VRAM)

(I/O 0xZ014) := 0x00800000

(STOPCOUNT <- half VRAM size)

/* and concurrently read and store bottom half of VRAM */

read and store(0x00000000)

sleep(1)

}while !(DONE)

/* go back to tracing to bottom half of VRAM */

(I/O 0xZ018) := 0x00000000

(HEADPTR <- bottom half of VRAM)

(I/O 0xZ014) := 0x00800000

(STOPCOUNT <- half VRAM size)

/* and concurrently read and store top half of VRAM */

read_and_store(0x00800000)

```

Generally the reading and storing would be done via DMA. The DMAENA bit of the MODE register enables the board to request the host machine to perform DMA on EISA DMA channel 7 when the STOPCOUNT counter reaches zero - the DMA handler would normally do the starting of the next acquisition at the same time. Completion of the DMA transfer can be signalled via an interrupt. The IRQENA bit of the MODE register causes the board to assert EISA interrupt IRQ12. The interrupt is level triggered so that multiple boards can share the same interrupt.

Currently, however, neither DMAENA nor IRQENA are implemented. Neither are burst transfers enabled.

Alternatively, the functionality can be provided within a program loop. The Intel 80x86 string copy instruction is interruptable, allows very long strings to be copied from source to destination, and issues reads and writes as fast as they can be issued. It does, however, consume processor cycles. This will seriously affect a single-issue procesor, but is acceptable for multi-issue processors such as the PentiumPro or Pentium II. Unfortunately the EISA bus is not found on systems that accomodate the latter two processors.

Note that the TRACE CONTINOUSLY bit of the TRIGCONFIG register is not related to this usage of the board. This bit, when set, forces acceptance of every sample. Since one of the provisos for the above is that the data can be read out of the EISA interface, and stored, as fast as it is acquired, use of the TRACE CONTINOUSLY bit is only likely to exacerbate the difficulty of satisfying this proviso.

Page 18 28th October, 1998

## **Applications Programming Interface (API)**

In a Microsoft Windows 95 or NT environment, device access may be implemented via functions that are loaded when needed from a Dynamic Link Library (DLL), i.e. they are dynamically linked to the application during execution. The DLL then calls device drivers to perform the I/O. A generic DLL can be defined that will serve as an API for both Windows 95 and NT environments; an example is given in the next section. Unfortunately a generic device driver cannot be defined for both Windows 95 and NT, since their requirements are different. Hence these are separately discussed further below.

#### The appropriate API functions for the DT200.1 are:

```

void reset board(void);

//Reset board

void set_map(unsigned long address);

//Writes to ADDRMAP

// register

unsigned long get map(void);

//Read the current

// address mapping

void set mode(unsigned long flags);

//Writes to the MODE

// register

unsigned long get_mode(void);

//Read the current mode

void set_trig_config(unsigned long flags); //Write to the trigger

// config register

unsigned long get_trig_config(void);

//Read from the trigger

// config register

void reset_timestamp(void);

//Reset the timestamp

// counter

void set_stop_count(unsigned long flags); //Write to the

// STOPCOUNT register

unsigned long get_stop_count(void);

//Read from the

// STOPCOUNT register

//Write to the

void set_head_ptr(unsigned long flags);

// HEADPTR register

unsigned long get_head_ptr(void);

//Read from the

// HEADPTR register

void set_sbuf_output_enas(unsigned long flags); //Write to the

// OUTPUTENA register

unsigned long get_sbuf_output_enas(void); //Read from the

// OUTPUTENA register

unsigned long get_trace_status(void);

//Read from the

// STATUS buffer

unsigned long get_EISA_ID(void);

//Read from the EISA

// ID register

void get_EISAID(char *text_ID);

//Read from EISA ID

// register amd decode

void stop_trace(void);

//Stop trace

unsigned long *map_RAM(void);

//Map VRAM and SRAM

// into linear memory,

// return address 0x0

on error

void unmap_RAM(void);

//Unmap VRAM and SRAM

// read out VRAM or SRAM (start address specified)

// and store it in array:

BOOL store_RAM(unsigned long *array,

unsigned long start_address_offset,

unsigned long size_in_bytes);

```

Page 19 28th October, 1998

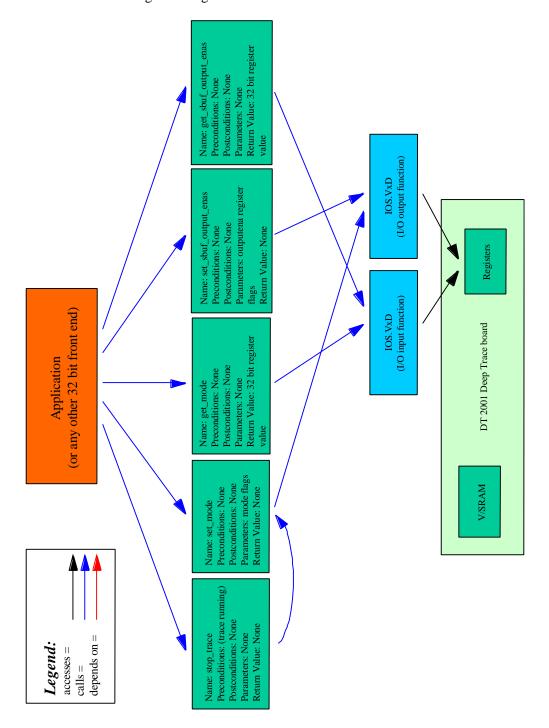

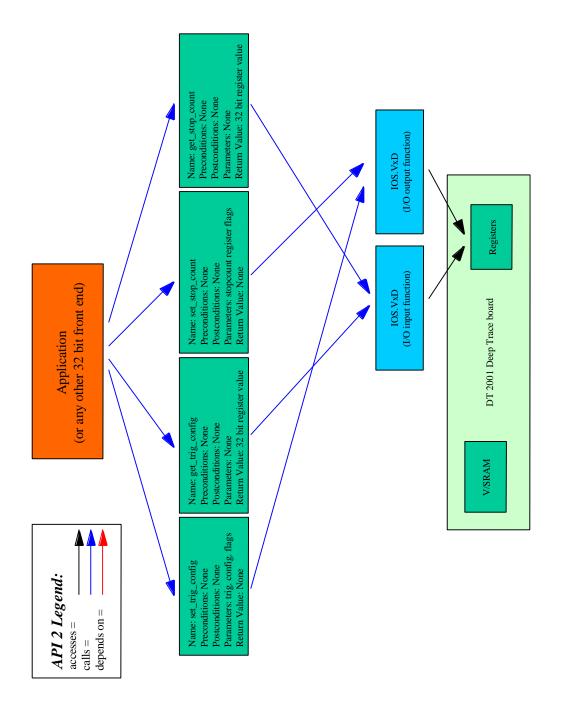

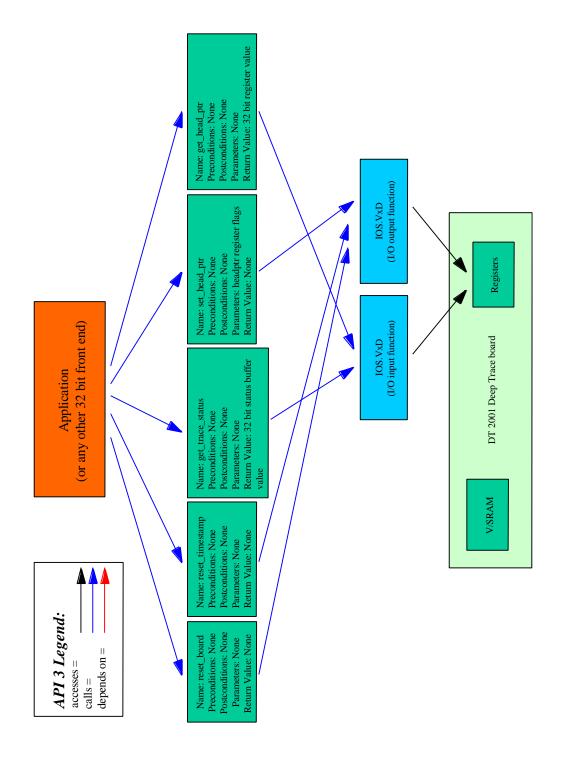

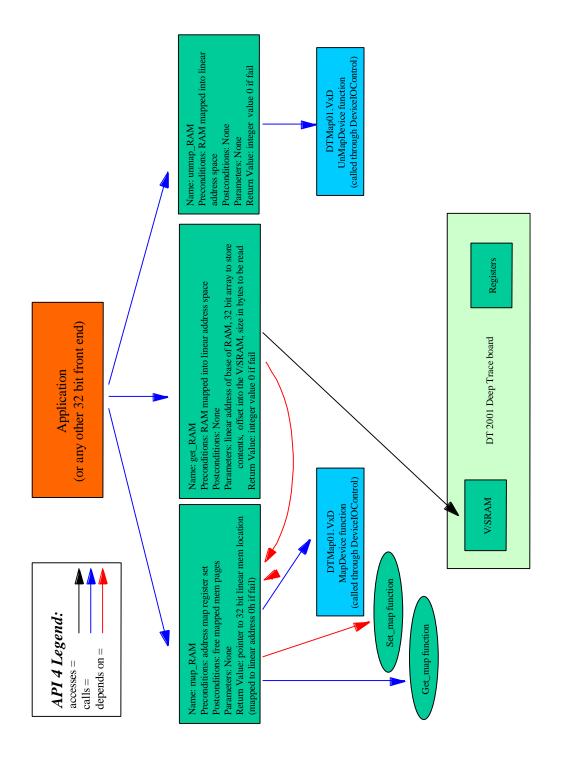

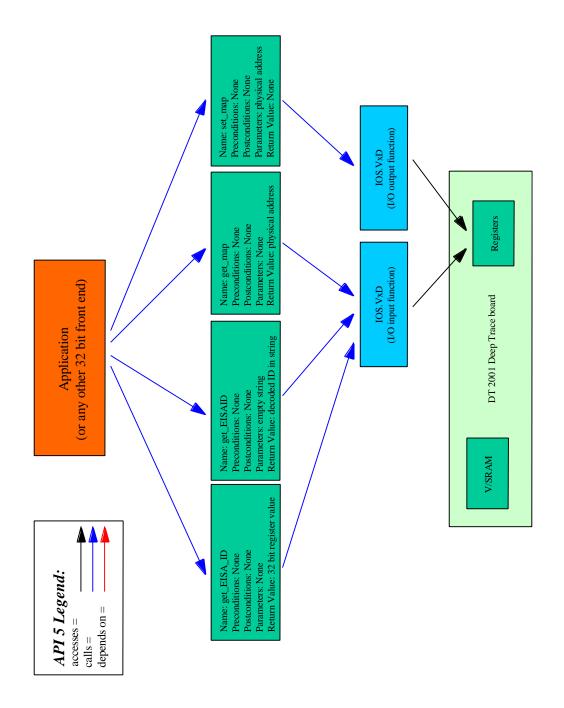

These API functions provide an applications interface suitable for programs written in high level languages like C or Java, such as the example Java application given further again below. The API is illustrated in the following four diagrams:

Page 20 28th October, 1998

Page 21 28th October, 1998

Page 22 28th October, 1998

Page 23 28th October, 1998

Page 24 28th October, 1998

## **Generic Dynamic Link Library (DLL)**

A generic DLL **definition file MapDev.h** for the DT200.1 is as follows:

```

// MAPDEV.h - include file for VxD MAPDEV

// Copyright (c) 1996 Vireo Software, Inc.

#ifndef NotVxD

#include <vtoolsc.h>

#define MAPDEV_Major

#define MAPDEV Minor

#define MAPDEV_DeviceID

UNDEFINED DEVICE ID

#define MAPDEV_Init_Order

UNDEFINED_INIT_ORDER

#define LPVOID PVOID

#endif

// This is the request structure that applications use

// to request services from the MAPDEV VxD.

typedef struct _MapDevRequest

// supplied by caller

DWORD mdr_ServiceID;

LPVOID mdr_PhysicalAddress; // supplied by caller

DWORD mdr_SizeInBytes; // supplied by caller

LPVOID mdr_LinearAddress; // returned by VxD

WORD mdr_Selector; // returned if 16-bit caller

WORD mdr_Status; // MDR_xxxx code below

} MAPDEVREQUEST, *PMAPDEVREQUEST;

#define MDR_SERVICE_MAP

CTL_CODE(FILE_DEVICE_UNKNOWN, 1,

METHOD_NEITHER, FILE_ANY_ACCESS)

#define MDR SERVICE UNMAP

CTL CODE(FILE DEVICE UNKNOWN, 2,

METHOD_NEITHER, FILE_ANY_ACCESS)

#define MDR_STATUS_SUCCESS

1

0

#define MDR_STATUS_ERROR

```

#### The associated $\underline{C}++$ source file MapDev.cpp for the DLL is:

```

#include <windows.h>

#include <winioctl.h>

#include <conio.h>

#include <memory.h>

#define NotVxD

#include "DT2001.h"

#include "DTMap01.h"

/*

// DLL Entry Point disabled since not used

// Note: The DLL entry point function is disables at the moment because Visual Basic doesn't seem to be able to call it; (no loadlib function provided).

```

Page 25 28th October, 1998

```

BOOL WINAPI DllEntryPoint (HINSTANCE hDLL,

DWORD dwReason,

LPVOID Reserved)

BOOL Success = TRUE;

switch (dwReason)

case DLL_PROCESS_ATTACH:

//reset_board();

//set_map(PHY_ADDR);//set physical address of VRAM/SRAM

//map_RAM();//set linear address of VRAM/SRAM

break;

}

case DLL_PROCESS_DETACH:

//unmap_RAM();

//reset_board();

break;

case DLL_THREAD_ATTACH: break;

case DLL_THREAD_DETACH: break;

return Success;

//Global Declarations:

HANDLE hDevice;

//handle for VxD

//resets board

__declspec( dllexport ) void __stdcall

reset_board(void)

_outpd(BASE_ADDR | REG_RESET, ANYVALUE);

}

//Writes to ADDRMAP register

// input: is physical address the VRAM/SRAM is to appear at

__declspec( dllexport ) void __stdcall

set_map(unsigned long address)

_outpd(BASE_ADDR | REG_ADDRMAP, address);

//Read the current physical address mapping

__declspec( dllexport ) unsigned long __stdcall

get_map(void)

return (_inpd(BASE_ADDR | REG_ADDRMAP) & 0xFF000000);

//Writes to the MODE register

__declspec( dllexport ) void __stdcall

set_mode(unsigned long flags)

_outp(BASE_ADDR | REG_MODE, (int)flags);

//Read the current mode

```

Page 26 28th October, 1998

```

__declspec( dllexport ) unsigned long __stdcall

get_mode(void)

{

return (((unsigned long) _inp(BASE_ADDR | REG_MODE)) &

0x00000 0FF);

//Write to the trigger config register

__declspec( dllexport ) void __stdcall

set_trig_config(unsigned long flags)

{

_outp(BASE_ADDR | REG_TRIGCONFIG, (int)flags);

//Read from the trigger config register

__declspec( dllexport ) unsigned long __stdcall

get_trig_config(void)

return (((unsigned long) _inp(BASE_ADDR | REG_TRIGCONFIG)) &

0 \times 0000003F);

}

//Reset the timestamp counter

__declspec( dllexport ) void __stdcall reset_timestamp(void)

{

_outpd(BASE_ADDR | REG_TIMERESET, ANYVALUE);

//Write to the STOPCOUNT register

__declspec( dllexport ) void __stdcall

set_stop_count(unsigned long flags)

_outpd(BASE_ADDR | REG_STOPCOUNT, flags);

}

//Read from the STOPCOUNT register

__declspec( dllexport ) unsigned long __stdcall

get_stop_count(void)

return (_inpd(BASE_ADDR | REG_STOPCOUNT) & 0x00FF8000);

//Write to the HEADPTR register

__declspec( dllexport ) void __stdcall

set_head_ptr(long int head_ptr)

_outpd(BASE_ADDR | REG_HEADPTR, head_ptr);

//Read from the HEADPTR register

__declspec( dllexport ) unsigned long __stdcall

get_head_ptr(void)

return (_inpd(BASE_ADDR | REG_HEADPTR) & 0x00FF8000);

//Write to the OUTPUTENA register

__declspec( dllexport ) void __stdcall

set_sbuf_output_enas(unsigned long flags)

{

```

Page 27 28th October, 1998

```

_outp(BASE_ADDR | REG_OUTPUTENA, (int)flags);

}

//Read from the OUTPUTENA register

__declspec( dllexport ) unsigned long __stdcall

get_sbuf_output_enas(void)

{

return (((unsigned long)_inp(BASE_ADDR | REG_OUTPUTENA)) &

0x0000003F);

}

//Read from the STATUS buffer

__declspec( dllexport ) unsigned long __stdcall

get_trace_status(void)

{

return (_inpd(BASE_ADDR | REG_STATUS) & 0x00008000);

}

//Read from the EISA ID register

__declspec( dllexport ) unsigned long __stdcall

get_EISA_ID(void)

return _inpd(BASE_ADDR | REG_EISAID);

}

//Read from EISA ID register amd decode string

// input: pointer to a char array (min 7 chars long)

__declspec( dllexport ) unsigned long __stdcall

get EISAID(char *text ID)

{

unsigned int chars;

unsigned int digits;

unsigned long reg = _inpd(BASE_ADDR | REG_EISAID);

chars = reg;

digits = reg >> 16;

text_{ID}[0] = (char) ( (chars & 0x007C) >> 2) + 0x40;

text_ID[1] = (char) ((( chars & 0x0003) << 3) |

((chars & 0xE000) >> 13)) + 0x40;

text_{ID[2]} = (char) ( (chars & 0x1F00) >> 8) + 0x40;

text_{ID[3]} = (char) ((digits & 0x00F0) >> 4) + '0';

text_{ID}[4] = (char) ( (digits & 0x000F) >> 0) + '0';

text_ID[5] = (char) ( (digits & 0xF000) >> 12) + '0';

text_{ID[6]} = (char) ( (digits & 0x0F00) >> 8) + '0';

text_ID[7] = 0;

return 1;

}

//Stop trace

__declspec( dllexport ) void __stdcall

stop_trace(void)

set_mode(PAUSE);

//Map VRAM and SRAM into linear memory, returns a pointer

// to base (32bit)

__declspec( dllexport ) unsigned long __stdcall

map_RAM(void)

{

DWORD cbBytesReturned;//count of bytes returned from VxD

```

Page 28 28th October, 1998

```

MAPDEVREQUEST req;

//VxD request structure

PVOID inBuf[1];

//buffer for DevIOCrtl pointer

// to req structure

const PCHAR VxDName = "\\\.\\DTMAP01.VXD";

const PCHAR VxDNameAlreadyLoaded = "\\\.\\DTMAP01";

hDevice = CreateFile(VxDName, 0,0,0,

CREATE_NEW, FILE_FLAG_DELETE_ON_CLOSE, 0);

if (hDevice == INVALID_HANDLE_VALUE)

hDevice = CreateFile(VxDNameAlreadyLoaded, 0,0,0,

CREATE_NEW, FILE_FLAG_DELETE_ON_CLOSE, 0);

if (hDevice == INVALID_HANDLE_VALUE)

return (unsigned long) GetLastError();//error!

else

//set up request structure:

req.mdr_ServiceID = MDR_SERVICE_MAP;

req.mdr_PhysicalAddress = (PVOID) get_map();

req.mdr_SizeInBytes = VRAM_SIZE;

inBuf[0] = &req;

//call Win32 API Message DeviceIOControl:

if(! DeviceIoControl(hDevice, MDR_SERVICE_MAP, inBuf,

sizeof(PVOID), NULL, 0,

&cbBytesReturned, NULL))

return 0;

else

return (unsigned long) req.mdr_LinearAddress;//Success!

}

}

//Unmap VRAM and SRAM

//uses the VxD, frees the linear address space

__declspec ( dllexport ) int __stdcall

unmap_RAM(void)

{

DWORD cbBytesReturned; //count of bytes returned from VxD

MAPDEVREQUEST req;

//VxD request structure

PVOID inBuf[1];

const PCHAR VxDName = "\\\.\\DTMAP01.VXD";

const PCHAR VxDNameAlreadyLoaded = "\\\.\\DTMAP01";

if (hDevice == INVALID_HANDLE_VALUE)

hDevice = CreateFile(VxDNameAlreadyLoaded, 0,0,0,

CREATE_NEW, FILE_FLAG_DELETE_ON_CLOSE, 0);

if (hDevice == INVALID HANDLE VALUE)

return 0;//error! can't get a handle on VxD

else

//set up request structure:

req.mdr_ServiceID = MDR_SERVICE_UNMAP;

req.mdr_PhysicalAddress = (void *) get_map();

reg.mdr SizeInBytes = VRAM SIZE;

inBuf[0]=&req;

//call Win32 API Message DeviceIOControl:

if (! DeviceIoControl(hDevice, MDR_SERVICE_UNMAP, inBuf,

sizeof(PVOID), NULL, 0,

&cbBytesReturned, NULL))

```

Page 29 28th October, 1998

```

return 0;//error! call to VxD failed

else

return 1; //success!

}

}

//read out SRAM or VRAM and store in array

//input: array of 32bit storage locations, offset address

//

into the VRAM/SRAM and the #bytes to read out

//output: TURE if success, FALSE if fail

__declspec( dllexport ) int __stdcall

get_RAM(PBYTE Map_Address,

unsigned long *array,

unsigned long start_address_offset,

unsigned long size_in_bytes)

int success = TRUE;

//boudary checking:

if (get_mode() & SRAMLD)

//access SRAM

if ((start address offset + size in bytes) > SRAM SIZE)

success = FALSE;

else

//access VRAM

if ((start_address_offset + size_in_bytes) > VRAM_SIZE)

success = FALSE;

else

memcpy(array,Map_Address + start_address_offset,

size_in_bytes);//read out RAM and store in array

return success;

}

```

#### An appropriate **compiler description file MapDev.dsp** would be:

```

# Microsoft Developer Studio Project File - Name="DT2001"

- Package Owner=<4>

# Microsoft Developer Studio Generated Build File, Format

Version 5.00

# ** DO NOT EDIT **

# TARGTYPE "Win32 (x86) Dynamic-Link Library" 0x0102

CFG=DT2001 - Win32 Debug

!MESSAGE This is not a valid makefile. To build this project

!MESSAGE using NMAKE, use the Export Makefile command and run :

!MESSAGE

!MESSAGE NMAKE /f "DT2001.MAK".

!MESSAGE

!MESSAGE You can specify a configuration when running NMAKE

!MESSAGE by defining the macro CFG on the command line.

```

Page 30 28th October, 1998

```

!MESSAGE For example:

!MESSAGE

!MESSAGE NMAKE /f "DT2001.MAK" CFG="DT2001 - Win32 Debug"

!MESSAGE

!MESSAGE Possible choices for configuration are:

!MESSAGE

!MESSAGE "DT2001 - Win32 Release"

!MESSAGE

(based on "Win32 (x86) Dynamic-Link Library")

!MESSAGE "DT2001 - Win32 Debug"

(based on "Win32 (x86) Dynamic-Link Library")

! MESSAGE

!MESSAGE

# Begin Project

# PROP Scc_ProjName ""

# PROP Scc_LocalPath ""

CPP=cl.exe

MTL=midl.exe

RSC=rc.exe

!IF "$(CFG)" == "DT2001 - Win32 Release"

# PROP BASE Use MFC 0

# PROP BASE Use_Debug_Libraries 0

# PROP BASE Output_Dir "Release"

# PROP BASE Intermediate_Dir "Release"

# PROP BASE Target Dir ""

# PROP Use MFC 0

# PROP Use_Debug_Libraries 0

# PROP Output Dir "Release"

# PROP Intermediate_Dir "Release"

# PROP Target_Dir ""

# ADD BASE CPP /nologo /MT /W3 /GX /O2 /D "WIN32" /D "NDEBUG" /D

"_WINDOWS" /YX /FD /c

# ADD CPP /nologo /MT /W3 /GX /O2 /D "WIN32" /D "NDEBUG" /D

"_WINDOWS" /YX /FD /c

# ADD BASE MTL /nologo /D "NDEBUG" /mktyplib203 /o NUL /win32

# ADD MTL /nologo /D "NDEBUG" /mktyplib203 /o NUL /win32

# ADD BASE RSC /1 0x1809 /d "NDEBUG"

# ADD RSC /1 0x1809 /d "NDEBUG"

BSC32=bscmake.exe

# ADD BASE BSC32 /nologo

# ADD BSC32 /nologo

LINK32=link.exe

# ADD BASE LINK32 kernel32.lib user32.lib gdi32.lib winspool.lib

comdlg32.lib advapi32.lib shell32.lib ole32.lib oleaut32.lib

uuid.lib odbc32.lib odbccp32.lib /nologo /subsystem:windows

/dll /machine:I386

# ADD LINK32 kernel32.lib user32.lib gdi32.lib winspool.lib

comdlq32.lib advapi32.lib shell32.lib ole32.lib oleaut32.lib

uuid.lib odbc32.lib odbccp32.lib /nologo /subsystem:windows

/dll /machine:I386

!ELSEIF "$(CFG)" == "DT2001 - Win32 Debug"

# PROP BASE Use_MFC 0

# PROP BASE Use_Debug_Libraries 1

# PROP BASE Output_Dir "Debug"

# PROP BASE Intermediate_Dir "Debug"

# PROP BASE Target_Dir ""

# PROP Use_MFC 0

# PROP Use_Debug_Libraries 1

```

Page 31 28th October, 1998

```

# PROP Output Dir "Debug"

# PROP Intermediate_Dir "Debug"

# PROP Target_Dir ""

# ADD BASE CPP /nologo /MTd /W3 /Gm /GX /Zi /Od /D "WIN32" /D

"_DEBUG" /D "_WINDOWS" /YX /FD /c

# ADD CPP /nologo /MTd /W3 /Gm /GX /Zi /Od /D "WIN32" /D

"_DEBUG" /D "_WINDOWS" /YX /FD /c

# ADD BASE MTL /nologo /D "_DEBUG" /mktyplib203 /o NUL /win32

# ADD MTL /nologo /D "_DEBUG" /mktyplib203 /o NUL /win32

# ADD BASE RSC /l 0x1809 /d "_DEBUG"

# ADD RSC /1 0x1809 /d "_DEBUG"

BSC32=bscmake.exe

# ADD BASE BSC32 /nologo

# ADD BSC32 /nologo

LINK32=link.exe

# ADD BASE LINK32 kernel32.lib user32.lib qdi32.lib winspool.lib

comdlq32.lib advapi32.lib shell32.lib ole32.lib oleaut32.lib

uuid.lib odbc32.lib odbccp32.lib /nologo /subsystem:windows

/dll /debug /machine:I386 /pdbtype:sept

# ADD LINK32 kernel32.lib user32.lib gdi32.lib winspool.lib

comdlg32.lib advapi32.lib shell32.lib ole32.lib oleaut32.lib

uuid.lib odbc32.lib odbccp32.lib /nologo /subsystem:windows

/dll /debug /machine:I386 /pdbtype:sept

!ENDIF

# Begin Target

# Name "DT2001 - Win32 Release"

# Name "DT2001 - Win32 Debug"

# Begin Source File

SOURCE=.\DT2001.cpp

# End Source File

# Begin Source File

SOURCE=.\dt2001.def

# End Source File

# Begin Source File

SOURCE=.\DT2001.h

# End Source File

# End Target

# End Project

```

Page 32 28th October, 1998

#### Windows 95 Virtual Device Driver (VxD)

Since the board uses both I/O for the registers and normal memory space for the VRAM and SRAM, the most efficient implementation in a Microsoft Windows 95 is to use the IOS.VxD driver for the I/O space and write a custom driver for the memory mapping for the VRAM and SRAM. The memory map driver is called DTMap01.VxD. The IOS.VxD driver comes with Windows 95 and is located in the SYSTEM folder of a Windows 95 system. It is also sensible to use the Win32 API to program the driver since it allows easy porting of the driver to Windows NT, as well as being the fastest and most reliable API for Microsoft products. The Win32 API uses control messages to access VxDs, in particular DeviceIOControl.. The driver is derived from an example found in the VToolsD programming package (Vireo Software Inc.). This is called MapDev.VxD and is located in the Examples folder of the VToolsD installation.

#### A sample **definition file DTMap01**. h would be:

```

// DTMAP01.h - include file for VxD DTMap01

#ifndef NotVxD

#include <vtoolsc.h>

#define MAPDEV_Major

1

#define MAPDEV_Minor

0

#define MAPDEV_DeviceID

UNDEFINED DEVICE ID

#define MAPDEV_Init_Order

UNDEFINED_INIT_ORDER

#define LPVOID PVOID

#endif

// This is the request structure that applications use

// to request services from the MAPDEV VxD.

typedef struct _MapDevRequest

DWORD mdr_ServiceID;

// supplied by caller

LPVOID mdr_PhysicalAddress;

// supplied by caller

// supplied by caller

DWORD mdr_SizeInBytes;

LPVOID mdr_LinearAddress;

// returned by VxD

// returned if 16-bit caller

mdr_Selector;

WORD

// MDR_xxxx code below

WORD

mdr_Status;

MAPDEVREQUEST, *PMAPDEVREQUEST;

#define MDR_SERVICE_MAP

CTL_CODE(FILE_DEVICE_UNKNOWN, 1,

METHOD_NEITHER, FILE_ANY_ACCESS)

#define MDR_SERVICE_UNMAP

CTL_CODE(FILE_DEVICE_UNKNOWN, 2,

METHOD_NEITHER, FILE_ANY_ACCESS)

#define MDR STATUS SUCCESS

1

#define MDR_STATUS_ERROR

0

```

Page 33 28th October, 1998

The associated **C source file** DTMap01.c for the VxD is:

```

//Deep Trace VxD driver for Windows95

//Erich Barnstedt

//VERSION V1.0

#define PAGENUM(p)

(((ULONG)(p)) >> 12)

#define PAGEOFF(p)

#define PAGEBASE(p)

#define NDAGE

(((ULONG)(p)) & 0xFFF)

(((ULONG)(p)) \& \sim 0xFFF)

\#define \_NPAGES\_(p, k) ((PAGENUM((char*)p+(k-1))

- PAGENUM(p)) + 1)

#define DEVICE_MAIN

#include "dtmap01.h"

#undef DEVICE_MAIN

//Create device descriptor block (DDB):

Declare_Virtual_Device(MAPDEV)

//Handle "DeviceIOControl" control message:

DefineControlHandler(W32 DEVICEIOCONTROL, OnW32Deviceiocontrol);

//Control dispatcher:

BOOL __cdecl ControlDispatcher(

DWORD dwControlMessage,

DWORD EBX,

DWORD EDX,

DWORD ESI,

DWORD EDI,

DWORD ECX)

START_CONTROL_DISPATCH

ON_W32_DEVICEIOCONTROL(OnW32Deviceiocontrol);

END_CONTROL_DISPATCH

return TRUE;

}

// Device Mapping Function:

PVOID MapDevice(PVOID PhysAddress, DWORD SizeInBytes)

PVOID Linear;

//calc number of mem pages required:

ULONG nPages = _NPAGES_(PhysAddress, SizeInBytes);

//set aside linear mem space:

Linear = PageReserve(PR_PRIVATE, nPages, PR_FIXED);

//do physical to linear translation (map into user space):

PageCommitPhys(PAGENUM(Linear),nPages,PAGENUM(PhysAddress),

PC_INCR | PC_USER | PC_WRITEABLE);

return (PVOID) ((ULONG)Linear+PAGEOFF(PhysAddress));

}

// Device Unmapping Function:

// Input: Base of linear memory block

// Output: None

VOID UnmapDevice(PVOID LinearAddress)

```

Page 34 28th October, 1998

```

//free linear memory:

PageFree((MEMHANDLE)PAGEBASE(LinearAddress),0);

// W32_DEVICEIOCONTROL Handler for Win32 Applications:

// Input: The dioc_InBuf field of the parameter structure

// contains a pointer to the request structure

// Output: Fields of the request structure are updated

// according to the request.

DWORD OnW32Deviceiocontrol(PIOCTLPARAMS p)

PMAPDEVREQUEST pReq;

switch (p->dioc_IOCtlCode)

case DIOC OPEN:

case DIOC CLOSEHANDLE:

break;

//map request:

case MDR_SERVICE_MAP:

pReq = *(PMAPDEVREQUEST*)p->dioc_InBuf;

pReq->mdr_LinearAddress =

MapDevice(pReq->mdr_PhysicalAddress,

pReq->mdr_Size InBytes);

if (pReg->mdr LinearAddress == NULL)

pReq->mdr_Status = MDR_STATUS_ERROR;

pReg->mdr Status = MDR STATUS SUCCESS;

break;

//unmap request:

case MDR_SERVICE_UNMAP:

pReq = *(PMAPDEVREQUEST*)p->dioc_InBuf;

UnmapDevice(pReq->mdr_LinearAddress);

pReq->mdr_Status = MDR_STATUS_SUCCESS;

break;

default:

return ERROR INVALID FUNCTION;

return DEVIOCTL_NOERROR;

}

An appropriate makefile DTMap01.mak needs to invoke special tools from the VxD development

environment:

# DTMAP01.mak - makefile for VxD DTMap01

DEVICENAME = DTMAP01

DYNAMIC = 1

FRAMEWORK = C

DEBUG = 1

OBJECTS = DTMap01.OBJ

```

Page 35 28th October, 1998

!include \$(VTOOLSD)\include\vtoolsd.mak

!include \$(VTOOLSD)\include\vxdtarg.mak

DTMap01.OBJ: DTMap01.c DTMap01.h

#### Windows NT Device Driver

An example Windows NT device driver is shown below. The **definition file** mapmem.h is as follows:

```

#define FILE DEVICE MAPMEM 0x00008000

#define MAPMEM_IOCTL_INDEX 0x800

// Define our own private IOCTL

#define MDR_SERVICE_MAP CTL_CODE(FILE_DEVICE_MAPMEM,

MAPMEM_IOCTL_INDEX,

METHOD BUFFERED,

FILE_ANY_ACCESS)

#define MDR SERVICE UNMAP CTL CODE(FILE DEVICE MAPMEM,

MAPMEM_IOCTL_INDEX+1,

METHOD_BUFFERED,

FILE_ANY_ACCESS)

// Our user mode app will pass an initialized structure like

// this down to the kernel mode driver

typedef struct _MapDevRequest

int

mdr_Service_ID;

unsigned long *mdr_PhysicalAddress;

mdr_SizeInBytes;

unsigned long *mdr LinearAddress;

unsigned char mdr_Selector;

unsigned char mdr_Status;

MAPDEVREQUEST, *PMAPDEVREQUEST;

#define MDR_STATUS_SUCCESS

#define MDR_STAUTS_ERROR

0

#define MAPDEV_Major

1

#define MAPDEV_Minor

#define MAPDEV_DeviceID

#define MAPDEV_Init_Order

UNDEFINED_DEVICE_ID

UNDEFINED INIT ORDER

```

#### The C source file mapmem.c is:

Notes:

```

/*++

A simple driver sample which shows how to map physical memory

into a user-mode process's adrress space using the

Zw*MapViewOfSection APIs.

Environment:

kernel mode only

```

For the sake of simplicity this sample does not attempt to recognize resource conflicts with other drivers/devices. A real-world driver would call IoReportResource usage to determine whether or not the resource is available, and if so, register the resource under it's name.

Page 36 28th October, 1998

```

_-*/

#include "ntddk.h"

#include "mapmem.h"

#include "stdarg.h"

//function prototypes:

NTSTATUS MapMemDispatch(IN PDEVICE_OBJECT DeviceObject,

IN PIRP Irp);

VOID MapMemUnload(IN PDRIVER_OBJECT DriverObject);

NTSTATUS MapMemMapTheMemory(IN PDEVICE_OBJECT DeviceObject,

IN OUT PVOID ioBuffer,

IN ULONG inputBufferLength,

IN ULONG outputBufferLength);

#if DBG

#define MapMemKdPrint(arg) DbgPrint arg

#define MapMemKdPrint(arg)

#endif

//no changes made in this routine:

NTSTATUS DriverEntry(IN PDRIVER_OBJECT DriverObject,

IN PUNICODE_STRING RegistryPath)

/*

Routine Description: Installable driver initialization entry

point. This entry point is called directly by the I/O system.

Arguments:

DriverObject - pointer to the driver object

RegistryPath - pointer to a unicode string representing the

path to driver-specific key in the registry

Return Value:

STATUS_SUCCESS if successful,

STATUS_UNSUCCESSFUL otherwise

* /

{

PDEVICE_OBJECT deviceObject = NULL;

NTSTATUS

ntStatus;

deviceNameBuffer[] = L"\\Device\\MapMem";

UNICODE_STRING deviceNameUnicodeString;

deviceLinkBuffer[] = L"\\DosDe vices\\MAPMEM";

UNICODE_STRING deviceLinkUnicodeString;

MapMemKdPrint (("MAPMEM.SYS: entering DriverEntry\n"));

// Create an EXCLUSIVE device object (only 1 thread at a time

// can make requests to this device)

RtlInitUnicodeString (&deviceNameUnicodeString,

deviceNameBuffer);

ntStatus = IoCreateDevice(DriverObject, 0,

&deviceNameUnicodeString,

FILE_DEVICE_MAPMEM, 0, TRUE,

&deviceObject);

if (NT_SUCCESS(ntStatus))

// Create dispatch points for device control, create

// and close.

DriverObject->MajorFunction[IRP_MJ_CREATE] =

MapMemDispatch;

DriverObject->MajorFunction[IRP_MJ_CLOSE] =

```

Page 37 28th October, 1998

```

MapMemDispatch;

DriverObject->MajorFunction[IRP_MJ_DEVICE_CONTROL] =

MapMemDispatch;

DriverObject->DriverUnload = MapMemUnload;

// Create a symbolic link, e.g. a name that a Win32 app can

// specify to open the device

RtlInitUnicodeString(&deviceLinkUnicodeString,

deviceLinkBuffer);

ntStatus = IoCreateSymbolicLink (&deviceLinkUnicodeString,

&deviceNameUnicodeString);

if (!NT_SUCCESS(ntStatus))

// Symbolic link creation failed- note this & then

// delete the device object (it's useless if a Win32

// app can't get at it).

MapMemKdPrint(("MAPMEM.SYS: IoCreateSymbolicLink

failed\n"));

IoDeleteDevice (deviceObject);

}

else

MapMemKdPrint (("MAPMEM.SYS: IoCreateDevice failed\n"));

return ntStatus;

}

//no changes made, works as of 7/7/98 (tested from Control Panel)

NTSTATUS MapMemDispatch(IN PDEVICE_OBJECT DeviceObject,

IN PIRP Irp)

Routine Description: Process the IRPs sent to this device.

Arguments:

DeviceObject - pointer to a device object

- pointer to an I/O Request Packet

Irp

Return Value:

STATUS_SUCCESS if successful,

STATUS_UNSUCCESSFUL otherwise

* /

PIO_STACK_LOCATION irpStack;

PVOID

ioBuffer;

ULONG

inputBufferLength;

ULONG

outputBufferLength;

ULONG

ioControlCode;

NTSTATUS

ntStatus;

// Init to default settings- we only expect 1 type of

\ensuremath{//} IOCTL to roll through here, all others an error.

Irp->IoStatus.Status

= STATUS_SUCCESS;

Irp->IoStatus.Information = 0;

// Get a pointer to the current location in the Irp. This is

// where the function codes and parameters are located.

irpStack = IoGetCurrentIrpStackLocation(Irp);

// Get the pointer to the input/output buffer and it's length

ioBuffer = Irp->AssociatedIrp.SystemBuffer;

```

Page 38 28th October, 1998

```

inputBufferLength =

irpStack->Parameters.DeviceIoControl.InputBufferLength;

outputBufferLength =

irpStack->Parameters.DeviceIoControl.OutputBufferLength;

switch (irpStack->MajorFunction)

case IRP_MJ_CREATE:

MapMemKdPrint (("MAPMEM.SYS: IRP_MJ_CREATE\n"));

break;

case IRP_MJ_CLOSE:

MapMemKdPrint (("MAPMEM.SYS: IRP_MJ_CLOSE\n"));

break;

case IRP MJ DEVICE CONTROL:

ioControlCode =

irpStack->Parameters.DeviceIoControl.IoControlCode;

switch (ioControlCode)

case MDR_SERVICE_MAP:

Irp->IoStatus.Status = MapMemMapTheMemory (DeviceObject,

ioBuffer, inputBufferLength, outputBufferLength);

if (NT_SUCCESS(Irp->IoStatus.Status))

// Success! Set the following to sizeof(PVOID) to

// indicate we're passing valid data back.

Irp->IoStatus.Information = sizeof(PVOID);

MapMemKdPrint (("MAPMEM.SYS: memory successfully

mapped\n"));

else

Irp->IoStatus.Status = STATUS_INVALID_PARAMETER;

MapMemKdPrint (("MAPMEM.SYS: memory map failed

:( n");

break;

case MDR_SERVICE_UNMAP:

if (inputBufferLength >= sizeof(PVOID))

Irp->IoStatus.Status =

ZwUnmapViewOfSection ((HANDLE) -1,

*((PVOID *) ioBuffer));

MapMemKdPrint (("MAPMEM.SYS: memory successfully

unmapped\n"));

else

Irp->IoStatus.Status = STATUS_INSUFFICIENT_RESOURCES;

MapMemKdPrint (("MAPMEM.SYS: ZwUnmapViewOfSection

failed\n"));

break;

default:

MapMemKdPrint (("MAPMEM.SYS: unknown

IRP_MJ_DEVICE_CONTROL\n"));

Irp->IoStatus.Status = STATUS_INVALID_PARAMETER;

break;

```

Page 39 28th October, 1998

```

break;

// DON'T get cute and try to use the status field of

// the irp in the return status. That IRP IS GONE as

// soon as you call IoCompleteRequest.

ntStatus = Irp->IoStatus.Status;

IoCompleteRequest(Irp, IO_NO_INCREMENT);

// We never have pending operation so always return the

// status code.

return ntStatus;

}

//no changes made, works as of 7/7/98 (tested from Control Panel)

VOID MapMemUnload(IN PDRIVER OBJECT DriverObject)

Routine Description: Just delete the associated device & return.

Arguments:

DriverObject - pointer to a driver object

Return Value:

None

* /

{

WCHAR deviceLinkBuffer[] = L"\\DosDevices\\MAPMEM";

UNICODE STRING deviceLinkUnicodeString;

// Free any resources

//??????

// Delete the symbolic link

RtlInitUnicodeString (&deviceLinkUnicodeString,

deviceLinkBuffer);

IoDeleteSymbolicLink (&deviceLinkUnicodeString);

// Delete the device object

MapMemKdPrint (("MAPMEM.SYS: unloading\n"));

IoDeleteDevice (DriverObject->DeviceObject);

}

NTSTATUS MapMemMapTheMemory(IN PDEVICE_OBJECT DeviceObject,

IN OUT PVOID IoBuffer,

IN ULONG InputBufferLength,

IN ULONG OutputBufferLength)

/*

Routine Description:

Given a physical address, maps this address into a user

mode process's address space

Arguments:

DeviceObject

- pointer to a device object

IoBuffer

- pointer to the I/O buffer

InputBufferLength - input buffer length

OutputBufferLength - output buffer length

Return Value:

STATUS_SUCCESS if sucessful, otherwise

STATUS_UNSUCCESSFUL,

STATUS_INSUFFICIENT_RESOURCES,

(other STATUS_* as returned by kernel APIs)

```

Page 40 28th October, 1998

```

* /

//PPHYSICAL_MEMORY_INFO ppmi =

//

(PPHYSICAL_MEMORY_INFO) IoBuffer;

PMAPDEVREQUEST pmdr = (PMAPDEVREQUEST) IoBuffer;

INTERFACE TYPE

interfaceType;

ULONG

busNumber;

physicalAddress;

PHYSICAL_ADDRESS

length;

ULONG

UNICODE_STRING

physicalMemoryUnicodeString;

OBJECT_ATTRIBUTES objectAttributes;

HANDLE

physicalMemoryHandle = NULL;

PVOID

PhysicalMemorySection = NULL;

ULONG

inIoSpace, inIoSpace2;

NTSTATUS

ntStatus;

PHYSICAL ADDRESS physicalAddressBase;

PHYSICAL ADDRESS physicalAddressEnd;

PHYSICAL ADDRESS viewBase;

PHYSICAL_ADDRESS mappedLength;

BOOLEAN

translateBaseAddress;

translateEndAddress;

BOOLEAN

virtualAddress;

PVOID

if ( ( InputBufferLength < sizeof (MAPDEVREQUEST) ) | |</pre>

( OutputBufferLength < sizeof (PVOID) ) )

{

MapMemKdPrint (("MAPMEM.SYS: Insufficient input or output

buffer\n"));

ntStatus = STATUS INSUFFICIENT RESOURCES;

goto done;

interfaceType = 2; //EISA only

= 0; //MAY have to switch to 1 on Niestein!

busNumber

physicalAddress.HighPart= (LONG) 0x00000000;

physicalAddress.LowPart = (LONG) pmdr->mdr_PhysicalAddress;

inIoSpace = inIoSpace2 = 0;

length

= pmdr->mdr_SizeInBytes;

// Get a pointer to physical memory...

// - Create the name

// - Initialize the data to find the object

// - Open a handle to the oject and check the status

// - Get a pointer to the object

// - Free the handle

RtlInitUnicodeString (&physicalMemoryUnicodeString,

L"\\Device\\PhysicalMemory");

InitializeObjectAttributes (&objectAttributes,

&physicalMemoryUnicodeString,

OBJ_CASE_INSENSITIVE,

(HANDLE) NULL,

(PSECURITY_DESCRIPTOR) NULL);

ntStatus = ZwOpenSection (&physicalMemoryHandle,

SECTION_ALL_ACCESS,

&objectAttributes);

if (!NT_SUCCESS(ntStatus))

MapMemKdPrint (("MAPMEM.SYS: ZwOpenSection failed\n"));

goto done;

}

```

Page 41 28th October, 1998

```

ntStatus = ObReferenceObjectByHandle (physicalMemoryHandle,

SECTION_ALL_ACCESS,

(POBJECT_TYPE) NULL,

KernelMode,

&PhysicalMemorySection,

(POBJECT HANDLE INFORMATION) NULL);

if (!NT_SUCCESS(ntStatus))

MapMemKdPrint (("MAPMEM.SYS: ObReferenceObjectByHandle

failed\n"));

goto close_handle;

}

// Initialize the physical addresses that will be translated

physicalAddressEnd = RtlLargeIntegerAdd (physicalAddress,

RtlConvertUlongToLargeInteger(length));

// Translate the physical addresses.

translateBaseAddress = HalTranslateBusAddress

(interfaceType,

busNumber,

physical Address,

&inIoSpace,

&physicalAddressBase);

translateEndAddress = HalTranslateBusAddress

(interfaceType,

busNumber,

physicalAddressEnd,

&inIoSpace2,

&physicalAddressEnd);

if (!(translateBaseAddress && translateEndAddress))

MapMemKdPrint (("MAPMEM.SYS: HalTranslatephysicalAddress

failed\n"));

ntStatus = STATUS UNSUCCESSFUL;

goto close_handle;

// Calculate the length of the memory to be mapped

mappedLength = RtlLargeIntegerSubtract (physicalAddressEnd,

physicalAddressBase);

// If the mappedlength is zero, somthing very weird happened

// in the HAL since the Length was checked against zero.

if (mappedLength.LowPart == 0)

MapMemKdPrint (("MAPMEM.SYS: mappedLength.LowPart == 0\n"));

ntStatus = STATUS UNSUCCESSFUL;

goto close_handle;

length = mappedLength.LowPart;

// If the address is in io space, just return the address,

// otherwise go through the mapping mechanism

if (inIoSpace) // will never be called in our implementation

// since we never map I/O space!

{

```

Page 42 28th October, 1998

```

*((PVOID *) IoBuffer) = (PVOID) physicalAddressBase.LowPart;

else

// initialize view base that will receive the physical

// mapped address after the MapViewOfSection call.

viewBase = physicalAddressBase;

// Let ZwMapViewOfSection pick an address

virtualAddress = NULL;

// Map the section

ntStatus = ZwMapViewOfSection (physicalMemoryHandle,

(HANDLE) -1,

&virtualAddress,

0L,

length,

&viewBase,

&length,

ViewShare,

0,

PAGE READWRITE | PAGE NOCACHE);

if (!NT SUCCESS(ntStatus))

MapMemKdPrint (("MAPMEM.SYS: ZwMapViewOfSection

failed\n"));

goto close_handle;

// Mapping the section above rounded the physical address

// down to the nearest 64 K boundary. Now return a virtual

// address that sits where we want by adding in the offset

// from the beginning of the section.

(ULONG) virtualAddress +=

(ULONG) physicalAddressBase.LowPart -

(ULONG) viewBase.LowPart;

pmdr->mdr_LinearAddress = (ULONG *) virtualAddress;

//return the IoBuffer with the message structure in it:

*((PVOID *) IoBuffer) = virtualAddress;

ntStatus = STATUS_SUCCESS;

close_handle:

ZwClose (physicalMemoryHandle);

done:

return ntStatus;

The driver must have an associated registry entry file mapmem.reg, such as:

REGEDIT4

[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\MAPMEM]

"Type"=dword:0000001

"Start"=dword:0000003

"Group"="Extended base"

"ErrorControl"=dword:0000001

```

Page 43 28th October, 1998

### For further information see:

- 1. Microsoft Windows NT 4.0 Driver Developer Kit online help files.

- 2. Microsoft Win32 Software Developer Kit online help files.

- 3. "The Windows NT Kernel-Mode Device Driver Cook Book, featuring Visual C++" by Ruediger R. Asche, found on the MSDN Library CD Version January 1997

- 4. "Writing Windows NT Kernel-Mode Drivers in C++" by Ruediger R. Asche found on the MSDN Library CD Version January 1997

Page 44 28th October, 1998

### **Applications Software**

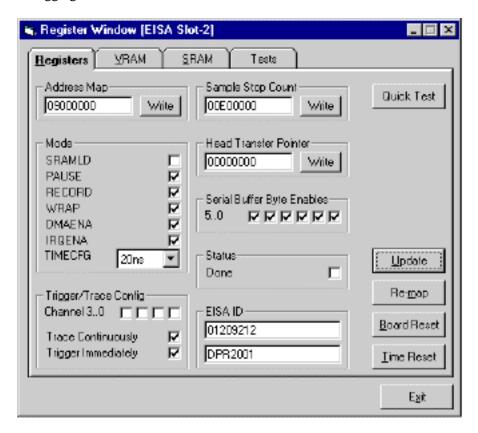

An example of a software application is described below. This is designed to present the following tracer control panel. This application demonstrates how to control the DT200.1 via a windowed graphical user interface (GUI) that calls the API functions described above, and is very useful for testing and debugging.

The design specifications allow the user to:

- (a) Read from and write to registers

- (b) Read from VRAM

- (c) Read from and write to SRAM

- (d) Perform various board test procedures (including repeated stress testing)

- (e) Save board configurations, test procedures and trigger information

- (f) Save the VRAM contents to a file

- (g) Analyse VRAM data to check board function ality and log results to a file

The interface consists of three main parts, a register window, a VRAM listing window and an SRAM listing window.

The register window displays the contents of all of the registers. The address map, stop count, head pointer and ID registers are displayed as test boxes containing hexadecimal data. The rest of the registers are displayed as check boxes indicating individual bit values. The time divisor is displayed in a drop down list with possible values of 20, 40, 80 and 160 ns.

In the VRAM listing window, the contents of a range of VRAM addresses can be displayed in a VRAM list box by entering the start and end addresses in text boxes and clicking on an Update

Page 45 28th October, 1998

button. For example, entering hexadecimal 0 in the From box and hexadecimal 1000 in the To box will display the contents of the VRAM from address 0 to 1000 in the list box, one longword per row.

The SRAM window works in the same way.

When the program is started the board is reset, the address map register is set to the default value and the Deep Trace memory is mapped to a linear address to make it accessible by the program.

The control panel shown above is actually produced by a stand-alone Visual Basic (Version 5.0) application. Visual Basic programs are comprised of many small files that make them difficult to describe. Consequently an equivalent Java program is presented below. This software generates nearly identical results.

### DT200.1 Control Panel Software using Java

This program, DTApp, is a stand-alone Java application with a user interface and the ability to control the DT200.1 Deep Trace Board through the <code>dt2001.dll</code> library. It is designed so that it can be used as a development platform for JNI (Java Native Interface) and JDBC (Java Database Connectivity).

At the top level the application consists of a Window with a card panel and a panel to control the cards. Each card consists of a number of panels implemented as separate classes. For example, there is a class for the Address Register panel. This allows the user interface code and the register control code to be kept in the same place. Thus by simply removing this class and the two lines which instantiate it, all address register functionality can be removed entirely from the application. This includes JNI code for the address register. This organization makes it easier to understand the code, as well as allowing the program to be changed very quickly.

At the uppermost level, the DTControlWindow class serves as a container for all of the other objects. It extends the Frame class to implement a window for the application. It also contains the main() entry point function for the application. A CardLayout manager is used to arrange the components (a panel for controlling the display of the cards and a panel for each card). There is no trace board functionality implemented at this level.

The ControlPanel class implements one of the cards contained in the DTControlWindow. It uses a GridBagLayout to arrange the DT200.1 register panels and a button bar. The ControlPanel handles events passed up from the button bar. This gives the button bar control of the registers.

There is a register panel class for each DT200.1 register. Each of these classes is able to make calls to the DLL functions which control the board using JNI. This means that each register panel exists as a component that can be removed and placed in new applications. It may be possible to alter these components to make their display optional. This would allow an application with higher level functionality to use the components but hide them from the user.

The DataPanel is a container for objects that deal with the trace data. The only such object at the moment is a DatabasePanel.

The DBControlPanel implements database connectivity using a JDBC-ODBC bridge. It has three member functions: a constructor, a function that stores a range of the Deep Trace VRAM in

Page 46 28th October, 1998

a database and a function that closes the database connection (see the section **Database Connectivity** for more information).

The ButtonPanel class implements the button bar used in the ControlPanel class. All of the button events are passed up to the parent class.

#### Java Native Interface (JNI)

The Java Native Interface (JNI) provides a method of using Java code together with native code (e.g. a DLL written in C++). It is possible to perform two-way communication between Java code and native code but here we are only interested in calling functions in the DT2001j.dll library<sup>1</sup>.

Native code libraries for use in Java Applications/Applets can be created by following a multi-step process:

1. Write the Java program. Declare any native methods in the classes where they are used. In a static code segment, make a call to the <code>loadLibrary()</code> function. This loads the native library into the Java class and maps the native method declaration to its implementation. For example<sup>2</sup>:

```

//

// AddressMapPanel

//

class AddressMapPanel extends Panel {

// [JNI] Native (DLL) method declaration

public native void setmap(int value);

public native int getmap();

static {

System.loadLibrary("DT2001J");

}

...

```

2. Compile the Java code written in the previous step:

```

> javac "DTControlWindow.java"

```

3. Create the header file for the native library. This will be used later to write the code for the native library. Use the javah program with the -jni argument:

```

> javah -jni "DTControlWindow.class"

```

If the Java source file contained more than one class with native declarations, then multiple header files will be produced, one for each class. To make life easier, all of the header files can be merged into one. To do this, take one of the header files and copy all of the function prototypes from the other files into this one, and then perhaps give it a name that makes more

Page 47 28th October, 1998

The DT2001j.dll library is a version of the DT2001.dll library with support for JNI. It allows the DT200.1 trace board to be controlled from the Java application. When this document was written, not all of the functionality implemented in DT2001.dll had been transferred to the JNI version (DT2001j.dll).

The loadLibrary() method appends (or prefixes) extensions to the library name in a system dependant way. For example, in a Windows95 environment, the entension .dll would be appended to DT2001j to give DT2001j.DLL. The user should not append this extension.

sense<sup>3</sup>. Make sure to leave the pre-processor instructions in the header file (the comment about not altering the file can be ignored!). The function prototypes can be altered later if required.

- 4. Write the native method implementation using the function prototypes created in Step 3. Remember to include the jni.h header file<sup>4</sup>.

- 5. Compile the native source code to create the shared library.

Java arrays and strings take a different format to arrays in C and C++. This means that arrays and strings passed from a Java program to a native method cannot be manipulated directly. The <code>jni.h</code> library includes some functions that allow native methods to use Java arrays and strings but this requires some extra code to be written. Refer to the Sun documentation on JNI.

#### **Database Connectivity**

JDBC<sup>5</sup> provides a standard API for the development of database applications in Java. A single Java application written using JDBC can be used to control different types of database, e.g. Sybase, Oracle, etc..

To use JDBC, a DBMS driver is required for each type of database accessed from the program. For the purposes of the DT200.1 Java application, a JDBC-ODBC bridge (category 1 driver) is used. This driver is distributed with the JDBC package from Sun. To set up basic database connectivity on a local machine:

- 1. Load the JDBC-ODBC bridge driver.

- 2. Find the driver to process the URL.

- 3. Create a property list with the information required to connect to the database.

- 4. Connect to the driver.

- 5. Execute the SQL query.

The following code segment illustrates the above procedure:

```

//

// Simple Database Connectivity

//

// Instantiate this class from another method

//

class DBControl {

String url; // Store the URL provided

Connection con;

public DBControl(String DBName) {

url = DBName;

```

Page 48 28th October, 1998

<sup>&</sup>lt;sup>3</sup> Try to avoid underscore characters when naming native methods in the Java code. The javah program creates new names by prefixing some information to the identifier and using underscores. If underscores are also used in the original method declaration, the native function names will become harder to follow.

The path containing the jni.h header file may need to be added to the include path of the compiler used to compile the .dll file.

Microsoft Visual J++ does not support JNI. As a result of this, there is also no support for JDBC. JDBC is the Sun API that gives Java Applications/Applets database functionality.

```

try {

// Load the JDBC-ODBC bridge driver

Class.forName("sun.jdbc.odbc.JdbcOdbcDriver");

// Find the driver to process the URL

Driver jdbcDriver = DriverManager.getDriver(url);

// Create and set up the property list with the

// correct security information

Properties propertyList = new Properties();

propertyList.put("user", "dtuser");

propertyList.put("password", "dtpassword");

// This can be used to provide verbose logging

DriverManager.setLogStream(System.out);

// Connect to the driver

con = DriverManager.getConnection(url, propertyList);

catch (SQLException ex) {

System.out.println("Exception while trying to connect");

while (ex != null) {

// The following information is essential for

// finding errors

System.out.println("SQLState: " + ex.getSQLState());

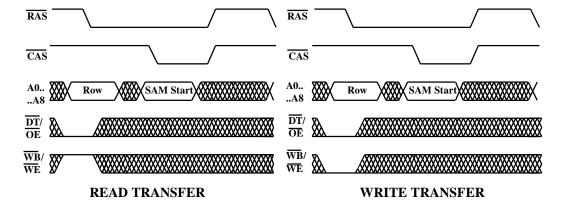

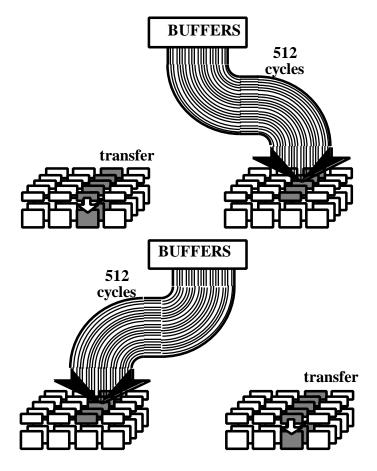

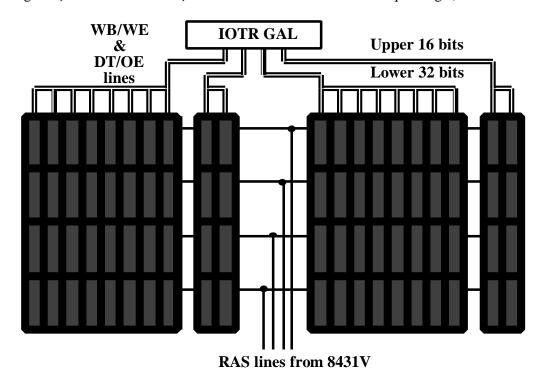

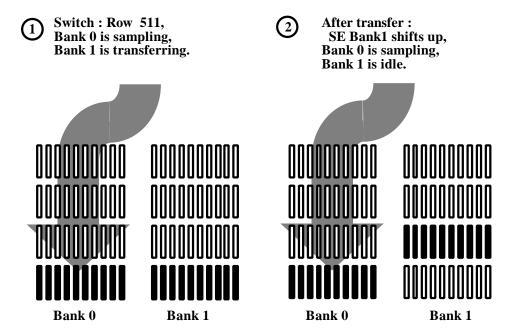

System.out.println("Message: " + ex.getMessage());